密级: \_\_\_\_

# 硕士学位论文

## 高性能波导集成型 PIN 光电探测器的研究

| 作者姓名: | 刘道群            |  |

|-------|----------------|--|

| 指导教师: | 李志华 研究员        |  |

|       | 中国科学院大学 微电子研究所 |  |

| 学位类别: | 工程硕士           |  |

| 学科专业: | 集成电路工程         |  |

| 培养单位: | 中国科学院大学 微电子研究所 |  |

2018年6月

## 硕士学位论文

## 高性能波导集成型 PIN 光电探测器的研究

| 作者姓名: | 刘道群            |

|-------|----------------|

| 指导教师: | 李志华 研究员        |

|       | 中国科学院大学 微电子研究所 |

| 学位类别: | 工程硕士           |

| 学科专业: | 集成电路工程         |

| 培养单位: | 中国科学院大学 微电子研究所 |

2018年6月

# The Study of High-Performance Waveguide-Integrated PIN Photodetector

A thesis submitted to

University of Chinese Academy of Sciences

in partial fulfillment of the requirement

for the degree of

Master of Engineering

in IC Engineering

By

Daoqun Liu

Supervisor: Professor Zhihua Li

Institute of Microelectronics of Chinese Academy of

Science

June 2018

## 中国科学院大学 研究生学位论文原创性声明

本人郑重声明: 所呈交的学位论文是本人在导师的指导下独立进行研究工作 所取得的成果。尽我所知,除文中已经注明引用的内容外,本论文不包含任何其 他个人或集体已经发表或撰写过的研究成果。对论文所涉及的研究工作做出贡献 的其他个人和集体,均已在文中以明确方式标明或致谢。

作者签名: 刘道祥 日期: 2018年5月7日

## 中国科学院大学 学位论文授权使用声明

本人完全了解并同意遵守中国科学院有关保存和使用学位论文的规定,即中国科学院有权保留送交学位论文的副本,允许该论文被查阅,可以按照学术研究公开原则和保护知识产权的原则公布该论文的全部或部分内容,可以采用影印、缩印或其他复制手段保存、汇编本学位论文。

涉密及延迟公开的学位论文在解密或延迟期后适用本声明。

作者签名: 刘道辞 导师签名: 龙龙子 日 期: 2018年5月21日 日 期: 2018年5月21日

#### 摘要

光电探测器作为光电子集成电路(Optoelectronic Integrated Circuit, OEIC)中一种不可或缺的元件,能够完成光通信与光互连系统中的光电转换功能,实现数据从光域到电域的转换。虽然基于 III-V 材料体系的光电探测器具有优异的性能并且已经实现商业化,然而高昂的制造成本以及无法与 CMOS 工艺兼容限制了其应用领域以及阻碍了其发展的速度。因而,开发一种性能与 III-V 光电探测器相当且具有 CMOS 兼容性的光电探测器成为了业界关注的焦点。锗(Germanium, Ge)作为一种准直接带隙材料,不仅在1.3µm – 1.5µm的波长范围内具有很高的光吸收系数同时其制备工艺与 CMOS 兼容,这使得 Ge 成为研究近红外光电探测器的首选材料。传统的垂直面入射 Ge 光电探测器由于光子吸收方向与光生载流子输运方向平行使得探测器的光响应度与带宽之间相互制约,然而光波导与探测器的集成使得制备兼具高响应度与高带宽的探测器成为可能。此外,由于 PIN 光电探测器相对于其他电学结构的探测器具有工艺相对简单,量子效率高及暗电流低等优点,波导集成型硅基 PIN Ge 光电探测器业已成为业界研究的主流。

本文开展了对波导集成型硅基 PIN Ge 光电探测器的研究。基于波导集成型 光电探测器的基本工作原理,首先设计了具有垂直 PIN 结构的波导集成型光电 探测器,其次基于优化的工艺流程完成了光电探测器的制备,最后对探测器进行 了结构表征与性能测试并详细分析了探测器结构参数与工艺参数对探测器性能 参数的影响。本论文的主要研究成果如下:

1.光电探测器的结构设计:设计了不同尺寸波导集成型垂直 PIN 光电探测器,探测器的有源区的长度为15μm,宽度以1μm为间隔从1μm增加到5μm。为了降低对制备工艺的要求,波导探测器的光耦合方式采用了倏逝波耦合;此外,为了降低光纤到光波导耦合时对对准精度的要求,采用了聚焦耦合光栅,这同时提高了光纤到光波导的光耦合效率。

2.光电探测器的制备: 首先通过标准的 CMOS 工艺完成了聚焦耦合光栅以及光波导的制备; 其次采用了选择性外延生长(Selective Epitaxial Growth, SEG) 技

术并利用减压化学气相沉积(Reduced Pressure Chemical Vapor Deposition,RPCVD)设备在图形衬底上生长出了高质量的锗膜;最后通过标准的 CMOS 金属化工艺完成了波导集成型 PIN Ge 光电探测器的制备。

3.光电探测器表征与测试:通过对探测器暗电流、光响应度以及频率响应的测试表明在-1V 的反偏压下,15μm×1μm光电探测器的暗电流低至 7nA:15μm×4μm探测器在-2V 偏压下,暗电流为 169nA,1530nm 波长处探测器的光响应度约为 0.43A/W,3-dB 带宽高达 47GHz 并且获得了速率高达 40Gbps 的清晰眼图。

关键词: 波导集成,光电探测器,PIN结,CMOS兼容

#### Abstract

As an integral part of OEIC (Optoelectronic Integrated Circuit), photodetectors can complete the photoelectric conversion function in optical communication and optical interconnection systems, and realize the conversion of data from the optical domain to the electrical domain. Although photodetectors based on III-V material systems have excellent performance and have been commercialized, high manufacturing costs and incompatibility with CMOS processes have limited their application area and hindered their development. Therefore, the development of a photodetector with performance comparable to III-V photodetectors and CMOS compatibility has become the focus of attention in the industry. Ge (Germanium) as a quasi-direct bandgap material not only has a high light absorption coefficient in the wavelength range of 1.3 µm-1.5 µm, but also has the compatibility with CMOS technnoloby, which makes Ge a preferred candidate for near infrared photo-detection. There is a trade-off between the reponsivity and 3-dB bandwith for traditional vertical surface incident Ge photodetector due to the fact that the direction of photons aborsption and that of photo-carrier transport is parallel. However, it is possible to fabricate high-speed photodetector with high responisivity by integrating the photodetector with the optical waveguide. In addition, comparing with the photodetector with other type electric structure, the PIN photodetector has advantages including lower fabricating complexity, higher responsivity and lower dark current. Therefore, the wavegude-integrated silicon-based PIN Ge photodetector has become the mainstream in industry.

In this paper, the waveguide-integrated silicon-based PIN Ge photodetectors were studied. Based on the basic principle of the waveguide-integrated photodetectors, firstly, waveguide-integrated photodetectors with a vertical PIN structure were designed, then the photodetectors were fabricated by an optimized process, finally the structure characterization and testings were conducted followed by a series analyses which focus on figuring the effects on the photodetector performance caused by variations from fabrication process and structure design. The main research results of this paper are as

follows:

- 1. Structure design of the photodetector: Waveguide-integrated Ge photodetectors with vertical PIN structures of different sizes were designed. The length of the active region of the detector is  $15 \, \mu m$ , and the width is increased from  $1 \, \mu m$  to  $5 \, \mu m$  at intervals of  $1 \, \mu m$ . In order to reduce the requirements of the fabrication process, the coupling of light from the waveguide to the detector employs evanescent-wave coupling; in addition, in order to reduce the requirement for the alignment accuracy when the light is coupled from the fiber to the optical waveguide, a focus coupling grating is used, which at the same time improves optical coupling efficiency.

- 2. Fabrication of the photodetector: Firstly, the fabrication of the focus-coupled grating and the optical waveguide was completed through the standard CMOS process; secondly, high quality germanium film was grown by the SEG (Selective Epitaxial Growth) technique through RPCVD (Reduced Pressure Chemical Vapor Deposition) equipment. Finally, the standard metallization process compatible with CMOS techneque was adopted to finish the fabrication of the waveguide-integrated PIN Ge photodetector.

- 3. Characterization and testing of the photodetector: The results from the dark-current testing, responsivity testing and frequency response tesing indicated that under a reverse bias of -1 V, the dark current of the  $15\mu m \times 1\mu m$  photodetector is as low as 7nA; as for the photodetector has size of  $15\mu m \times 4\mu m$ , under -2V reverse bias, the dark current is as low as 169nA, the responsivity is 0.43A/W at 1530nm wavelength, the 3-dB bandwidth is as high as 47GHz and a clear eye-diagram at 40Gbps is obtainable.

**Key Words:** Waveguid Integration, Photodetector, PIN Junction, Compatibility with CMOS

## 目 录

| 摘  |     | 要                        | . I |

|----|-----|--------------------------|-----|

| ΑĒ | BS' | TRACTI                   | II  |

| 目  | ;   | 录                        | V   |

| 图: | 表   | 目录V                      | II  |

| 第  | 1   | 章 绪论                     | . 1 |

| 1  | .1  | 引言                       | . 1 |

| 1  | . 2 | 波导集成型光电探测器的研究进展          | .4  |

| 1  | .3  | 本文的主要研究内容及组织结构           | 12  |

| 第  | 2   | 章 PIN 光电探测器的基本工作原理1      | 4   |

| 2  | .1  | 波导集成型 PIN 光电探测器的分类       | 4   |

| 2  | 2.2 | 光电探测器的基本工作原理             | 17  |

|    | 2   | .2.1 PN 结光电探测器的工作原理1     | 7   |

|    | 2   | .2.2 PIN 结光电探测器的工作原理1    | 8   |

| 2  | 3   | 光电探测器的主要性能参数2            | 20  |

|    | 2   | .3.1 暗电流                 | :0  |

|    | 2   | .3.2 光响应度2               | :1  |

|    | 2   | .3.3 3-dB 带宽2            | 2   |

| 2  | .4  | 小结2                      | 23  |

| 第  | 3   | 章 波导集成型 PIN GE 光电探测器的制备2 | :5  |

| 3  | .1  | 引言2                      | 25  |

| 3  | .2  | 波导集成型光电探测器的制备2           | 27  |

|    | 3   | .2.1 衬底的选择与处理2           | :7  |

|    | 3   | .2.2 Poly-Si Taper 的制备3  | 0   |

|    | 3   | .2.3 光波导与光栅的制备           | 0   |

#### 高性能波导集成型 PIN 光电探测器的研究

| 3.2.4 锗的选择性外延    | 33          |

|------------------|-------------|

| 3.2.5 器件的金属化     | 38          |

| 3.3 小结           | 40          |

| 第 4 章 光电探测器的结构表征 | 与性能测试41     |

| 4.1 引言           | 41          |

| 4.2 探测器的结构表征     | 41          |

| 4.3 波导及光栅的光学损耗   | 50          |

| 4.4 探测器的光电性能测试   | 53          |

| 4.4.1 暗电流        | 53          |

| 4.4.2 光响应度       | 56          |

| 4.4.3 3-dB 带宽及眼图 | 58          |

| 4.5 小结           | 61          |

| 第 5 章 总结与展望      | 62          |

| 5.1 本文工作的总结      | 62          |

| 5.2 展望           | 63          |

| 参考文献             | 67          |

| 致 谢              | 71          |

| 作者简历及攻读学位期间发表的   | 学术论文与研究成果72 |

### 图表目录

| 图       | 1.1 存储器与微处理器所遵循的摩尔定律1                                                                                                                                                                                                                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 图       | 1.2 各种半导体体材料的光吸收系数                                                                                                                                                                                                                              |

| 图       | 1.3 垂直面入射光电探测器结构3                                                                                                                                                                                                                               |

| 图       | 1.4 波导集成型光电探测器示意图4                                                                                                                                                                                                                              |

| 图       | 1.5 1984 年 Luyri 等人制备的光电探测器结构示意图5                                                                                                                                                                                                               |

| 图       | 1.6 1998 年 Samavedam S. B.等人制备的光电探测器结构6                                                                                                                                                                                                         |

| 图       | 1.7 2004 年 Dosumma O.I.等人制备的谐振腔光电探测器6                                                                                                                                                                                                           |

| 表       | 1.1 近十年垂直面入 PIN Ge 光电探测器的主要性能参数7                                                                                                                                                                                                                |

| 图       | 1. 8 1974 年 Stillman G. E.制备的波导集成型In <sub>x</sub> Ga <sub>1-x</sub> As/Pt肖特基结光电探                                                                                                                                                                |

| 测:      | 器结构7                                                                                                                                                                                                                                            |

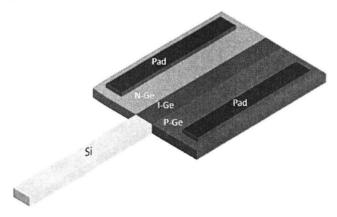

| 图       | 1.9 首例波导集成型 PIN Ge 光电探测器结构8                                                                                                                                                                                                                     |

| 图       | 1.10 2006 Liu J. F.等人制备的高性能波导集成型 PIN Ge 光电探测器8                                                                                                                                                                                                  |

| 图       | 1.11 2011 年 Derose C.T.等人制备的超紧凑型波导集成型 PIN Ge 光电探测器                                                                                                                                                                                              |

|         |                                                                                                                                                                                                                                                 |

|         | 9                                                                                                                                                                                                                                               |

| 图       | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测                                                                                                                                                                                            |

| 图       |                                                                                                                                                                                                                                                 |

| 图 器.    | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测                                                                                                                                                                                            |

| 图 器.    | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测                                                                                                                                                                                            |

| 图器图表    | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测         1. 12 2016 年 Chen H.等人制备的高性能波导集成型 PIN Ge 光电探测器10                                                                                                                                   |

| 图器图表    | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测 10 1.13 2016 年 Chen H.等人制备的高性能波导集成型 PIN Ge 光电探测器 10 1.2 近十年波导集成型 PIN Ge 光电探测器的研究进展 11 2.1 对接耦合波导集成型 PIN 光电探测器                                                                              |

| 图器图表图图  | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测 10 1.13 2016 年 Chen H.等人制备的高性能波导集成型 PIN Ge 光电探测器 10 1.2 近十年波导集成型 PIN Ge 光电探测器的研究进展 11 2.1 对接耦合波导集成型 PIN 光电探测器 15                                                                           |

| 图器图表图图图 | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测 10 1.13 2016 年 Chen H.等人制备的高性能波导集成型 PIN Ge 光电探测器 10 1.2 近十年波导集成型 PIN Ge 光电探测器的研究进展 11 2.1 对接耦合波导集成型 PIN 光电探测器 15 2.2 倏逝耦合波导集成型 PIN 光电探测器 15                                                |

|         | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测 10 1.13 2016 年 Chen H.等人制备的高性能波导集成型 PIN Ge 光电探测器 10 1.2 近十年波导集成型 PIN Ge 光电探测器的研究进展 11 2.1 对接耦合波导集成型 PIN 光电探测器 15 2.2 倏逝耦合波导集成型 PIN 光电探测器 15 2.3 波导集成型水平 PIN Ge 光电探测器结构 16                  |

|         | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测 10 1.13 2016 年 Chen H.等人制备的高性能波导集成型 PIN Ge 光电探测器 10 1.2 近十年波导集成型 PIN Ge 光电探测器的研究进展 11 2.1 对接耦合波导集成型 PIN 光电探测器 15 2.2 倏逝耦合波导集成型 PIN 光电探测器 15 2.3 波导集成型水平 PIN Ge 光电探测器结构 16 2.4 PN 结光电探测器 18 |

|         | 1. 12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测 10 1.13 2016 年 Chen H.等人制备的高性能波导集成型 PIN Ge 光电探测器                                                                                                                                           |

| 图 | 3.2 本文制备的波导集成型垂直 PIN 光电探测器          | .26 |

|---|-------------------------------------|-----|

| 图 | 3.3 本文制备的波导集成型垂直 PIN 结构 Ge 光电探测器版图  | .26 |

| 表 | 3.1 本文制备的波导集成型 PIN Ge 光电探测器版图信息     | .27 |

| 图 | 3.4 本文研究的波导集成型 PIN Ge 光电探测器的制备工艺流程  | .28 |

| 图 | 3.5 本文制备探测器所采用的 SOI 衬底              | .29 |

| 图 | 3.6 基于 SOI 衬底的硅光波导截面示意图             | .29 |

| 图 | 3.7 波导模式有效折射率随波导芯层厚度的变化关系           | .30 |

| 图 | 3.8 Poly-Si Taper 结构对应的版图           | .30 |

| 图 | 3.9 本文制备的波导集成型探测器中集成的波导             | .31 |

| 图 | 3.10 聚焦光栅版图                         | .32 |

| 图 | 3.11 PIN 光电探测器的 N 型区(离子注入)版图 NS     | .32 |

| 图 | 3.12 Si 上欧姆接触重掺杂区对应版图 NSS           | .32 |

| 图 | 3.13 Ge 外延的位错密度对比图                  | .34 |

| 图 | 3.14 外延窗口定义所对应的版图 Ge                | .35 |

| 图 | 3.15 外延 Ge 顶部与外延窗口结合处出现未完全填充现象      | .36 |

| 图 | 3.16 Ge 形貌(截面 SEM 图)对比              | .37 |

| 图 | 3.17 Ge 层 P 型注入所对应的版图 GP            | .38 |

| 图 | 3-18 Ge 与 Si 接触孔对应版图 GCA、CA         | 38  |

| 图 | 3.19 探测器的金属电极形成对应版图 M1 与 PD         | .39 |

| 图 | 3.20 探测器通光孔对应版图 LT                  | .39 |

| 图 | 3.21 本文所制备的波导集成型 PIN Ge 光电探测器光学显微图  | .40 |

| 图 | 4.1 本文制备的波导集成型 PIN Ge 光电探测器截面 SEM 图 | .42 |

| 图 | 4.2 Poly-Si Taper 版图                | .43 |

| 图 | 4.3 Poly-Si Taper 表面 SEM 图          | .43 |

| 图 | 4.4 PY 版测试区图形                       | .43 |

| 图 | <b>4.5</b> SOI 晶圆上不同位置处波导截面 SEM 图   | .44 |

| 图 | 4.6 聚焦光栅版图                          | 44  |

| 刚 | 47 聚佳光栅形貌图                          | 45  |

| <b>图</b> | 4.8 晶圆片中心与边缘位置处不同宽度的外延窗口形貌                         | 46 |

|----------|----------------------------------------------------|----|

| 图        | 4.9 Ge 外延前清洗不彻底导致的外延失败案例                           | 47 |

| 图        | 4.10 晶圆上不同位置外延窗口清洗后的表面 SEM 图                       | 47 |

| 图        | <b>4.11</b> 15μm×3μm窗口外延 Ge 形貌                     | 48 |

| 图        | <b>4.12</b> 15μm × 2μm窗口外延 Ge 的 TEM 图              | 48 |

| 图        | 4.13 窗口中 Ge CMP 后形貌图                               | 49 |

| 图        | 4.14 Ge 被氧化性溶液腐蚀后的器件截面 SEM 图                       | 50 |

| 图        | 4.15 波导传输损耗与光栅耦合损耗测试结构版图                           | 51 |

| 图        | 4. 16 光谱仪 YOKOGAWA AQ6370D                         | 51 |

| 图        | 4.17 可调谐激光器 YOKOGAWA AQ2200-136                    | 51 |

| 图        | 4.18 四维探针台                                         | 52 |

| 表        | 4.1 不同长度波导的总损耗                                     | 52 |

| 图        | 4.19 波导总损耗随波导长度的变化曲线                               | 53 |

| 图        | 4.20 不同尺寸探测器暗电流特性曲线                                | 54 |

| 表        | 4.2 典型偏压下不同尺寸探测器的暗电流                               | 54 |

| 图        | 4.21 IMEC 波导集成型 PIN Ge 光电探测器暗电流特性                  | 55 |

| 图        | 4.22 典型偏压下探测器暗电流随 Ge 区宽度的变化曲线                      | 55 |

| 图        | 4.23 探测器光响应度测试原理框图                                 | 56 |

| 表        | 4.3 不同尺寸探测器的光响应度(@-2V@1530nm)                      | 57 |

| 图        | 4.24 探测器响应度随 Ge 宽度的变化趋势(@-2V@1530nm)               | 57 |

| 图        | 4.25 探测器 S 参数矩阵测试原理框图                              | 58 |

| 图        | 4.26 探测器的s <sub>21</sub> 参数随频率的变化关系曲线(@-2V@1530nm) | 59 |

| 图        | 4.27 探测器眼图测试原理框图(@-2V@1530nm)                      | 60 |

| 图        | <b>4.28</b> 15μm×3μm探测器眼图(@-2V@1530nm)             | 60 |

|          | <b>4.29</b> 15μm × 4μm探测器眼图(@-2V@1530nm)           |    |

#### 第1章 绪论

#### 1.1 引言

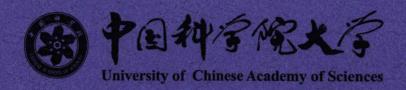

从 1947 年第一个点接触式锗晶体管的发明<sup>[1]</sup> 到 1960 年第一块基于平面工艺的集成电路芯片的诞生<sup>[2]</sup> 到今天的利用 22nm 互补金属-氧化物-半导体(Complementary Metal-Oxide-Semiconductor,CMOS)工艺在不到200 mm<sup>2</sup>面积上集成有超过十亿个晶体管 Intel CPU<sup>[3]</sup>,集成电路的发展基本上遵循着摩尔定律<sup>[4]</sup>所预测的时间路线图,如图 1-1 所示。尽管推动集成电路向着更快、超低功耗以及更低成本方向发展的市场驱动力日趋强盛,但是 CMOS 器件的物理尺寸

图 1.1 存储器与微处理器所遵循的摩尔定律[4]

限以及日益攀升的功率密度所引发的诸如芯片散热及可靠性问题制约着集成电路向前发展的速度。在后摩尔时代,人们一直致力于探索与开发能够克服上述挑战并能够在未来替代传统 CMOS 器件的新技术与器件以应对摩尔定律终结所带来的威胁。OEIC 作为极具发展潜力的可选项应运而生。

OEIC 芯片相对于传统的 IC 芯片而言具有诸多的优势,如数据传输速率更高、抗干扰性更强、功耗更低及保密性更强等。目前,OEIC 芯片的实现的工艺平台主要有两种,一种基于 III-V 族工艺而另外一种则依赖于目前十分成熟的 CMOS 平台。III-V 材料如 InP、GaAs 等多为直接带隙半导体且其具有很高的载

流子迁移率;最早的 OEIC 芯片是基于 III-V 材料的,其发展至今工艺已相当成熟,许多高性能的基于 III-V 材料的光子学无源器件<sup>[5]</sup> 及有源器件如调制器<sup>[6]</sup> 、激光器<sup>[7]</sup> 及探测器<sup>[8]</sup> 已经被开发出来且已经实现商用化。然而,由于 III-V 材料难以提纯且难以制备大尺寸(目前还没有 8 英寸的 III-V 工艺线)的晶圆,所以基于 III-V 材料衬底的 OEIC 芯片制造成本昂贵且产能不足。基于 CMOS 工艺的硅基 OEIC 芯片具有工艺成熟稳定且价格低廉等特点,然而,由于 Si 材料无法实现高效率发光,这使得光源问题成为发展 OEIC 芯片的一个最大障碍;此外由于 Si 光吸收截止波长约为1.1μm,所以 Si 对于近红外光通信波段的光是透明的,这使得全硅探测器无法应用于1.3 — 1.6μm的光通信波段。

目前,解决硅基 OEIC 芯片探测器集成的方案有两种,分别是基于封装键合技术的混合集成和基于异质外延技术的单片集成。前者利用键合技术将成熟的III-V 光源芯片与 Si 基 OEIC 芯片及其他 IC 芯片封装在一个基体内形成功能完整的 OEIC 芯片,然而由于这需要解决不同材料电学、光学及热学性能差异所引入的可靠性问题,同时由于键合引入的各种寄生参数也不能忽略,所以混合集成技术通常成本高昂,成品率低且可靠性不佳。基于异质外延的单片集成方案则通过直接在硅基(Si 或 SOI 衬底)上直接生长异质材料(如 III-V 材料、Ge 等)实现,由于衬底统一且 CMOS 工艺技术成熟先进,因此单片集成方案具有成本低、可靠性高等优点。然而,硅基异质外延面临的最大挑战是由于材料晶格常数差异造成的晶格失配以及材料热膨胀系数差异导致的热性能失配,这都严重制约着材料的生长质量。

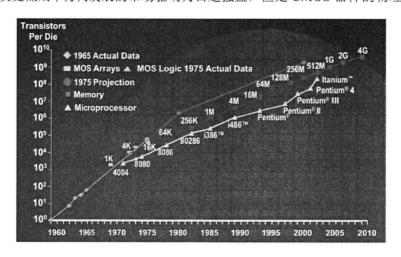

尽管大多数 III-V 材料以及 Ge 在近红外波段都有较高的光吸收系数,如下图 1-2<sup>[9]</sup> 所示。然而,除了晶格失配与热性能失配外,可能造成 CMOS 工艺线掺杂污染(III-V 材料通常可作为 Si 材料的掺杂杂质)也是 III-V 材料难以与 Si 实现高质量异质集成的一个重要原因。所以 Ge 与 Si 的单片异质集成是目前的主流方案。尽管 Ge 与 Si 之间存在高达 4.2%的晶格失配,但是诸如低-高温两步生长、可变 Ge 组分的缓冲层生长、选择性外延以及上述方法的有机组合都能有效地减少 Ge 外延层中穿透位错密度(Treading Dislocation Density, TDD),从而使材料到达制备器件的要求。

图 1.2 各种半导体体材料的光吸收系数[9]

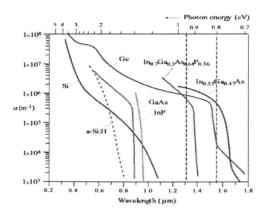

早期的 Si 基 Ge 光电探测器多为垂直面入射式光电探测器,即光是通过探测器顶部或底部的通光窗口垂直进入探测器,如图 1.3 所示。从图 1.3 可以看出,光垂直于探测器顶部的通光窗口入射进入探测器的本征 Ge 层中并被吸收,产生的光生载流子(电子-空穴对)在外加电场的作用下分别向探测器的 P 端、N 端运动并被电极收集最终在外电路形成光电流。由于光的入射吸收方向与载流子的输运方向平行,想要在不影响探测器频率响应的情况下通过增加 Ge 层厚度从而提高探测器的量子效率是不可能的。因而垂直面入射光电探测器的光响应度与频率响应间存在相互制约的关系,这是使其应用范围受到很大限制。

图 1.3 垂直面入射光电探测器结构

为了克服垂直面入射探测器的上述缺点,即使得探测器的光入射吸收方向与 光生载流子的输运方向解耦合,光波导被巧妙地应用到这一问题的解决中。利用 光波导的对光的导引特性,波导集成型光电探测器中光吸收与光生载流子的输运 的路径方向相互垂直且二者互不影响,如图 1.4 所示。波导集成型探测器中光吸收方向为探测器有源区的长度方向,而载流子的输运方向则为探测器有源区的厚度方向;可通过分别优化探测器有源区的长度与厚度设计并制备出兼具 3-dB 带宽大、光响应度高的光电探测器。

图 1.4 波导集成型光电探测器示意图

#### 1.2 波导集成型光电探测器的研究进展

探测器的分类方法主要有两种,一种是按照其电学结构进行分类,光电探测器可分为 PN 结光电探测器、PIN 结光电探测器、雪崩击穿光电探测器(Avalanche Photodetector, APD )及金属-半导体-金属(Metal-Semiconductor-Metal, MSM)光电探测器等;一种是按照其光学结构进行分类,可分为垂直面入射光电探测器(如图 1.3)与波导集成光电探测器(如图 1.4 所示)。值得注意的是,上述两种分类方法并不是相互独立的,即根据实际的应用需求将不同的光学结构与电学结构进行组合即设计出不同结构的光电探测器。此外,还可以按照光电探测器有源区材料(光吸收材料)的种类以及适用的波长范围对探测器进行分类。

本部分在简要回顾垂直面入射 PIN Ge 光电探测器的发展现状的基础上,重点介绍波导集成 PIN Ge 光电探测器的研究进展及现状。

#### 1.2.1 垂直面入射 PIN Ge 光电探测器

早期的 PIN Ge 光电探测器的光学结构都是垂直面入射的,这是因为垂直面入射结构的探测器结构较为简单,加工工艺也相对简单;此外由于垂直面入射结构的探测器多采用台面或者双台面结构,结构尺寸都在几微米至几十微米量级,与之同时代的光刻与刻蚀等工艺完全能够满足其对于加工精度的要求。

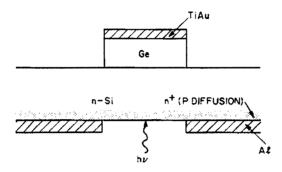

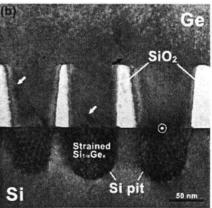

最早的 PIN Ge 光电探测器可以追溯到 1984 年,Serge Luryi<sup>[10]</sup> 所在的研究 小组利用分子束外延法(MBE)法,首先在  $n^+$  Si 层上外延一层 1800Å 厚的 Ge 组分 x 从 0%增加值 100%的 $Ge_xSi_{1-x}$ 缓冲层,而后依次外延1.25 $\mu$ m厚的原位掺杂  $n^+$  Ge 层、2.0 $\mu$ m厚的本征 Ge 层及 2500Å 厚的  $p^+$  Ge 层,利用此多层膜结构制备的探测器,如图 1.5 所示,在 1450 $\mu$ m 波长处的量子效率约为 41%(对应的光响应度约为0.48 A/W),然而其暗电流密度却高达50  $\mu$ mA/cm²。

图 1.5 1984 年 Luyri 等人制备的光电探测器结构示意图[14]

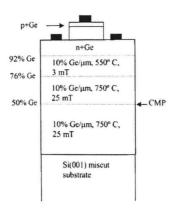

在此后的十多年里,由于 Ge 材料外延生长技术的发展缓慢,PIN Ge 探测器的性能也几乎停滞不前。直到 1998 年,来自 MIT 的 Samavedam S. B<sup>[11]</sup> 等人利用通过 CMP 工艺优化处理的Ge<sub>x</sub>Si<sub>1-x</sub>缓冲层技术,外延生长出高质量的本征 Ge 层,并由此制得暗电流密度很低的 PIN Ge 光电探测器,如图 1.6 所示。该探测器在-1V 反偏压下的暗电流密度低至0.15 mA/cm²,这表明本征 Ge 层的高质量特性; 然而其在 1330nm 波长处的量子效率仅有 12.6%,理论 3-dB 带宽达吉赫兹量级。

在之后的发展过程中,研究人员一方面通过利用日趋成熟的材料外延生长技术来改善 Ge 材料的外延生长质量以降低探测器的暗电流密度,利用一方面则是通过优化探测器的结构设计以改善探测器的光电响应特性以及频率响应特性。

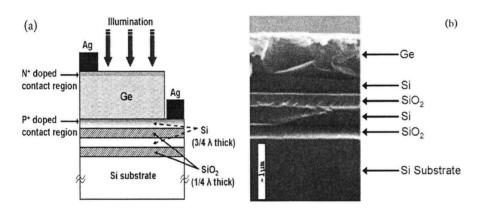

2004年,来自波士顿大学的 Dosunmu O. I.与 MIT 的研究人员<sup>[12]</sup> 合作开发了一种居于双 SOI 衬底的 PIN Ge 光电探测器,如图 1.7 所示。利用谐振腔(RCE)带来的光吸收增强效应,在-IV 反偏压下,在 1550nm 波长处其量子效率高达 76%,暗电流密度也仅约为276 mA/cm<sup>2</sup>,理论 3-dB 带宽高达 25GHz。

图 1.6 1998 年 Samavedam S. B. 等人制备的光电探测器结构[11]

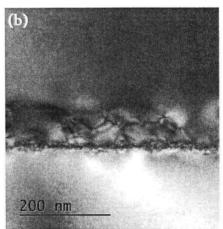

图 1.7 2004 年 Dosumma O.I.等人制备的谐振腔光电探测器<sup>[12]</sup>(a)探测器截面结构示意图(b) 探测器的截面 SEM 图

2009 年,Dongwoo<sup>[13]</sup> 等人利用 RPCVD 技术外延生长出高质量的 Ge 膜并利用 p 型多晶硅(Poly-Si)对 Ge 表面进行钝化处理。在-1V 反偏压下,探测器的暗电流密度低至4.63 mA/cm<sup>2</sup>;在 1550nm 波长处,探测器的响应度为0.47 A/W;3-dB 带宽高达数十吉赫兹。

随着材料外延生长技术的不断进步,Ge 的外延生长质量不断提升,器件的暗电流密度也在逐步下降,从早期的几十mA/cm²量级下降至小于10 mA/cm²;器件的响应度主要取决于本征 Ge 层的厚度,而 3-dB 带宽也受其制约,所以垂直面入射的 PIN Ge 光电探测器的响应度与 3-dB 带宽要根据实际的应用需求进行折中优化。表 1.1 给出了近十年来垂直面入射 PIN Ge 探测器主要性能参数。

| 年份   | 器件台面   | 暗电流  | 响应度(A/W) | 3-dB 带宽(GHz) | 参考文献 |

|------|--------|------|----------|--------------|------|

|      | 直径(μm) | (nA) | @1550nm  | @1550nm      |      |

| 2008 | 20     | 30   | 0.47     | 18.9         | [14] |

| 2009 | 25     | 13.9 | 0.32     | 12.04        | [15] |

| 2010 | 50     | 1μΑ  | 0.23     | -            | [16] |

| 2011 | 60     | 30μΑ | 0.37     | -            | [17] |

| 2013 | 20     | 52   | 0.68     | 25.2         | [18] |

| 2015 | 60     | 341  | 0.84     | 13.4@-3V     | [19] |

| 2017 | 12     | 50   | 0.27@0V  | 38@-1V       | [20] |

表 1.1 近十年垂直面入 PIN Ge 光电探测器的主要性能参数

**注:** 表中未加特殊说明性能参数均是在-IV 的反偏压下测得的,而"-"表示此参数在参考文献中未给出。

#### 1.2.2 波导集成型 PIN Ge 光电探测器

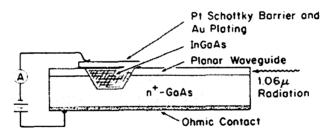

波导集成型光电探测器最早可以追溯到1974年,MIT 林肯实验室的Stillman G.  $E^{[21]}$  等人通过在 GaAs 衬底上外延生长化合物半导体 $In_xGa_{1-x}As$ 制备出了波导集成型 $In_xGa_{1-x}As$ /Pt 肖特基结光电探测器,如图 1.8 所示。自此,人们认识到

图 1.8 1974 年 Stillman G. E.制备的波导集成型In<sub>x</sub>Ga<sub>1-x</sub>As/Pt 肖特基结光电探测器结构<sup>[21]</sup>

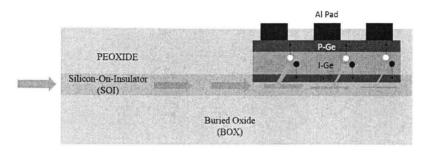

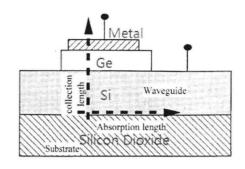

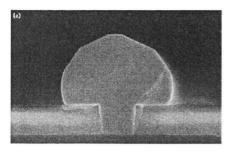

波导的集成在改善光电探测器光响应度方面的巨大潜力,然而由于材料生长技术的限制,首个波导集成型 PIN Ge 光电探测器是 2011 年 Masini G.<sup>[22]</sup> 等人利用蒸镀在 SOI 衬底上的多晶 Ge 膜制成的,如图 1.9 所示。尽管采用的是 Poly-Ge 作为1.3μm波段的光吸收材料,然而其暗电流密度却比传统垂直面入射 PIN Ge 探测器低约一个数量级,同时又具有至少高一个数量级的光响应度。此后的波导集成型 PIN Ge 光电探测器便逐渐成为一个研究热点,这种能够有效克服光响应度与带宽相互制约关系的方法也被推广应用于其他结构的探测器。

图 1.9 首例波导集成型 PIN Ge 光电探测器结构[22]

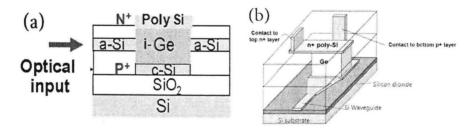

首例高性能波导集成型 PIN Ge 光电探测器是 2006 年 Liu J. F<sup>[23]</sup> 等人采用对接耦合的方法将选择性外延生长的 Ge 与多晶硅波导集成在一起实现的,如图 1.10 (a) 所示。该探测器中,顶部的本征 Ge 层既作为光吸收层又是波导的一部分;由于光子的吸收方向为本征 Ge 层的长度方向而非厚度方向,所以在-3V 的反偏压下,探测器在 1520nm 波长处的光响应度高达1.0 A/W,3-dB 带宽为4.5 GHz。与此同时,为了研究不同耦合机制对探测器性能的影响,他们还通过在 Si 波导上选择性外延 Ge 制备了倏逝波耦合的 PIN Ge 探测器,如图 1.10 (b)所示。由于倏逝耦合效率通常低于对接耦合效率,所以该探测器在相同偏压条件下的光响应度

图 1.10 2006 Liu J. F.等人制备的高性能波导集成型 PIN Ge 光电探测器<sup>[23]</sup>(a)对接耦合结构 (b)倏逝波耦合结构

仅为0.2 A/W, 3-dB 带宽也仅为 1.5 GHz。尽管在光响应度方面对接耦合结构的探测器具有很大优势,然而要实现光电探测器与波导间无缝对接对加工精度的要求极为苛刻,因此其工艺实现要比倏逝耦合结构的探测器复杂得多。在而后的十多年里, PIN Ge 光电探测器在结构设计上的发展基本上是围绕上述两种光学结构

展开的诸多优化,而其在工艺上的进展则始终与 Ge 的外延生长上技术保持同步。

2007年,Ahn Donghwan<sup>[24]</sup> 等人采用倏逝耦合结构并利用标准的 CMOS 工艺,制备出了在-IV 偏压下暗电流密度为1.3 A/cm²,1550nm 波长处响应度高达1.0 A/W,3-dB 带宽高达 7.2 GHz 的高性能波导探测器。同年,Yin Tao<sup>[25]</sup> 等人利用倏逝耦合原理在 SOI 衬底上制备出了-IV 偏压下带宽高达 31 GHz 的高速 PIN Ge 光电探测器。该探测器在-IV 反偏压下的暗电流密度低至27 mA/cm²,在较宽的光谱范围内光响应度均大于0.8 A/W。与此同时,来自 Luxtera(业界著名的硅光子器件供应商)的 Masini Gianlorenzo<sup>[26]</sup> 等工程师利用 130nm 标准 CMOS 工艺开发了全球首款内嵌波导集成型 PIN Ge 光电探测器的光探测芯片。该芯片在C 波段(1530~1560nm)展示出优异的性能:灵敏度高达-14.2 dBm(对应的误码率为10<sup>-12</sup>BER)即能够响应 0.038mW 的信号光,数据传输速率高达 10 Gbps。

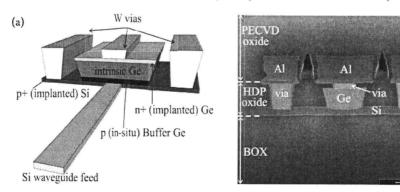

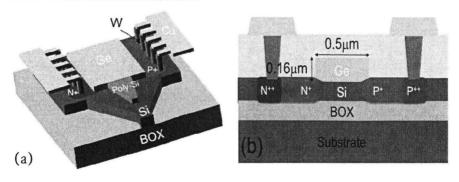

类似于传统的 IC 器件,OEIC 芯片的光子学器件发展也是不断朝着微型化、集成化及低功耗的方向发展的。2011 年,Derose Christopher T.<sup>[27]</sup> 等人设计并利用标准 CMOS 工艺实现了超紧凑波导集成型 PIN Ge 光电探测器,如图 1.11 所示。该探测器的有源区(Ge 区)的面积仅为1.3×4μm²但却有不俗的性能表现:在-1V 偏压下,暗电流密度低至40 mA/cm²(对应的暗电流约为 3nA),响应度高

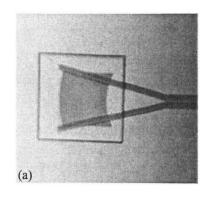

图 1.11 2011 年 Derose C.T.等人制备的超紧凑型波导集成型 PIN Ge 光电探测器<sup>[27]</sup> (a)器件 3D 结构(b)器件截面 SEM 图

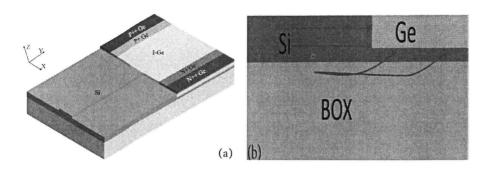

达0.8 A/W,3-dB 带宽更是达到了 45GHz。2012 年,来自法国的科学家 Vivien Laurent<sup>[28]</sup> 等人首先利用选择性外延技术生长出 Ge 膜而后采用离子注入技术在 Ge 上形成水平的 PIN 结构最后利用标准的 CMOS 金属化工艺制备出了零偏压下

**(b)**

数据传输速率高达 40Gpbs,1550nm 波长处响应度高达0.78 A/W的波导集成型光电探测器,如图 1.12 所示。最值得一提的是其在-2V 反偏压下的 3-dB 可达120GHz(这是目前见于报道的最高水平),这使得 Tb/s 的光通信与光互连成为可能。然而由于离子注入引入的损伤与缺陷导致其在-1V 反偏压下暗电流密度高达80 A/cm²,对应的暗电流为4μA,而这并不符合高速光电收发芯片对于探测器暗电流的要求<sup>[4]</sup>。

图 1.12 2012 年 Luarent Vivien 等人制备的波导集成型水平 PIN Ge 光电探测器 [28]

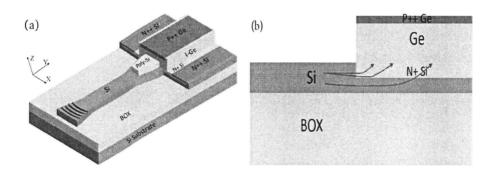

2016年,Chen H.<sup>[29]</sup> 等人设计并利用 CMOS 兼容工艺制备出了高性能的 Ge 波导探测器,如图 1.13 所示,其在-IV 偏压下的暗电流低至 3nA,1330nm 和 1550nm 波长处的响应度分别高达0.74 A/W和0.93 A/W,3-dB 带宽均大于 45GHz,能够很好地满足 50Gbps 光链路对数率的要求。表 1.2 列出了近十年来波导集成型 PIN Ge 光电探测器的研究进展。

**图 1.13** 2016 年 Chen H.等人制备的高性能波导集成型 PIN Ge 光电探测器<sup>[29]</sup>(a)器件 3-D 结构(b)器件截面示意图

尽管目前 OEIC 芯片的集成度远不如传统的 IC 芯片,但是业界已经有多家公司如国外的 Intel、Luxtera、SiFotonics、MACOM、Mellanox、Inphi 等都曾发布性能优越的硅光产品并在进一步加快硅光子模块批量生产的产业布局,国内的如华为、海信等也都先后发布了相关的硅光产品。以 SiFotonics 为例,其在 2016年底正式对外发布了集成有 8 个带宽为 40GHz 的 Si 基 Ge PIN 波导探测器的100G/200G 全集成相干光电收发芯片 TRQ411<sup>[30]</sup>。

虽然波导的引入使得光电探测器的光响应度不再受其频率响应的制约,但是亚微米甚至是深亚微米量级的波导截面尺寸对应用于探测器制备的微纳加工能力提出了很高的要求(这在对接耦合型波导探测器中表现得尤为突出)。当然现代先进的 CMOS 工艺能力早已进入纳米阶段,因此微纳加工技术已然不再成为限制波导集成型光电探测器向前发展的绊脚石;波导与商用单模光纤的光耦合问题如今也能通过高效的耦合光栅加以解决。此外波导的引入增加了工艺的复杂度使得设计与制造成本上升,但波导集成带来的探测器性能的巨大的飞跃使得波导探测器早已成为业界研究的主流。

| 年份   | 器件尺寸                      | 暗电流                 | 响应度      | 3-dB 带宽(GHz)  | 参考文献 |

|------|---------------------------|---------------------|----------|---------------|------|

|      | $(L \times W \times T)$   | (nA)                | (A/W)    | _             |      |

| 2007 | 10 × 7 × 1.1              | 10 <sup>3</sup>     | 1.08     | 7.2           | [24] |

| 2008 | $5\times0.8\times0.22$    | 15                  | 0.4      | 18            | [32] |

| 2009 | $15\times3\times0.33$     | 54                  | 1@-4V    | 42@-4V@1520nm | [32] |

| 2010 | $10\times0.65\times4.6$   | $1.3 \times 10^{3}$ | 1.06     | 32.6          | [33] |

| 2011 | $4 \times 1.3 \times 0.6$ | 3                   | 0.8      | 45@1530nm     | [27] |

| 2012 | $10\times0.5\times0.22$   | $4 \times 10^3$     | 0.8      | 120@-2V       | [28] |

| 2013 | $10\times0.46\times0.22$  | 25                  | 0.4@0V   | 50@0V         | [34] |

| 2014 | 10 × - × 1                | 50                  | 1.0      | 33            | [35] |

| 2015 | $13.8\times0.5\times0.4$  | 3.3                 | l        | 20            | [36] |

| 2016 | $14.2\times0.5\times0.16$ | 3.0                 | 0.74     | > 45          | [29] |

| 2017 | $10\times0.3\times0.26$   | 8                   | 0.2      | 34.7          | [37] |

| 2018 | $15 \times 4 \times 0.5$  | 42                  | 0.43@-2V | 48@-2V        | [38] |

表 1.2 近十年波导集成型 PIN Ge 光电探测器的研究进展

**注**: "器件尺寸"指的是探测器有源区(本征 Ge 区)的大小, "L"、"W"及"T"分别代表 Ge 区的长、宽及厚度且单位均为μm。表中的参数出特别声明外,均为在-1V 反偏压下,1550nm 波长处测得,而"-"表示此参数在参考文献中未给出。

不同于波导探测器,传统的垂直面入射探测器由于其光响应度与带宽之间存

在固有的相互制约关系,其愈来愈无法满足高灵敏度与高速应用场合对探测器性能的要求;但这并不意味着它将退出历史舞台,因为其相对于波导探测器具有独特的优势;工艺相对简单、制作成本低以及易于与光纤之间实现高效的光耦合且其性能也能通过引入谐振腔的手段得到一定程度的改善;更为重要的是,并非所有的应用场合都同时需要高灵敏度与高速的光电探测器,这同样也使得其在今天有其独特的生存空间。

#### 1.3 本文的主要研究内容及组织结构

在国家科技重大专项《硅基光互联后道工艺及耦合封装技术研究》 (2017ZX02315004)的支持下,本文开展了波导集成型垂直 PIN 结构 Si 基 PIN Ge 光电探测器的设计、制备与表征工作,重点研究了探测器的结构参数对于探测器各性能参数的影响。本论文的组织结构如下:

第一章:论证了在光子集成电路(OEIC)技术大发展的背景下开发一款高性能的近红外波导集成型光电探测器的意义,系统地介绍了 Si 基 PIN Ge 波导光电探测器的发展现状。

第二章:对波导集成型 PIN Ge 光电探测器的类型进行了梳理并对比研究了 PN 结光电探测器与 PIN 结光电探测器的基本工作原理最后给出了光电探测器的主要性能参数。

第三章:基于波导集成型性 PIN Ge 光电探测器制备的 3-D 工艺流程图,结合器件光刻版图详细地论述了波导集成型 PIN Ge 光电探测器制备过程中的各项关键工艺模块,包括:衬底的选择与处理,Poly-Si Taper 的制备,光波导与光栅的制备,Ge 的选择性外延以及器件的金属化。在讨论 Ge 的选择外延生长的同时简要地回顾了包括组分渐变 $Ge_xSi_{1-x}$ 缓冲层、低-高温生长(两步生长)在内的其他外延 Ge 技术。

第四章:采用电子扫描显微镜(SEM)与透射电子显微镜(TEM)对器件的结构进行了表征并结合第三章中的加工工艺参数对器件表征结果进行了简要的分析。测试了波导集成型 PIN Ge 光电探测器的主要性能参数包括暗电流、光响应度以及频率响应,并结合器件的表征结果对器件电性能测试结果展开了详细的分析与

讨论;

第五章: 对本文的工作进行了总结并对探测器的性能优化提出了一些潜在的解决方案。

#### 第 2 章 PIN 光电探测器的基本工作原理

当能量大于带隙的光子入射进入半导体后,其能量释放给价带的电子并使其 跃迁至导带,同时在价带中产生空穴;产生的电子空穴对在外电场的作用下被分 离开最终被电极收集从而 在外电路产生光电流。这种基于半导体本征光吸收的 内光电效应便是光电探测器工作的理论基础。

尽管在第一章中已经给出了探测器的基本分类,但是本章将在进一步厘清波导集成型 PIN 光电探测器分类的基础上探讨 PN 结与 PIN 结光电探测器的基本工作原理,最后将对表征光电探测器光电性能的几个基本参数如探测器的暗电流、光响应度以及 3-dB 带宽等展开研究。

#### 2.1 波导集成型 PIN 光电探测器的分类

本文所研究的是波导集成型 PIN Ge 光电探测器,探测器与波导的集成使其很好地克服了垂直面入射光电探测器中光响应度与带宽相互制约的矛盾,因而波导集成型光电探测器可以兼具高响应度与高带宽等优点。

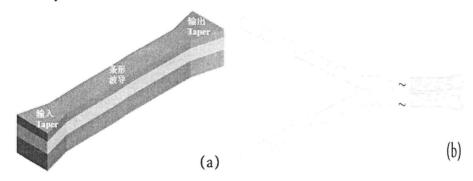

按照光波导与探测器间的光耦合方式,光电探测器又可分为对接耦合光电探测器以及倏逝耦合光电探测器;而根据 PIN 结中的宏观光电流的方向与衬底法线方向是否平行,波导集成型 PIN 光电探测器又可分为水平 PIN 光电探测器与垂直 PIN 光电探测器。

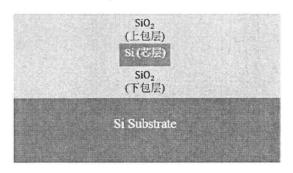

在对接耦合光电探测器中,光吸收层作为波导的一部分与波导对接在一起,如图 2.1<sup>[34]</sup> 所示。而对于倏逝耦合光电探测器,光通过倏逝波的形式将能量耦合进入光吸收层如 Ge 层中,如图 2.2 所示。采用对接耦合结构时,波导与探测器间的耦合效率较高(通常高达 90%以上),其光响应度通常都能达到1.0 A/W以上;而采用倏逝耦合结构时,由于波导的中只有约 50%~60%的能量能够耦合进入波导且存在较强的自由载流子吸收,所以倏逝波耦合波导光电探测器的光响应度的最高水平一般也只有0.8 A/W左右。

从制备工艺的角度来看,由于 Ge 材料本身作为波导的一部分,所以为了保证高效的光耦合,对接耦合 PIN Ge 光电探测器中波导输出端面与 Ge 端面必须

图 2.1 对接耦合波导集成型 PIN 光电探测器[34] (a)3D 结构示意图(b)2D 截面示意图

图 2.2 倏逝耦合波导集成型 PIN 光电探测器(a)3D 结构示意图(b)2D 截面示意图

做到无缝对接,否则端面反射损耗的存在会降低光电探测器的量子效率从而削弱探测器的光响应度。这对探测器的加工提出了不小的挑战,因而对接耦合波导光电探测器的工艺复杂度即成本要比倏逝波耦合波导光电探测器高。此外,通过分析不难发现,在对接耦合波导集成型光电探测器中光波导的上表面与 Ge 的上表面几乎处于同一水平高度,如图 2.1 所示,在此类结构的光电探测器中采用垂直 PIN 的电学结构会因 Ge 顶层的接触金属引入的光学吸收而劣化光电探测器的光响应度。所以目前文献中报道的的绝大多数波导集成型垂直 PIN Ge 光电探测器的光学耦合方式都为倏逝波耦合。

水平 PIN 光电探测器与垂直 PIN 光电探测器的主要区别在于: (1)对于水平 PIN 光电探测器,如图 2.1 与图 2.3 所示,衬底法线方向平行于"Z",光电流方向平行与"X",二者相互垂直即 PIN 结的宏观光电流的方向与衬底法向垂直;而对于垂直 PIN 光电探测器,如图 2.2 所示,衬底法线方向与光电流方向均平行与"Z"。值得注意的是,对于垂直面入射 PIN 光电探测器,如图 1.3 所示,其衬底

法线方向与光电流方向必定平行; 所以水平 PIN 光电探测器与垂直 PIN 光电探测器的分类是在波导集成型光电探测器的基础上进行的。(2)水平 PIN 光电探测器中,本征区中光生载流子的输运时间由本征区的宽度决定; 在垂直 PIN 光电探测器中,本征区光生载流子的输运时间则取决于本征区的厚度。

图 2.3 波导集成型水平 PIN Ge 光电探测器结构

波导集成型水平 PIN Ge 光电探测器中由于有效本征 Ge 区厚度很薄,所以此类探测器的 3-dB 带宽可以达到很高的水平。通过对比图 2.1(a)与图 2.3 不难发现波导集成型水平 PIN Ge 光电探测器中的水平 PIN 结的实现方式有两种:同质水平 PIN 结与异质水平 PIN 结。在图 2.1 (a)所示的光电探测器中,光电探测器的 P区、I 区及 N 区都是在 Ge 上形成的即此类 PIN 光电探测器中的 PIN 结为同质PIN 结。这种探测器中本征区中电场很强,光生载流子以饱和漂移速度进行输运所以带宽很高;此外由于离子注入后的退火过程中离子的横向扩散使得实际的本征 Ge 宽度进一步缩小,使得即使在零偏压下光生载流子也能获得接近饱和速度的漂移速度。然而由于 Ge 区上的多重掺杂引入的缺陷使得其暗电流密度高达几至几十A/cm²量级。在图 2.3 所示的探测器中,光电探测器的 P 区与 N 区都是形成与 Si 层之上的,Ge 区仅作为 PIN 光电探测器的 I 区,此时的 PIN 结为异质PIN 结,这避免了在 Ge 上的离子注入掺杂从而保证了 Ge 层的高质量,其暗电

流可低至数纳安量级。然而这种 Ge 光电探测器中本征 Ge 区中的电场仅仅是 Si 上 PIN 结本征 Si 区的较弱的边缘电场,这不利于光生载流子的收集,因此其带 宽不如图 2.1(a) 所示探测器。文献[34] 中探测器(图 2.1 所示结构)的带宽尽管高 达 120GHz,但是其暗电流大到高速光电收发芯片无法接受的地步;而文献[29] 中的探测器(图 2.3 所示结构)在探测器高达 67GHz 的情况下暗电流却可以低至 2.4nA。这很好的映证了上述的定性分析。

波导集成型垂直 PIN 结构光电探测器中的 PIN 结为异质 PIN 结,即 PIN 探测器的 P区(或 N区)是通过在 Ge 层上的离子注入掺杂实现的,而 N区(或 P区)则是形成与 Si 上的轻掺杂区之上的。这种结构的探测器由于 Ge 上的离子掺杂注入同样会使得探测器的暗电流偏大。

#### 2.2 光电探测器的基本工作原理

PIN 光电探测器是在 PN 结光电探测器的基础上在 P 区与 N 区之间插入了本征层而到的。所以在研究 PIN 结光电探测器的工作原理前有必要了解 PN 结光电探测器的基本工作原理以及它的局限性。本节将在简要回顾 PN 结光电探测器的基础上对 PIN 结光电探测器的工作原理展开讨论。

#### 2.2.1 PN 结光电探测器的工作原理

PN 结是由 P 型半导体与 N 型半导体间形成冶金学接触而形成的,当 PN 结用于光信号探测时称为 PN 结光电探测器或 PN 结光电二极管,其一般工作在反向偏置的状态下即 P 端接负电压而 N 端接正电压。因为反向偏置下: (1)无光照条件下流过 PN 结的电流十分微弱,仅为其反向饱和电流(2)耗尽区展宽,PN 结的势垒电容减小,RC 时间常数降低,有利于提高器件的频率响应; 同时由于耗尽区的展宽,有更多的光子在耗尽区被吸收,因而有利于保证探测器的探测效率。

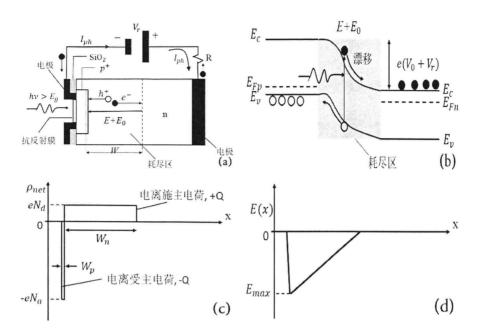

图  $2.4^{[39]}$  显示了 PN 结光电探测器的基本结构与工作模式、反向偏压下 PN 结的能带结构、净电荷分布以及电场分布。由图可知,当能量高于光吸收材料带隙  $E_g$  的光子在耗尽区内被吸收时,耗尽区产生的电子-空穴对立刻被外电场分离开并分别向探测器的 N 区与 P 区做漂移运动,最终被电极收集从而在外电路中形成光电流。通过分析不难发现,PN 结光电探测器存在以下不足之处:(1)器件

图 2.4 PN 结光电探测器[39] (a)结构与工作模式(b)能带图(c)净电荷分布(d)电场分布

耗尽区内的高浓度电离杂质对光生载流子的散射作用很强,导致光生载流子的实际漂移速度远低于其理论值,这将严重劣化其频率响应特性(2)耗尽区外距离耗尽区一个扩散长度以内的光生载流子将通过扩散运动到耗尽区后被耗尽区内电场分别扫向两极,而慢得多的扩散运动速度也将制约 PN 结光电探测器工作速度(3)由半导体物理学知识可知,光子的吸收大都发生在非耗尽区,因而探测器的量子效率很低。

#### 2.2.2 PIN 结光电探测器的工作原理

为了克服 PN 结光电二极管存在的上述缺点,人们发明了 PIN 结光电探测器。通过在 P 型半导体与 N 型半导体间插入一层较厚的本征(I 区)或低掺杂半导体能够使得探测器的势垒电容极大地降低从而提升器件的工作速度,同时由于本征半导体区在反偏时被全部耗尽因而 PIN 光电探测器的量子效率也有了较大地提升。

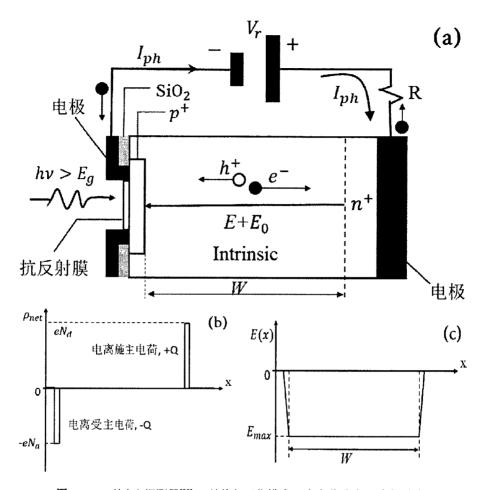

图 2.5<sup>[39]</sup> 显示了 PIN 结光电探测器的基本结构及工作模式、反向偏压下净电荷分布以及电场分布。PIN 光电探测器基本工作原理与 PN 结光电二极管类似。本征层的引入使得 PIN 结光电探测器的综合性能大大提升,本征(I)层的主要作

图 2.5 PIN 结光电探测器[39] (a)结构与工作模式(b)净电荷分布(c)电场分布

用有:(1)I 层为本征层或低掺杂层,电阻率高; PIN 光电探测器正常工作时, I 层 承载了绝大部分的器件端电压因而本征层有足够强的电场(2)有效的光吸收发生 在 I 层内及距 I 层一个扩散长度以内的区域,适当增加 I 区厚度可以在不影响器 件工作速度的前提下提高探测器的效率(3)I 层的厚度通常比反偏压状态下的 PN 结耗尽区大很多,从而降低了器件的势垒电容改善了器件的频率响应特性。然而并不能通过一味地增加 I 层的厚度来提高探测器的光响应度,因为 I 层过厚势必 延长光生载流子的输运时间从而造成探测器的 3-dB 带宽下降。这种光响应度与带宽相互制约的矛盾正是制约垂直面入射 PIN 光电探测器综合性能的症结所在。此外,为了抑制距 I 区一个扩散长度以内的区域向 I 区注入的扩散电流,PIN 结通常可以做成异质结即 I 区采用窄带隙材料如 Ge,而 P 区和 N 区材料的带隙却

大于I区材料。因此,在有光照时所有的光子吸收均发生在I区,避免了速度很慢的光生载流子的扩散运动从而提高了探测器的频率响应特性。

#### 2.3 光电探测器的主要性能参数

表征光电探测器性能水平的主要参数包括光电探测器的暗电流、光响应度以及 3-dB 带宽。探测器的暗电流大小往往可以反映出探测器光吸收材料质量的高低并作为探测器噪声的一个重要来源对探测器的探测灵敏度产生重要的影响,而探测器的光响应度及带宽则通常取决于设计者对探测器结构的优化程度,很多情况下设计者需要根据实际的应用需求折中考虑探测器的各项性能指标。

#### 2.3.1 暗电流

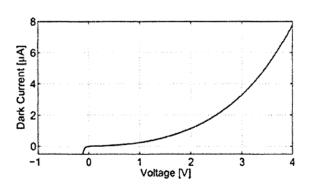

顾名思义,探测器的暗电流是指无光照条件下探测器中流过的电流。光电探测器暗电流包括体暗电流与表面暗电流。其中体暗电流的产生过程可用肖克利里德-霍耳理论<sup>[40-42]</sup>加以解释,体暗电流往往随外加偏压的增加而呈指数上述趋势,如图 2.6 所示。体暗电流主要取决于探测器光吸收材料如 Ge 的生长质量。

图 2.6 光电探测器体暗电流随外加偏压的变化关系[40]

表面暗电流则是由于 Ge 等半导体光吸收材料在界面处的周期性边界条件被破坏而引入的大量界面态所导致的。因而表面暗电流可以通过钝化 Ge 等的表面悬挂键来进行抑制。

综合考虑探测器的体暗电流与表面暗电流得到的总暗电流可由按下公式<sup>[43]</sup> 讲行估算:

$$I_{dark} = J_{bul \, k} \cdot A + J_{surf} \sqrt{4\pi} \cdot \sqrt{A} \tag{2.1}$$

其中 A 为探测器的结面积, $J_{bul k}$ 与 $J_{surf}$ 分别为探测器的体暗电流密度与表面暗暗电流密度,单位分别为 $mA/cm^2$ 与mA/cm。

#### 2.3.2 光响应度

探测器光响应度是衡量探测器效率的一个宏观物理量,通常记为 R,其定义为探测器的光电流与入射光功率的比值,单位通常为 A/W:

$$R = \frac{I_{ph}}{P_0} \tag{2.2}$$

其中, $I_{ph}$ 为从为净光电流,即为直接从探测器测得光电流(总光电流)与相同偏压条件下的暗电流的差值; $P_o$ 为入射到探测器中的光功率。值得注意的是,对于垂直面入射 PIN Ge 光电探测器, $P_o$ 指的是光纤的出射光功率 $P_{fiber}$ 减去探测器表面的反射损耗后的功率值;当探测器表面镀有抗反射薄膜时,表面的反射损耗可以忽略不计,此时 $P_o \approx P_{fiber}$ 。而对于波导集成型 PIN Ge 光电探测器, $P_o$ 的计算则需要考虑光波导的传输损耗以及光栅的耦合损耗。

此外,量子效率作为表征探测器光探测效率的一个微观物理量也被广泛地应用。光电探测器的量子效率又可分为内量子效率与外量子效率,分别记为 $\eta_i$ 与 $\eta_e$ :通常在不做特别声明的情况下探测器的量子效率指的是外量子效率。外量子效率 $\eta_e$ 与内量子效率 $\eta_i$ 的定义分别为:

$$\eta_e = \frac{\text{光生电子-空穴对的数目}}{\text{入射到探测器的光子数目}} = \frac{I_{ph}/e}{P_O/hv} = R \frac{hc}{e\lambda}$$

(2.3)

其中, $e=1.60\times 10^{-19}$ C为电子电量, $h=6.625\times 10^{-34}$ J·s为普朗克常数, $c=3\times 10^8$  m/s为真空中的光速, $\lambda$ 为入射光波的波长。式(2.3)将表征探测器探测效率的宏观物理量 R 与微观物理量 $\eta_e$ 联系到一起且二者都是波长的函数,通常都是先通过式(2.2)计算得出特定波长下的光响应度 R,然后再由式(2.3)换算得到相应的量子效率。将式(2.3)变换整理得

$$R = \eta_e \frac{e\lambda}{hc} \tag{2.4}$$

由ηε的物理定义可知

$$\eta_e < 1 \tag{2.5}$$

由此可知对于没有电流增益的光电探测器,特定波长入下探测器的光响应度

R 的最大值Rmax 满足

$$R_{max} < \frac{e\lambda}{hc} \approx 0.805\lambda$$

(2.6)

其中, $R_{max}$  的单位为A/W,而 $\lambda$ 的单位为 $\mu$ m。由此可知,探测器在1.55 $\mu$ m波长处的响应度小于1.25 A/W,而在1.31 $\mu$ m波长处的光响应度则低于1.05 A/W。

不同于外量子效率,内量子效率 $\eta_i$ 的定义为光生电子空穴对数目与被吸收的 光子数目之比,即

$$\eta_i = \frac{\text{光生电子-空穴对数目}}{\text{ 被探测器吸收的光子数目}} = \frac{I_{ph}/e}{P_{ph}/h\nu} = \frac{R}{\zeta}$$

(2.7)

其中, $\zeta = P_{ab}/P_o$ 为探测器吸收的光功率与入射到探测器的光功率的比值。光在半导体材料中的衰减规律可用下式描述:

$$I(x) = I_0 e^{-\alpha x} \tag{2.8}$$

其中I(x)为距离半导体材料表面 x 处的光强, $\alpha$ 则为半导体材料的光吸收系数,单位为 $m^{-1}$ 。由式(2.7)与式(2.8)可知,由于探测器光吸收材料在光吸收方向上的厚度有限,所以内量子效率是一个非常接近但小于 1 的数。

内量子效率 $\eta_i$ 与外量子效率 $\eta_e$ 通常可用以下理论公式<sup>[44]</sup> 联系起来:

$$\eta_e = (1 - R_{surf})\eta_i (1 - e^{-\alpha d_{ab}}) \tag{2.9}$$

其中, $R_{surf}$ 为探测器光吸收材料的表面光反射率(功率反射率), $d_{ab}$ 为在探测器光吸收材料在光吸收方向上的厚度。

#### 2.3.3 3-dB 带宽

探测器的 3-dB 带宽是衡量光电探测器对光信号响应快慢的一个重要物理量。 光电探测 3-dB 带宽主要取决于: 光生载流子的输运时间以及探测器的 RC 时间 常数。

光生载流子的输运时间又称光生载流子的渡越时间,指的是光生电子-空穴对从在耗尽区中产生到被有源区收集所需的时间。通常情况下,在光生载流子的输运过程中其一般以饱和漂移速度做漂移运动,而在绝大多数半导体材料中空穴的漂移速度往往远小于电子,因此由慢载流子-空穴输运时间决定的探测器的工作频率可由以下公式[45] 描述:

$$f_{tr} = 0.4 \frac{v_{h-sat}}{I} \tag{2.10}$$

其中, $v_{h-sat}$ 为探测器中光生空穴的饱和漂移速度,而 L 则探测器在光生载流子输运方向上的长度。

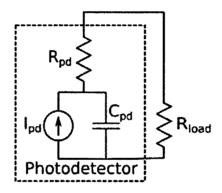

探测器的 RC 时间常数即为探测器寄生电容的充放电时间,其取决于探测器 反偏时的结电容以及探测器工作时的总电阻。由光电探测器的等效电路<sup>[40]</sup>(如图 2.7 所示)可知,由探测器寄生电容充放电快慢决定的探测器频率<sup>[4]</sup>为

$$f_{RC} = \frac{1}{2\pi (R_{pd} + R_{load})C_{pd}} = \frac{d}{2\pi (R_{pd} + R_{load})\varepsilon_0\varepsilon_r A}$$

(2.11)

其中, $R_{pd}$ 为探测器的寄生串联电阻, $R_{load}$ 为探测器的负载电阻, $C_{pd}$ 为探测器反偏时的结电容, $\varepsilon_0 = 8.854 \times 10^{-14}$  F/cm为真空中的电容率, $\varepsilon_r$ 为探测器光吸收材料的相对介电常数,A 为探测器的结面积,d 为载流子输运方向上的距离。

图 2.7 光电探测器的等效电路[40]

综合考虑探测器光生载流子输运时间及RC时间常数对探测器频率响应的影响,探测器的总带宽可由下式<sup>[40]</sup> 计算

$$f = \sqrt{\frac{1}{f_{tr}^2} + \frac{1}{f_{RC}^2}} \tag{2.12}$$

#### 2.4 小结

与其他文献中探测器的分类方法不同,本章对波导集成型 PIN Ge 光电探测器做了进一步的分类处理,并简要地分析了各种探测器的优缺点。由于本文所研究的是 PIN 光电探测器,所以本章仅在分析 PN 结光电二极管基本工作原理的基础之上简要地讨论了 PIN 光电探测的工作原理。

表征光电探测器性能的参数包括探测器的暗电流、光响应度以及 3-dB 带宽。值得注意的是,通过定量分析可知,垂直面入射光电探测器的响应度与带宽之间

存在相互制约的关系:而对于波导集成型光电探测器,波导的引入使得光生载流子的输运方向与光子的吸收方向相互垂直且互不影响。所以波导集成型光电探测器能有效地克服这一问题,这是本文选择波导集成型光电探测器作为研究目标的主要原因之一。

# 第3章 波导集成型 PIN Ge 光电探测器的制备

### 3.1 引言

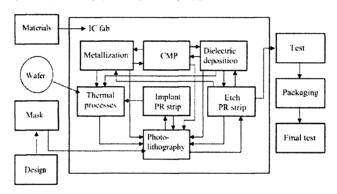

本文所研究的波导集成型 PIN Ge 光电探测器是在中科院微电子研究所 8 英寸标准 CMOS 工艺线上完成制备工作的。同传统的 IC 芯片的制作流程一样(如图 3.1<sup>[46]</sup> 所示)一样,波导集成型探测器的制备工艺主要包括光刻工艺、刻蚀工艺、薄膜工艺、化学机械抛光工艺以及最后的金属化工艺等。为了防止前后段工艺之间的交叉污染,Ge 外延生长前的无源部分如波导、光栅等的加工均采用前段工艺完成,而之后的加工均采用后段工艺实现。

图 3.1 IC 芯片制造工艺流程

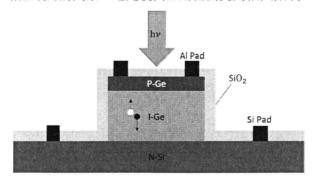

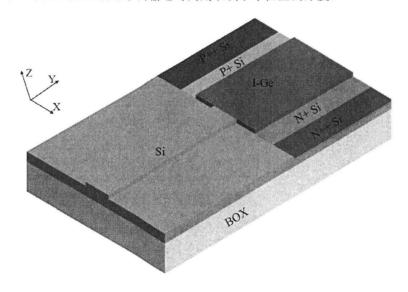

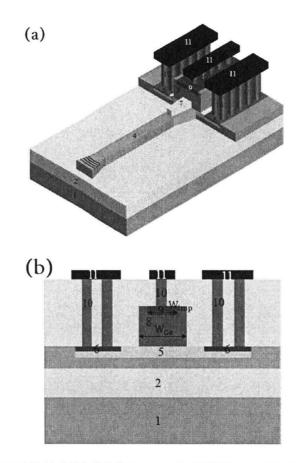

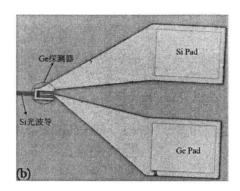

本文制备的波导集成型垂直 PIN Ge 光电探测器的结构如图 3.2 所示。图中各数字所代表的含义分别为: "1"为 Si 衬底,"2"为掩埋二氧化硅(Buried Oxide, BOX)层,"3"为聚焦耦合光栅,"4"为 Si 单模光波导,"5"为 Si 上 N 型轻掺杂区,"6"为 Si 上 N 型重掺杂区,"7"为 Poly-Si Taper,"8"为 Ge,"9"为 Ge 上 P 型重掺杂区,"10"为钨插塞;"11"为铝铜电极。光电探测器的版图如图 3.3 所示。

图 3.2 本文制备的波导集成型垂直 PIN Ge 光电探测器(a)3-D 结构(b)截面结构

图 3.3 本文制备的波导集成型垂直 PIN Ge 光电探测器版图

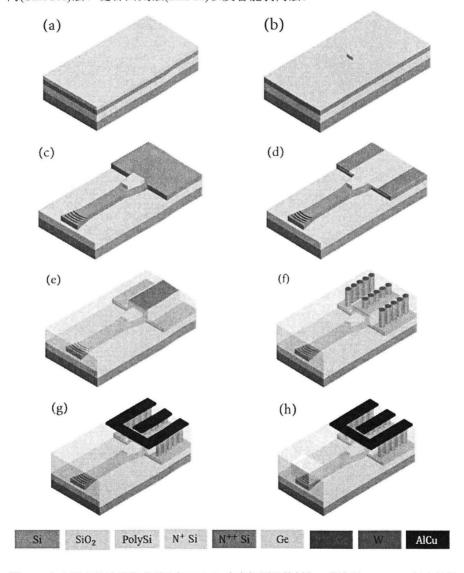

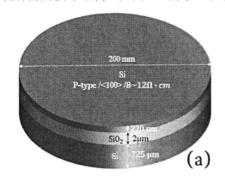

探测器的制备采用的是 8 英寸的 P 型<100>晶向,电阻率为8~12Ω·cm的 SOI 晶圆片,其顶层硅厚度为 220nm,BOX 层的厚度为2μm。制备波导集成型 PIN Ge 光电探测器的主要工艺包括: 光刻工艺、刻蚀工艺、薄膜工艺(如 Ge 的选择性外延、SiO<sub>2</sub>薄膜的淀积等)、离子注入工艺、化学机械抛光工艺以及湿法清洗工艺等。本文制备的波导集成型垂直 PIN Ge 光电探测器制备共包含 12 道光刻工艺,每一层光刻版对应的相关信息如表 3.1 所示。其制备工艺流程如图 3.4 所示。

本章将以图 3.4 为基础并结合探测器的版图详细地讨论本文所研究的波导集成型垂直 PIN Ge 光电探测器的制备工艺中的所有关键工艺模块: 衬底选择与处理、Poly-Si Taper 的制备,光波导与光栅的制备、Ge 的选择性外延以及探测器的金属化工艺。在整个光电探测器的制备过程中,Ge 的外延是最为关键的工艺,因此本章的也将在回顾诸多外延方法的基础之上重点讨论 Ge 的选择性外延。

| 光刻版代号 | 对应结构 说明            |                                |  |

|-------|--------------------|--------------------------------|--|

| PY    | Poly-Si Taper      | Poly-Si 的刻蚀                    |  |

| WG    | 光波导                | 顶层 Si 的刻蚀                      |  |

| FC    | 聚焦耦合光栅 顶层 Si 的浅刻蚀  |                                |  |

| NS    | 探测器的N区             | 顶层 Si 上的 P 离子注入                |  |

| NSS   | Si 欧姆接触重掺杂区        | 顶层 Si 上的 P 离子重掺杂               |  |

| Ge    | Ge 的外延窗口           | SiO <sub>2</sub> 的刻蚀、Ge 的选择性外延 |  |

| GP    | 探测器的 P 区以及 Ge 欧姆接触 | Ge 上的 B 离子重掺杂                  |  |

|       | 重掺杂区               |                                |  |

| GCA   | Ge 接触孔             | SiO <sub>2</sub> 的刻蚀,Ge 层金属接触  |  |

| CA    | Si 接触孔             | SiO <sub>2</sub> 的刻蚀。Si 层金属接触  |  |

| MI    | AlCu 电极            | AlCu 的刻蚀                       |  |

| PD    | Pad                | SiO <sub>2</sub> 的刻蚀           |  |

| LT    | 光栅正上方的通光孔          | SiO <sub>2</sub> 的刻蚀           |  |

表 3.1 本文制备的波导集成型 PIN Ge 光电探测器版图信息

### 3.2 波导集成型光电探测器的制备

本文所研究的波导集成型光电探测器的制备采用的是 CMOS 兼容工艺,其中光刻工艺采用的是先进的 248nm 深紫外(DUV)光刻技术,其最小可分辨线宽为 180nm; 干法刻蚀技术采用的是电感耦合等离子体(ICP)刻蚀技术,Ge 的外延结合了低-高温两步生长法及选择性外延生长法的优势,器件的金属化工艺采用的是标准 CMOS 金属化工艺模块。

### 3.2.1 衬底的选择与处理

绝缘体上硅(Silicon-On-Insulator, SOI)的衬底的广义定义为中间夹有绝缘介质层的双单晶硅层结构,而用于微电子领域与硅基光电子领域的 SOI 衬底中的

绝缘介质层通常为SiO<sub>2</sub>膜层。由于 SOI IC 器件的低功耗与高速特性,SOI 衬底自诞生以来就被广泛地应用各种电子 IC 器件的制造上;此外 SOI IC 器件的抗辐照特性使其广泛应用于宇航 IC 领域。目前主流的 SOI 衬底制备方法包括注入氧分离(SIMOX)法、键合回刻法(BESOI)以及智能剥离法。

图 3.4 本文研究的波导集成型垂直 PIN Ge 光电探测器的制备工艺流程 (a)SiO<sub>2</sub>干氧生长及 Poly-Si 的淀积(b)Poly-Si Taper 的形成(c)波导和光栅的形成(d)项层 Si 掺杂形成探测器 N 区及 Si 层欧姆接触重掺杂区(e)Ge 的选择性外延、CMP 及 P 型重掺杂(f)Si 层与 Ge 金属接触 的形成(g)AlCu 的淀积形成电极(h)通光孔的形成

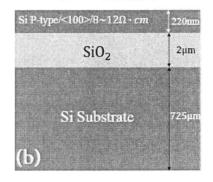

此次波导探测器的制备选择的 SOI 衬底规格如图 3.5 所示。由于 SOI 衬底中 SiO<sub>2</sub>埋氧层(Buried OXide, BOX)与顶层 Si 在光通信波段的波长窗口内的折射率 存在较大差异(在 1550nm 波长处,SiO<sub>2</sub>与 Si 体材料的折射率分别约为 1.46 与 3.5),这使得光能够很好的限制在以 Si 材料为芯层材料而以SiO<sub>2</sub>为包层材料的波导结构中,所以仅通过简单的刻蚀工艺与SiO<sub>2</sub>薄膜淀积工艺就能在 SOI 衬底上实现所需的波导结构,如图 3.6 所示。在波长 1550nm 处,芯层厚度为 220nm Si

图 3.5 本文制备探测器所采用的 SOI 衬底(a) 3-D 结构示意图(b)2-D 截面示意图

波导仅支持光波的单模传输;这一点可以从 Chrostowski L.<sup>[40]</sup> 等人所做的理论仿真看出,如图 3.7 所示。这一厚度也被诸如 IME、IMEC 及 LETI 等国际著名的硅光子芯片代工服务商所采用,因此这一厚度已经成为业界的主流。此外由理论分析可知,为了确保 Si 波导中传播的 TE 模式的光能量不泄露到衬底 Si 层,其包层厚度必须足够厚,一般大于1μm。

图 3.6 基于 SOI 衬底的硅光波导截面示意图

首先对 SOI 晶圆进行"打标"处理以便流片过程中的管理,而后对晶圆片进行栅氧化层生长前所需的标准清洗以去除晶圆表面残留的颗粒污染物以及 Si

3 Single mode cutoff (TE, TM)

2.5

1.5

0 50 100 150 200 250 300 350 400

的自然氧化层,接着立即送入高温氧化炉进行厚度约为60Å的SiO2生长。

图 3.7 波导模式有效折射率随波导芯层厚度的变化关系[40]

Slab Thickness [nm]

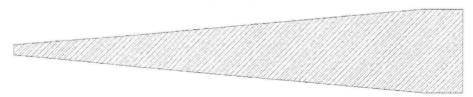

## 3.2.2 Poly-Si Taper 的制备

光波导输出端的 Taper 结构,如图 3-2 (a)中的"7"所示,用于增强光波导与探测器间的光耦合效率<sup>[29]</sup>。首先在处理好的 SOI 衬底上淀积约 150nm 厚的 Poly-Si,如图 3.4 (a)所示,而后采用 ICP 刻蚀技术在晶圆表面刻蚀出厚度为 150nm 的 Taper 结构,其对应的版图 PY 如图 3.8 所示。由于 Poly-Si 与单晶 Si 化学本质相同,所以干法刻蚀 Poly-Si 时二者的刻蚀速率几乎为 1:1 即刻蚀 Poly-Si 时对单晶 Si 的选择比几乎为零; 此外在干法刻蚀时通常会采用一定的过刻蚀量用于保证所需刻蚀的材料完全被刻蚀干净。为了确保图形区之外的 Poly-Si 完全被去除同时又不损伤表面的 Si 层,因而在淀积 Poly-Si 之前淀积一层薄的SiO<sub>2</sub>层作为刻蚀的停止层(多晶硅刻蚀采用的是Cl<sub>2</sub>,Poly-Si 对SiO<sub>2</sub>的刻蚀选择比超过 30)。刻蚀完成后最终得到如图 3.4(b)所示的 Poly-Si Taper 结构。

图 3.8 Poly-Si Taper 结构对应的版图

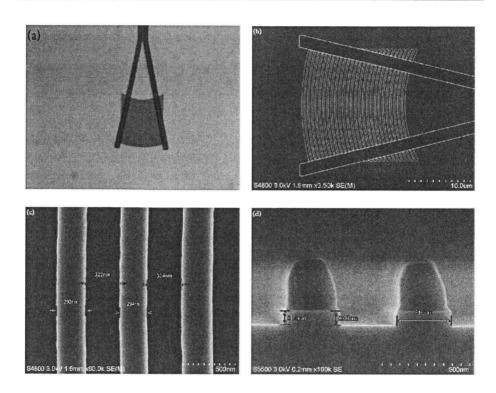

## 3.2.3 光波导与光栅的制备

通常波导集成型光电探测器中的波导都由输入端 Taper、条形波导以及输出

端 Taper 组成, 其结构如图 3.9 (a)所示, 版图 WG 如图 3.9 (b)所示(由于波导过长, 所以图中只给出了部分条形波导的版图)。 波导的制备是通过刻蚀项层硅来完成的, 刻蚀的深度为 220nm, 刻蚀停止层为 BOX 层, 刻蚀采用的气体同刻蚀 Poly-Si。

图 3.9 本文制备的波导集成型探测器中集成的波导(a)3-D 结构(b)版图

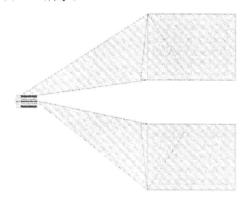

一般地,光纤的芯径约为10μm而单模光波导的截面尺寸为 450nm (本文采用的单模条形光波导的宽度),二者相差甚大。若采用垂直面入射式光电探测器中经常采用的端面耦合,光纤与波导中的模式的模斑面积相差将达 700 倍之多;因此采用端面直接耦合时,波导集成型光电探测器中波导与光纤的耦合不仅对对准精度要求十分苛刻而且耦合效率也十分低下。所以对于波导集成型光电探测器,光纤与光波导间的光耦合一般采用光栅耦合。输入耦合光栅是通过干法刻蚀技术形成于波导的输入 Taper 结构之上的,若采用传统的直条形光栅,较高耦合效率下所要求的输入 Taper 的长度都在数百微米的量级,这阻碍了波导集成型光电探测器向微型化、集成化方向发展。

为了在提高光纤到波导的耦合效率的同时减小器件的尺寸,本文采用的是聚焦光栅,对应的版图 FC 如图 3.10 所示。聚焦光栅由若干弧形硅条组成,其对光有一定的会聚作用因而能够显著提高光纤到波导的耦合效率,同时又能够满足器件小型化的要求。本文所采用的聚焦光栅是通过 SOI 衬底顶层 Si 的浅刻蚀形成的,刻蚀深度控制在 70nm 左右;由于刻蚀时没有停止层,实际的光栅刻蚀深度是通过控制刻蚀时间调整的。光波导及聚焦光栅刻蚀完成后器件的结构如图 3.4 (c)所示。

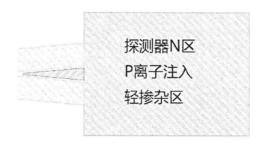

在完成波导集成型光电探测器中的无源组件的制备之后,在顶层 Si 靠近 Poly-Si Taper 一侧的特定区域内通过离子注入技术掺入磷(P)离子以制备 PIN 光

图 3.10 聚焦光栅版图

电探测器的 N 区,对应的版图 NS 如图 3.11 所示;而后在 N 型注入的基础上再

图 3.11 PIN 光电探测器的 N 型区(离子注入)版图 NS

次进行高剂量低能量的 P 离子注入以在 Si 上形成浅的欧姆接触的重掺杂区,对应版图 NSS 如图 3.12 所示;此外由图 3.12 可知,Si 中离子重掺杂区域均远离波导的中心轴线,这是为了减小重掺杂区域内光的自由载流子吸收从而保证探测器的光响应度。

图 3.12 Si 上欧姆接触重掺杂区对应版图 NSS

需要注意的是,为了减小离子注入引入的表面损伤以及抑制离子注入过程中沟道效应,离子注入前需在 Si 表面淀积一层薄的注入掩蔽层。在流片过程采用的是SiO<sub>2</sub>薄膜作为离子注入的掩蔽层。离子注入后为了激活注入的 P 离子同时修复注入损伤,采用快速热退火(RTA)设备对晶圆片进行高温退火。相比于传统的炉管退火,RTA 设备具有快速的升降温能力因而能够在激活杂质的同时尽可能地减少离子在退火过程中的再扩散从而获得更加陡峭的杂质分布。

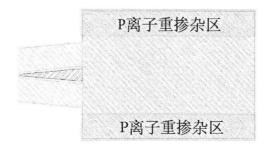

## 3.2.4 锗的选择性外延

Ge 高质量异质外延生长是实现高性能 Ge 光电探测器的重要前提,因为 Ge 中的穿透位错密度(TDD)以及表面的粗糙度直接影响到探测器的暗电流继而对探测器的光响应度以及高频性能产生影响。

Ge 的晶格常数为 5.6579Å,Si 的晶格常数为 5.43095 Å,二者间的晶格失配高达 4.2%;此外,Ge 的热膨胀系数比 Si 大一倍以上(Ge 的热膨胀系数为5.9 ×  $10^{-6}$ /K,Si 的热膨胀系数为  $2.6 \times 10^{-6}$ /K)。晶格常数失配与热膨胀系数失配使得 Si 基上的高质量 Ge 外延变得十分困难。目前在 Si 上实现低位错密度与低表面粗糙度 Ge 外延的方法主要有三种:(1)Ge 组分渐变的  $Ge_xSi_{1-x}$ 缓冲层技术(2)低-高温生长技术(3)选择性外延技术。

由于 $Ge_xSi_{1-x}$ 的表面能低于 Si, $Ge_xSi_{1-x}$ 与 Si 之间的晶格失配程度低于 Ge 与 Si 之间的晶格失配;因而 Ge 组分渐变的 $Ge_xSi_{1-x}$ 缓冲层的引入能使得在其上 生长 Ge 层时处于层状生长模式即 Frank-van der Merwe 模式 $[^{47]}$  ,故能有效降低 TDD 以及 Ge 层表面粗糙度。早在 1984 年, $Luryi^{[10]}$  等人采用 180nm 厚的 Ge 组分渐增的 $Ge_xSi_{1-x}$ 缓冲层在分子束外延(MBE)设备山生长出质量较高的厚度为数微米的 Ge 膜。随后  $Fitzgerald^{[48]}$  等人在此基础之上优化了 Ge 组分的变化梯度使 Ge 膜中的 TDD 处于~ $10^6$ / $cm^2$ 的较低水平。此外, $Wong^{[6]}$ 等人采用 Ge 组分递减的 $Ge_xSi_{1-x}$ 缓冲层技术制得了 TDD 低至 $10^5$ / $cm^2$ 的 Ge 膜,其表面粗糙度也仅有 1.1nm。不难看出,为了获得高质量的 Ge 膜, $Ge_xSi_{1-x}$ 缓冲层要足够厚,通常为数微米。这不仅不利于器件的集成,同时也使得器件的制造周期变长。低-高温生长法可以有效的克服这一缺点。在这种方法中,首先在较低温度  $(300~400\,^{\circ}C)$ 环境下生长一层很薄(30~50nm)的 Ge 层作为缓冲层,然后将温度升

高至 600℃以上以获得较高的生长速率及较好晶体质量。在低温下,吸附在 Si 表面的 Ge 原子的迁移率较低因而其 3 维成核生长被抑制,同时 Ge 与 Si 间的晶格失配也能通过此低温层中的高密度位错得到释放。通常情况下,采用低-高温法生长 Ge 膜时会引入退火工艺以进一步降低 Ge 膜的 TDD 及表面粗糙度。

选择性外延生长技术在 GaN 器件的制备中应用得十分普遍, 其降低 TDD 的基本原理类似于 Czochralski<sup>[49]</sup> 法生长 Si 晶锭过程中的"收肩", 二者都是通过将高密度的位错限制在一较窄区域内从而降低而后生长的晶体的 TDD。在 Ge 的选择性外延生长工艺模块中,首先通过光刻技术与刻蚀技术在硬掩模材料SiO<sub>2</sub>上形成外延窗口,其次再利用 Ge 组分渐变的Ge<sub>x</sub>Si<sub>1-x</sub>缓冲层生技术或者低-高温生长技术在图形窗口中外延出高质量的 Ge 膜。由于源于Ge<sub>x</sub>Si<sub>1-x</sub>缓冲层或低温 Ge 层中的穿透位错向上攀沿生长的方向与晶圆法线方向并不平行,所以绝大多数穿透位错线最终都能被窗口的侧壁所捕获并终止于侧壁。相对于非选择性外延,选择性外延生长得到的 Ge 膜的 TDD 通常要低两个数量级且绝大部分位错都被限制在Ge<sub>x</sub>Si<sub>1-x</sub>缓冲层或低温 Ge 层中,如图 3.13<sup>[50]</sup> 所示。但是由于外延窗口的图形化定义增加了工艺成本,因而 Li Q.<sup>[51]</sup> 与 Hungafu Y.<sup>[50]</sup> 等人分别提出了无光刻的 Ge 选择性外延技术以降低选择性外延的成本。

图 3.13 Ge 外延的位错密度对比(a)非选择性外延 TEM 图(b)选择性外延 TEM 图

本文所研究的波导集成型 PIN Ge 光电探测器的制备过程中的 Ge 外延结合了低-高温生长技术与选择选外延技术的优点。在完成了探测器的 N 区 P 离子注

入及相应的热退火工艺之后,首先用 PECVD 技术在晶圆片淀积一层厚度为 $t_{pre-cmp}$  的SiO<sub>2</sub>膜,而后通过 CMP 技术将其减薄至厚度 $t_{post-cmp}$ ;不难看出波导的形成在晶圆片表面引入了高度约 220nm 的台阶,因此在保证探测器 Ge 区厚度 $t_{Ge}$ 的前提下 CMP 过程中SiO<sub>2</sub>的研磨量至少为 220nm,所以SiO<sub>2</sub>的淀积厚度 $t_{pre-cmp}$  应满足关系:  $t_{pre-cmp} \geq t_{post-cmp} + 220nm$ 。在本文中 $t_{Ge} \approx t_{post-cmp} \approx 500nm$ ,所以应有 $t_{pre-cmp} \geq 720nm$ ;此外需要考虑 PECVD 工艺的均匀性以及给 CMP 工艺留有足够的工艺余量,最终取 $t_{pre-cmp} \approx 1$ µm。在 PECVD SiO<sub>2</sub>的膜厚减薄至 500nm 之后,利用光刻技术与 ICP 干法刻蚀技术在晶圆片表面定义出长度 $L_{Ge}$ 为15µm,宽度 $W_{Ge}$ 分别为 1、2、3、4 及 5µm的外延窗口,其版图 Ge如图 3.14 所示。随后,在利用标准的去胶清洗工艺去除圆片上残留的光刻胶及聚合物之后再利用稀释的氧化物缓冲腐蚀液(HF 溶液与NH<sub>4</sub>F溶液的按一定的比例的混合液)对晶圆片进行彻底的清洗,这一步清洗的主要目的在于去除各外延窗口底部形成的自然氧化物。

图 3.14 外延窗口定义所对应的版图 Ge

目前,实现 Si 基 Ge 外延的主流技术包括 MBE 与 CVD。前者是利用高真空度(可达10<sup>-8</sup>Pa)下 Ge 原子在 Si 表面的物理成核过程;而后者则是前驱物锗烷(GeH<sub>4</sub>)在分解反应中的产物 Ge 在 Si 表面的成核生长过程。在 MBE 中,由于 Ge 原子是通过超高真空环境下高温蒸发纯净的 Ge 材料得到的,薄膜的淀积速率能够得到精确控制且能够实现对薄膜的实时原位监控。尽管如此,由于需要极高的真空度,成膜速率很慢;所以 MBE 生长 Ge 常见于科学研究而非工业上的大规模批量生产。对于 CVD 技术,按照真空度也可将其分为超高真空 CVD(UHV-

CVD)以及减压 CVD(RPCVD)等。本文在制备波导型光电探测器过程中所涉及的 Ge 外延采用的是 RPCVD 系统。相对于 UHV-CVD, RPCVD 具有工艺相对简单、工艺周期短、无需高真空以及适合批量化生产等优点。

为了防止外延窗口底部的 Si 再次被氧化,外延前清洗工艺结束后晶圆片被立即送入 RPCVD 设备工艺腔中。随后工艺腔温度升高至 800℃以上并通入一定量的H<sub>2</sub>对整个晶圆片进行高温烘烤以去除外延窗口底部的 Si 表面的自然氧化硅层;随后,将腔温下调至 400℃左右同时以一定流量通入GeH<sub>4</sub>从而完成低温 Ge的生长;最后将腔温升高至 600℃以上同时调节前驱物的比例及流量以获得较高的生长速率从而完成高温 Ge 层的生长。此外,为了降低 Ge 层中的 TDD 以及表面粗糙度,实际工艺过程中分别在低温 Ge 层生长结束后以及高温 Ge 层生长结束后进行H<sub>2</sub>氛围下的高温原位退火。由于 Ge 外延生长的各项异性<sup>[52]</sup>, Ge 外延生长完成后其顶部与外延窗口的结合处可能出现缝隙<sup>[53]</sup>(如图 3.15 所示),这将不利于波导与探测器间的集成(这对于对接耦合的 Ge 光电探测器更加严重)以及后续工艺的开展。因此高温 Ge 层必须足够厚(> 1μm)以避免这个问题。Ge 外延生长后必须采用 CMP 工艺对晶圆片表面进行平坦化处理以满足后续光刻工艺对于表面平整度的要求。CMP 前后探测器的 Ge 区如图 3.16 所示。

图 3.15 外延 Ge 顶部与外延窗口结合处出现未完全填充现象[53]

图 3.16 Ge 形貌(截面 SEM 图)对比(a)CMP 前(b)CMP 后

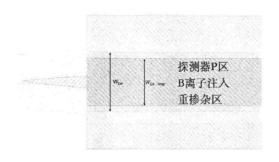

PIN Ge 光电探测器的 P 区是通过离子注入掺杂技术形成于 Ge 层之上的, 离 子种类为硼(B)离子, 对应的版图 GP 如图 3.17 所示。值得注意的是, Ge 层 P 型 离子注入区域的与 Ge 所在区域并不完全重合,二者的边缘之间有一定的间距即  $W_{Ge-imp} \leq W_{Ge}$ 。如前所述,选择型外延的一个重要优点是绝大部分穿透位错被 限制在低温 Ge 层中, 考虑到 Ge 的表面具有大量的悬挂键, 所以 Ge 侧壁的表面 态及缺陷密度很高。而 Ge  $\boxtimes$  P 型离子注入区域的宽度 $W_{Ge-imn}$ 小于 Ge  $\boxtimes$  宽度 W<sub>Ge</sub>能够有效削弱正常工作时探测器侧壁的电场从而可以有效抑制探测器暗电 流中的表面漏电流成分[54]。此外,之所以选择在Ge 层上注入P 型杂质(本文在Ge 层注入的杂质为 B 离子)是因为 B 的相对原子质量比 P 小, 离子注入对晶格 造成损伤也比较小因而能够抑制暗电流中的体暗电流成分。最后由于存在费米钉 扎效应[55] 导致 Ge上的 N 型欧姆接触较难实现,因此 Ge上 P 型欧姆接触能够 有效降低半导体金属接触势垒,从而改善探测器的频率响应特性。同 Si 中注入 离子的激活, Ge 中离子注入后的退火激活以及晶格损伤也是采用 RTA 技术以防 止 P 离子在退火过程中的扩散。在实际的制备工艺中, 受工艺条件的限制, Ge 中注入离子的激活退火所使用的设备与 Si 中 P 离子的退火相同: 退火前需在晶 圆片表面淀积一层薄的SiO<sub>2</sub>层,一是防止退火过程中 B 离子的外泄从而影响欧姆 接触, 更重要的是为了防止 Ge 原子的挥发从而污染工艺腔。Ge 的选择性外延、 CMP 以及离子注入完成之后器件的结构如图 3.4 (e)所示。

图 3.17 Ge 层 P 型注入所对应的版图 GP

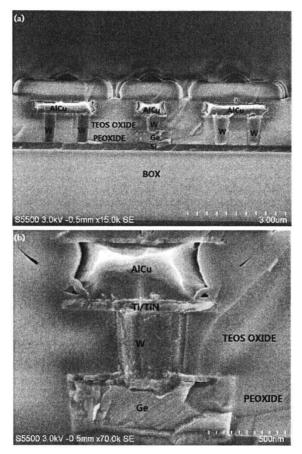

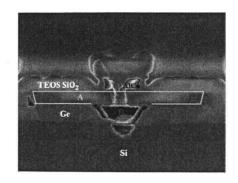

### 3.2.5 器件的金属化

器件金属化的目的在于完成器件间的互联以及对外提供器件测试及封装时所需的引线电极。本文所研究的波导集成型光电探测器的金属电极的形成采用的是标准的 CMOS 器件金属化工艺模块。首先,采用 PECVD 技术在完成了上述各项工艺的晶圆片表面淀积一厚度约为500 nm的正硅酸乙酯 (TEOS) SiO2膜,然后利用 DUV 光刻技术与 ICP 刻蚀技术在SiO2膜依次制备出 Si 与 Ge 的接触孔(对应版图 GCA、CA 如图 3.18 所示),考虑到探测器的本征 Ge 层中的电场的均匀性,Si 的接触孔分布在 Ge 区的两侧同时以 Ge 区的轴向中心线为对称轴。在完成相关的清洗工艺后,采用物理气相淀积(PVD)技术在晶圆片上淀积一层薄的金属镍层并进行高温快速热退火以在接触孔内形成镍硅(NiSi)、镍锗(GeNi)合金。半导体金属化合物能够进一步的降低器件的接触电阻提升器件的频率特性。在利用热的 HCI 溶液去除SiO2表面未合金化的 Ni 后,采用 PVD 技术在接触孔内依次淀积钛(Ti)、氮化钛(TiN)作为金属钨(W)的黏附层与阻挡层。钨塞的形成是通过 PECVD 技术在接触孔内填充满 W 来实现的,SiO2表面的过量 W 通过随后的CMP 工艺加以去除。钨塞形成后器件的结构如图 3.4 (f)所示。

图 3-18 Ge 与 Si 接触孔对应版图 GCA、CA

器件的金属引线与电极是通过图形化定义 AICu 合金来完成的,对应的版图

MI与PD如图 3.19 所示。首先,钨塞形成后在圆片表依次淀积薄的 Ti/TiN 膜以及约 400nm 厚的 AlCu 合金;然后在利用氯气的干法刻蚀制备出金属引线;最后利用厚度约为 600nm 的 TEOS SiO<sub>2</sub>对整个器件进行钝化处理并利用干法刻蚀形成金属电极(Pad)。最后在聚焦耦合光栅的的正上方刻蚀出通光孔(其版图 LT 如图 3.20 所示)。通光孔的形成有利于器件进行光电性能测试时光纤与光栅的耦合对准。在完成整个器件的合金化处理之后,器件的整个制作过程就正式结束了。器件的最终形貌如图 3.21 所示。

图 3.19 探测器的金属电极形成对应版图 M1 与 PD

图 3.20 探测器通光孔对应版图 LT

图 3.21 本文所制备的波导集成型 PIN Ge 光电探测器光学显微图(a)光栅及波导(b)波导及 Ge 光电探测器

### 3.3 小结

相比于垂直面入射光电探测器<sup>[56]</sup>,波导集成型光电的探测器制备工艺要复杂的多。工艺复杂度的增加主要源于探测器与波导、光栅等无源器件的集成,但这将带来探测器性能的极大提升。本文所制备的波导集成型 PIN Ge 光电探测器需要十二次光刻工艺,本章在结合器件版图的情况下对探测器制备过程中的所有关键工艺模块如衬底的选择与处理、Poly-Si Taper 的形成、光波导与光栅的刻蚀、Ge 的选择型外延以及器件的金属化工艺展开了详细的讨论,重点讨论了 Ge 的外延技术,给出了波导集成型光电探测的制备关键工艺的 3-D 流程图(图 3-6)。由于篇幅的原因,制备过程中许多十分重要的工艺如湿法清洗工艺、Ge 的 CMP工艺并没有展开详细讨论。尽管这些工艺是标准的 CMOS 工艺,但是在应用到光子学器件尤其是探测器、激光器等有源器件上时又有许多需要特别注意的地方。关于利用中科院微电子研究所的标准 CMOS 工艺线实现垂直面入射与波导集成型 PIN Ge 光电探测器一些工艺细节可以参考文献[56]~[58]。

## 第 4 章 光电探测器的结构表征与性能测试

### 4.1 引言

由于加工过程中存在不可避免的误差,实际制得的探测器结构与理论设计也一定存在偏差,这就导致了实际的器件性能与器件仿真结果存在偏差,且通常情况下实际的器件性能总是劣于仿真结果。所以探测器的结构表征对于分析工艺误差及其来源至关重要同时其可以帮助修正器件仿真参数使器件性能更加接近理论仿真结果。对于本文所制备的波导集成型 PIN Ge 光电探测器,采用扫描电子显微镜(SEM)以及透射电子显微镜(TEM)两种基本的表征手段对探测器的光栅、波导以及外延 Ge 区等进行定性与定量的分析。

波导集成型光电探测器的性能测试包括光学性能测试以及光电性能测试,前者主要是针对光栅及光波导等无源部分的光学传导性能的测试及相应的量化分析;而后者则是在探测器加载反向偏压的条件下测试其对外部光信号的响应能力,主要包括探测器的暗电流测试,光响应度测试以及频率响应测试。尽管在第二章中已经给出了探测器基本性能参数的定义以及可能存在的影响因素,但是在进行测试时仍需了解基本性能参数的测试原理,这有助于我们深刻理解影响探测性能的各项结构参数以及工艺参数,同时也为探测器的性能优化指明了方向。

因此,本章在对探测器各基本性能参数进行测试之前将对各项参数的测试原理加以简要介绍;在给出测试结果后,将结合第二章给出的基本概念、第三章中给出的各项工艺参数以及本章中给出的器件结构的表征结果对各项性能参数的测试结果展开较为详细的分析讨论。此外,在对探测器的各项性能参数的测试结果进行分析时结合了当今关于提升波导集成型光电探测器性能的一些新进展给出了提升探测器性能的一些潜在的优化方案。

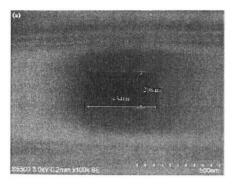

## 4.2 探测器的结构表征

本节基本上按照探测器的制备工艺顺序给出探测器结构的表征结果并进行 相关的分析。考虑到对探测器各部分进行结构表征时的复杂度以及成本,除了对 探测器的外延 Ge 区进行了 TEM 表征外, 其他的诸如波导与光栅仅采用 SEM 对其进行结构表征。

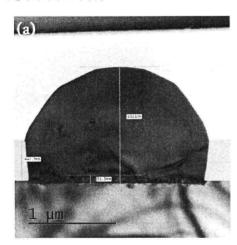

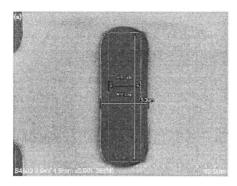

本文所研究并制备的探测器的基本结构如图 3.2 所示。探测器制备完成后沿垂直于波导轴向方向利用 SEM 对光电探测器进行观察,得到如图 4.1 所示的截面 SEM 图。

图 4.1 本文制备的波导集成型 PIN Ge 光电探测器截面 SEM 图(a)整体(b)Ge 区放大

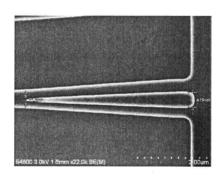

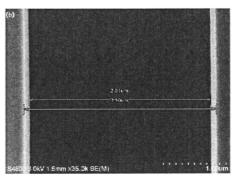

由第三章可知,Poly-Si Taper 是用于增强光波导与探测器间光学耦合;它是通过刻蚀 150nm 的 Poly-Si 形成的,其版图 PY 如图 4.2 所示,其结构尺寸与理论尺寸的偏差将对探测器的光响应度造成一定的影响。通过电子扫描显微镜观察 Poly-Si Taper 得到的表面与截面 SEM 图如图 4.3 与图 4.4 所示。注意图 4.4 是观察 PY 版测试区图形而非 Poly-Si Taper 得到的结果。从图中可以看出 Poly-Si Taper

两端的实际线宽分别为 72.2.nm、419nm 与设计值 120nm、1μm存在很大误差,二者的差值远远地超出了正常的工艺窗口(实际线宽应控制在设计线宽的±10%以内)。这是由于 Poly-Si Taper 的 120nm 的设计线宽远远地超过了光刻机的工艺能力。此外图 4.4 中可以看出,Poly-Si 的厚度很好的控制在了 150nm 左右,但是图形的侧壁并不十分陡直。

图 4.2 Poly-Si Taper 版图

图 4.3 Poly-Si Taper 表面 SEM 图

图 4.4 PY 版测试区图形(a)版图(b)中心位置截面 SEM 图(c)边缘位置截面 SEM 图

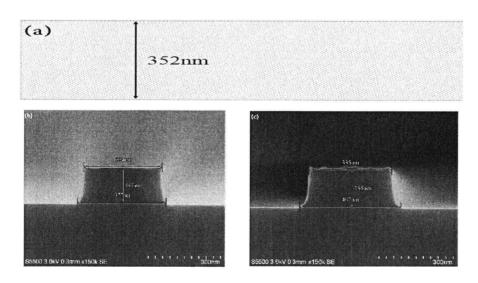

单模光波导芯层截面尺寸的理论设计值( $W_{WG} \times H_{WG}$ )为450nm  $\times$  220nm,而实际情况如图 4.5 所示。从图中可以发现晶圆片中心位置与边缘位置的波导截面

图 4.5 SOI 晶圆上不同位置处波导截面 SEM 图(a)中心位置(b)边缘位置

尺寸分别为434nm×208nm、439nm×213nm,二者均在工艺误差所允许的范围内。尽管 SOI 晶圆片顶层硅厚度的标称值为220nm,但实测值均偏小。这是由两个方面的因素造成的,一方面,SOI 晶圆片顶层 Si 厚度本身存在一定的误差,其次由第三章可知,Poly-Si Taper 刻蚀时的停止层热氧化SiO<sub>2</sub>的生长将消耗一定量的顶层 Si。此外,从图 4.5 中还可以注意到光波导的侧壁并不陡直与光滑。光波导的截面尺寸与理论尺寸的偏差与侧壁的粗糙程度都将影响到光波导的传输损耗。

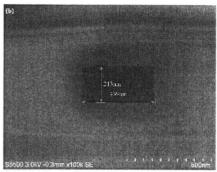

聚焦光栅是形成于光波导输入端 Taper 之上的,其占空比将影响光从光栅耦合到光波导的效率,而其刻蚀的深度将决定其反射特性。聚焦光栅的版图与 SEM 图分别如图 4.6 与图 4.7 所示。从图 4.7 (c)、(d)中可以看出,尽管与设计值存在差距,但是聚焦光栅的实际线宽被很好的控制在工艺误差范围以内。同时也可以很明显的看出,聚焦光栅的侧壁十分粗糙,这是由其弧状的布局引起的。

图 4.6 聚焦光栅版图

图 4.7 聚焦光栅形貌图(a)光学显微图(b)表面 SEM 图(整体)(c)表面 SEM 图(放大)(d)截面 SEM 图

Ge 的选择性外延是制备 Ge 光电探测器的最关键的工艺。受到负载效应的影响,在外延窗口的定义过程中以及 Ge CMP 过程中均存在刻蚀速率不均导致的外延窗口底部的 Si 的过刻蚀深度不一以及 Ge CMP 后 Ge 厚度不一;前者将影响到探测器的 Ge/Si 界面特性,而后者则将影响探测器的频率响应特性。Ge 外延窗口(仅以宽度为1μm、3μm及5μm的外延窗口为例)的形貌图如图 4.8 所示。该片在进行 PECVD SiO<sub>2</sub>膜减薄前,利用光学膜厚仪测得其膜厚的最大值、最小值以及均值分别为10316.88Å、9921.40Å及10119.72Å,由此可以初步判断出采用 PECVD 工艺淀积 SiO<sub>2</sub>厚膜的工艺均匀性良好。而在采用 CMP 工艺对该圆片进行持续时间为 132s 的研磨减薄后再次进行膜厚测量时发现该片的SiO<sub>2</sub>膜厚的最大值、最小值以及均值分别为5941.20Å、4575.63Å及5193.74Å。通过对比可以发现SiO<sub>2</sub>膜厚的 Range 值(最大膜厚值与最小膜厚值之差)由 CMP 前的395.48Å上升至 CMP 后的1365.39Å,这意味着采用 CMP 工艺对SiO<sub>2</sub>膜厚进行减薄的同时

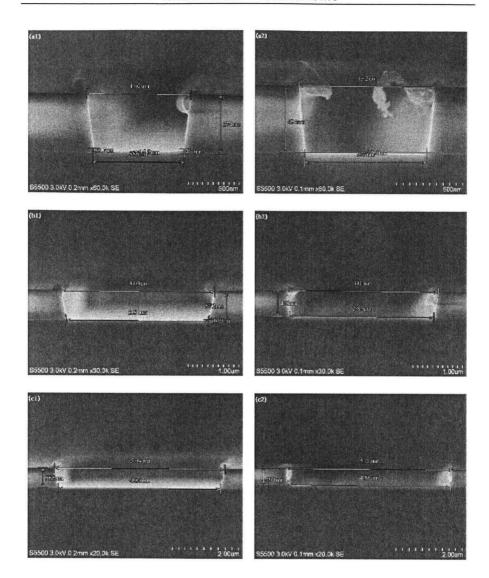

图 4.8 晶圆片中心与边缘位置处不同宽度的外延窗口形貌(a1) $W_{Ge}=1\mu m$ (中心) (a2) $W_{Ge}=1\mu m$ (边缘) (b1) $W_{Ge}=3\mu m$ (中心) (b2) $W_{Ge}=3\mu m$ (边缘) (c1) $W_{Ge}=5\mu m$ (中心) (a1) $W_{Ge}=5\mu m$ (边缘)

却使其厚度的均匀性变差,且在研磨的过程还发现采用 CMP 进行研磨减薄的时间越长研磨后的 $SiO_2$ 膜厚均匀性越差。从图 4.8 中可以发现(1)晶圆片中心位置的  $SiO_2$ 膜厚大于边缘位置,这与 $SiO_2$ 膜厚的测量结果一致(2)宽度为 $1\mu$ m的外延窗口 (欠刻蚀)刻蚀速率要低于 $3\mu$ m(过刻蚀)、 $5\mu$ m的窗口,这是因为前者暴露出的图形

面积明显小于后者因而刻蚀副产物在小窗口中被抽取的速率慢进而导致小窗口刻蚀速率偏慢。由此可知 CMP 工艺引入的差的 $SiO_2$ 膜厚均匀性以及刻蚀过程中的负载效应均使得刻蚀过程变得困难。

由第三章可知,完成外延窗口的刻蚀后,晶圆片必须经过彻底的清洗才能进入 RPCVD 设备中进行 Ge 的外延;若清洗结束过程进行的不够彻底那么很可能导致外延失败,如图 4.9 所示。从光学显微镜下可以明显地看出 Ge 的表面非常粗糙,从截面 SEM 图甚至可以看到 Ge/Si 界面处存在多处空洞。这可能是外延

图 4.9 Ge 外延前清洗不彻底导致的外延失败案例(a)光学显微图(b)截面 SEM 图

窗口的刻蚀过程中残留的一些聚合物在去胶清洗过程中未被完全除去所导致的。 因此在外延前的清洗后,需要利用 SEM 对外延窗口进行观察确保底部无残留物。 图 4.10 是 SOI 晶圆片的外延窗口(仅以 $W_{Ge}=3\mu m$ 的外延窗口为例)在彻底清洗 后的 SEM 观察图。从图中可以看出外延窗口的底部非常干净,外延窗口的线宽

图 4.10 晶圆上不同位置外延窗口清洗后的表面 SEM 图(a)中心(b)边缘

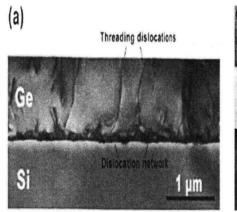

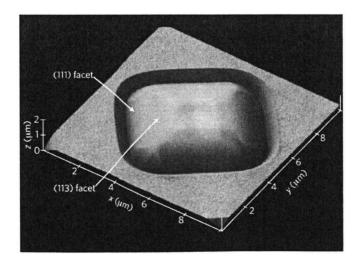

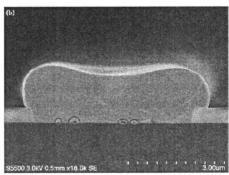

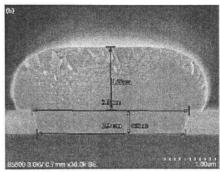

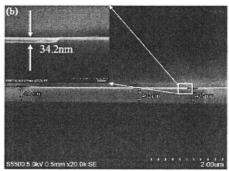

也在容许的误差范围内。在采用第三章所述的选择性外延工艺后,利用 SEM 和 TEM 对外延 Ge 区进行表征得到的如图 4.11、图 4.12 所示的结果。从图 4.11 中

图 4.11 15μm × 3μm窗口外延 Ge 形貌(a)光学显微(b)截面 SEM 图

可以看出, Ge 外延正常情况(外延窗口清洗干净彻底)下, Ge 在光学显微镜下看起来表面是十分光滑的且 SEM 截面图中 Ge/Si 界面也不会出现任何缝隙,这与

图 4.12 15μm × 2μm 窗口外延 Ge 的 TEM 图(a)整体(b)局部放大

图 4.9 形成十分鲜明的对比。Ge 外延生长后采用 TEM 对 Ge 层进行了表征,得到如图 4.12 所示的结果。从图 4.12 中可以看出,Ge 中位错几乎都被限制在了近90nm 厚的低温 Ge 层中,而高温 Ge 中的缺陷较少。在之后的 CMP 过程中,由于负载效应的存在,所以不同宽度的外延 Ge 区的研磨速率不一。15μm×5μm 窗口中外延 Ge 在 CMP 研磨 42s 之后的的截面形貌如图 4.13 所示。从图中可以

图 4.13 窗口中 Ge CMP 后形貌图(a)表面 SEM 图(b)截面 SEM 图

看出,Ge 出现了过磨,过磨量约为 34nm。因为进行 Ge CMP 工艺时设备不支持在线研磨终点监测,工艺过程中判断研磨终点采用的标准为:若同一位置处 Ge CMP 研磨前后在 SEM 顶视图中的 Ge 宽相同,则认定为到达研磨终点从而结束 CMP 过程;否则继续 CMP 过程,直到 Ge 宽相同为止。但是由图 4.13 可知,这种方法不可取而且极易造成大窗口内的 Ge 的过磨。

由第一章可知,尽管第一个三极管所使用的材料是 Ge,但是其在随后的不久便被 Si 所取代,其中一个非常重要的原因是 Ge 极易被氧化且氧化物的化学性质不稳定即GeO<sub>2</sub>不仅易溶于酸碱溶液甚至能溶于水。因为在 Ge 层离子注入后的去胶清洗以及 Ge 层接触孔刻蚀后的去胶清洗过程中所使用的清洗溶液均不能含有氧化性成分,否则极易造成 Ge 被腐蚀从而导致整个器件彻底失效。在制备 PIN Ge 光电探测器的第一次流片过程中,由于在 Ge 层离子注入后的去胶清洗过程中采用了一种代号为"SiGe Clean"(溶解有一定含量O<sub>3</sub>的稀释的 HCI 溶液)的溶液且 Ge 接触孔刻蚀后的去胶清洗过程中同样使用了具有较强氧化性的 DSP 溶液(稀释的H<sub>2</sub>SO<sub>2</sub>溶液与H<sub>2</sub>O<sub>2</sub>溶液的混合液),导致 Ge 被大量地腐蚀(如图 4.14 所示)最终使得整个器件失效。通过与图 4.1 对比并进行分析可知,在图 4.14 中 A 区(现被 TEOS SiO<sub>2</sub>填充)中的 Ge 是是被"SiGe Clean"溶液腐蚀,而 B 区(现为空洞)中的 Ge 则是被 DSP 溶液所腐蚀。

针对上述问题,本文对探测器制备过程中 Ge 的清洗工艺进行了优化改进,

图 4.14 Ge 被氧化性溶液腐蚀后的器件截面 SEM 图

采用稀释的 HF 溶液分别替代"SiGe Clean"溶液与 DSP 溶液对晶圆片进行去胶清洗最终得到的器件的形貌如图 4.1 所示,然而采用 HF 溶液进行去胶清洗时必须精确地控制清洗时间防止清洗过程中出现严重的横向腐蚀问题。

## 4.3 波导及光栅的光学损耗

本文所研究的波导集成型 PIN Ge 光电探测器的工作波长范围为 C 波段与 L 波段,而由作为第一章可知波导芯层的 Si 的光吸收截止波长为1.1μm左右,因而理论上 C 波段与 L 波段的光在 Si 光波导传播时不存在损耗。但事实并非如此,波导材料本身存在缺陷以及波导粗糙的表面会引入散射损耗,带间吸收与自由载流子吸收将导致吸收损耗,波导弯曲则会引入辐射损耗。在本文所研究的波导集成型光电探测器中,波导为直波导,如图 3.9 所示,故波导的辐射损耗可忽略不计。所以在研究中,光波导的传输损耗主要来自于波导的表面散射损耗以及吸收损耗。

输入耦合光栅是形成于波导 Taper 结构之上的周期性结构,如图 3.4 (d)所示。它能对波导的有效折射率起周期性调制作用,当相位匹配条件<sup>[59]</sup> 满足时,光能够从光纤中耦合到波导中。光栅的耦合效率(又称插损)定义<sup>[40]</sup> 为:

$$IL = 10 \log_{10}(P_{wg}/P_{fibre})$$

其中, $P_{fibre}$ 与 $P_{wg}$ 分别为光纤与光波导中基模所携带的能量。

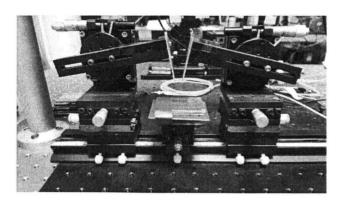

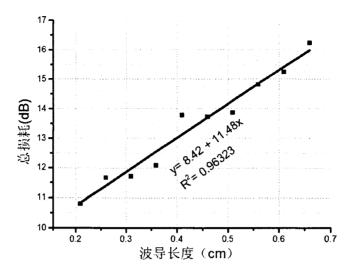

测试光波导损耗的方法包括截断法、法布里-珀罗腔共振法以及散射光法<sup>[59]</sup>。 采用截断法测量光波导的传输损耗时需要测量一组长度等量递增的波导阵列的 总损耗,包括光波导的传输损耗与光栅耦合损耗;因此只要作出总损耗随波导长 度的变化曲线(数据拟合为一不过原点的直线),则直线的斜率即为波导的传输损耗而纵轴截距即为光栅耦合损耗的二倍。本文采用的是截断法来测量光波导的传输损耗以及光栅的耦合损耗。测试结构版图如图 4.15 所示。测试结构中光波导的长度由最底部的2090μm以500μm为间隔增加到6590μm。采用的测试仪器有光谱仪(型号为 YOKOGAWA AQ6370D, 如图 4.16 所示)、可调谐激光器(YOKOGAWA AQ2200-136, 如图 4.17 所示),四维探针台(含光纤与偏振片,如图 4.18 所示),测量得到的波导损耗数据如表 4.1 所示,将 4.1 中数据进行线性拟合得到如图 4.19 所示曲线。

图 4.15 波导传输损耗与光栅耦合损耗测试结构版图

图 4.16 光谱仪 YOKOGAWA AQ6370D

图 4.17 可调谐激光器 YOKOGAWA AQ2200-136

图 4.18 四维探针台

由图 4-19 中可知,光波导的传输损耗高达11.48 dB/cm,而光栅的耦合损耗为4.21dB。尽管分析光波导的传输损耗与光栅耦合损耗偏大的原因需要对其做进一步的更加精微的结构表征,但是从 4.2 节中光波导与光栅的结构表征结果可以初步判定光波导损耗如此之大的主要原因光波导粗糙的侧壁,这一点可从图 4.5 中直观地看出。而图 4.7 (a)、(d)则直观地表明光栅耦合损耗偏大可能是由光栅侧壁及表面粗糙造成的。

表 4.1 不同长度波导的总损耗

| 波导长度/cm | 总损耗/dB |

|---------|--------|

| 0.2090  | 10.805 |

| 0.2590  | 11.681 |

| 0.3090  | 11.726 |

| 0.3590  | 12.093 |

| 0.4090  | 13.782 |

| 0.4590  | 13.728 |

| 0.5090  | 13.865 |

| 0.5590  | 14.820 |

| 0.6090  | 15.257 |

| 0.6590  | 16.244 |

图 4.19 波导总损耗随波导长度的变化曲线

## 4.4 探测器的光电性能测试

如第二章所述,表征光电探测器光电性能的主要参数有暗电流、光响应度以及频率响应;其中探测器的频率响应又可从两方面来看,其一是探测器自身的 3-dB 带宽,其二则是探测器在光通信链路中的数据传输速率。

探测器暗电流的大小将决定器件的静态功耗以及系统的噪声,光响应度则决定了探测器的灵敏度,而探测器的频率响应特性的优劣则是决定探测器能否应用于高速光收发系统标准。值得注意的是,探测器的暗电流高低对响应度及频率响应均具有十分重要的影响。

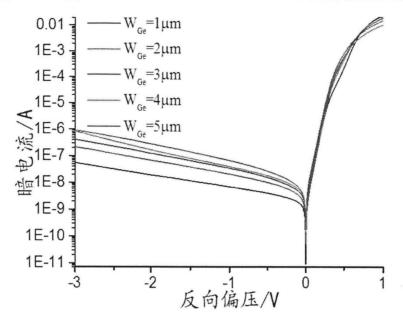

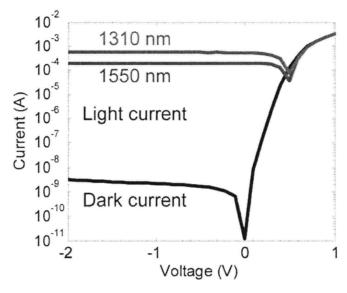

### 4.4.1 暗电流

探测器的暗电流测试所用的仪器是 Keithley 4200 半导体参数测试仪,测试需要在无光的条件下进行。测试时加载在探测器两端的电压从-3V(此时探测器处于反偏状态)以 0.01V 为扫描间距逐渐增加至正偏时的 1V,得到不同尺寸探测器的暗电流特性曲线,如图 4.20 所示。从图中可以看出探测器的整流特性良好,其暗电流随反偏压的增大而呈指数上升趋势。由第三章可知,由于 Ge 与 Si 之间存在高达 4.2%的晶格常数失配,所以无论采取哪种外延方法 Si 基上的 Ge 外延势必会在 Ge 层中引入大量的位错,这一点可以从图 4-13 中较为直观地看出,这些位错的存在会在 Ge 的禁带中引入缺陷能级。探测器工作在反偏状态下,外加电

场使得 Ge 的能带发生弯曲从而出现由缺陷引入的暗电流成分且其随外加电压的

图 4.20 不同尺寸探测器暗电流特性曲线

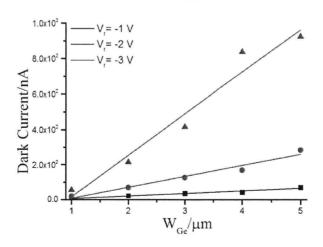

呈指数上升趋势。此外表 4-2 给出了典型偏压下不同尺寸探测器的暗电流数值,从表中可以看出,在- $1V\sim-3V$  的反偏状态下所有尺寸的探测器的暗电流均小于  $1\mu A$ ,这符合高速光电收发芯片对于探测器暗电流的要求。此外, $15\mu m \times 1\mu m$ 探

| 階电流/nA | -1 | -2  | -3  |

|--------|----|-----|-----|

| 1      | 7  | 20  | 55  |

| 2      | 22 | 70  | 215 |

| 3      | 37 | 127 | 415 |

| 4      | 42 | 169 | 838 |

| 5      | 71 | 283 | 924 |

表 4.2 典型偏压下不同尺寸探测器的暗电流

测器在-1V 反偏压下的暗电流低至 7nA,对应的暗电流密度约为47 mA/cm²,这一数值十分接近 IMEC<sup>[29]</sup> 的水平(IMEC 在 16 年报道的水平 PIN 结 Ge 光电探测器在-1V 反偏压下的暗电流密度约为43 mA/cm²)。然而,文献[29] 中文的探测器的暗电流特性,如图 4.21 所示,表明其暗电流在-1V~-2V 的反偏压范围内增长缓慢甚至趋于饱和,这反映出其很高的 Ge 外延生长质量。而对于本文的光电

探测器,当反偏压从-1V增加到-2V时,暗电流增长了近4倍,这表明我们在Ge的外延生长及后期Ge表面钝化工艺方面还有很大的改进空间。

图 4.21 IMEC 波导集成型 PIN Ge 光电探测器暗电流特性[29]

此外,从图 4.21 与表 4-2 中还可以看出,同等反偏压条件下,探测器的暗电流随着探测器的 Ge 区的宽度的增大而增大。为了进一步研究探测器暗电流与其结构尺寸的关系,对表 4-2 中给出的数据进行分析拟合得到图 4.22。由图 4.22

图 4.22 典型偏压下探测器暗电流随 Ge 区宽度的变化曲线

可知,在较低反偏压 $(-2 \text{ V} \leq \text{ V}_r \leq 0 \text{ V})$ 下,探测器的暗电流随探测器 Ge 区宽度的

增加而线性增加。此时,由式(2.1)可知,探测器的暗电流主要来自受体位错及缺陷密度影响的体暗电流;而当反向偏压增加至-3V时,暗电流与 Ge 区宽度之间依然总体上保持线性增长趋势但是已经出现偏离线性关系的趋势(曲线的线性拟合度由-1V、-2V偏下的高于 0.95 下降到-3V偏压下的不到 0.94),此时取决于表面态密度的表面暗电流开始变得不可忽略。

探测器的暗电流包括体暗电流与表面暗电流。本文在进行选择性 Ge 外延时,由于外延窗口是直接采用干法刻蚀完成的,过刻蚀导致外延窗口底部 Si 表面十分粗糙,这直接影响到外延 Ge 的质量。采用干法刻蚀与湿法腐蚀相结合的方法可以有效地克服这一问题。此外,通过改善 CMP 后 Ge 表面的钝化条件则可以抑制器件的表面暗电流<sup>[60-62]</sup>。

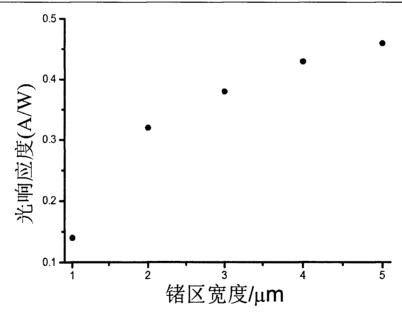

## 4.4.2 光响应度

由式(2.2)可知探测器的光响应度定义为探测器输出的光电流与接收的光功率之比。其中,探测器的输出的光电流是指实测得到的总光电流减去相同偏压条件下的暗电流而得的净光电流,而探测器接收的光功率则需要扣除测试链路本身的固有损耗、光栅的耦合损耗以及光波导的传输损耗。

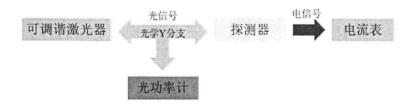

测试探测器的光响应度的基本原理如图 4.23 所示。从可调谐激光器输出的 红外光信号被光学 Y 分支器分成强度相等的两束,其中一束作为参考直接被光 功率计测量,另一束则通过本文所研究的光电探测器转换成光电流之后直接由电流表读出。

图 4.23 探测器光响应度测试原理框图

实际测试时,可调谐激光器输入的光信号的波长为 1530nm,输出的光功率为 0.332dBm 即光功率计的读数为 0.3dBm,于是达到探测器输入光栅的光功率 也为 0.3dBm 即约为 1.071mW。本文所研究的波导集成型垂直 PIN Ge 光电探测

器中波导长度约为1545 $\mu$ m,则光波导的传输损耗约为 1.77dB;考虑到测试时光纤的端面反射(引入的损耗约为 1dB),总的损耗约为 6.98dB。那么入射到探测器一侧的实际光功率约为 0.215 $\mu$ W。表 4.3 中给出了在-2V 反偏压下 1530 $\mu$ m 波长处测得的不同尺寸的探测器的光电流大小以及换算得到的光响应度值,表中 $\mu$ 0为实际测试时的总光电流, $\mu$ 0为探测器的外量子效率。不同尺寸探测器响应度随其 Ge 区宽度的变化趋势如图 4.24 所示。

| $W_{Ge}/\mu m$ | $l_{\rm o}/{\rm mA}$ | I <sub>dark</sub> /nA | R(A/W) | $\eta_e$ |

|----------------|----------------------|-----------------------|--------|----------|

| 1              | 0.03                 | 20                    | 0.14   | 0.114    |

| 2              | 0.07                 | 70                    | 0.33   | 0.268    |

| 3              | 0.083                | 127                   | 0.39   | 0.316    |

| 4              | 0.093                | 169                   | 0.43   | 0.349    |

| 5              | 0.1                  | 283                   | 0.47   | 0.381    |

表 4.3 不同尺寸探测器的光响应度(@-2V@1530nm)

图 4.24 探测器响应度随 Ge 宽度的变化趋势(@-2V@1530nm)

从表 4.3 与图 4.24 中均可以看出,探测器的光响应度随着 Ge 区宽度的增加而增加,这是因为当 Ge 区的宽度增加时,通过倏逝耦合进入 Ge 区后的光被束缚在 Ge 层中的时间增加,因此 Ge 吸收的光能量也会相应地增加因而探测器的

光响应度上升。从探测器的材料来看,由式(2.9)可知,材料中的位错缺陷会导致内量子效率 $\eta_i$ 的下降从而劣化探测器的光响应度特性,这是导致探测器光响应度总体偏低的主要原因;从探测器的结构看,由图 4.3 可知,用于增强波导与探测器之间光耦合效率的 Poly-Si Taper 由于光刻工艺加工能力的问题而未能实现,所这也是一个导致光响应度偏低的重要原因。

光电探测器与波导集成的出发点就是为了解除传统垂直面入射光电探测器的光响应度与带宽之间的相互制约关系以期望在获得高带宽的同时提高探测器的光响应度。在此基础之上研究人员提出了诸如引入谐振腔以及布拉格反射镜等来进一步增强探测器光响应度的方法。而最为重要的一点是通过不断的改善 Ge 的异质外延质量来提高其内量子效率使其尽可能的接近 1 从而提高探测器的响应度。

### 4.4.3 3-dB 带宽及眼图

探测器的带宽即 3-dB 带宽是衡量探测器响应光信号快慢程度重要物理量, 其取决于 Ge 层中光生载流子的输运时间以及 RC 时间常数。实际测试时,3-dB 带宽是通过测量探测器的 S 参数矩阵

$$S = \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix}$$

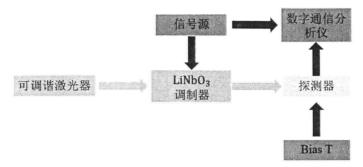

得到的。其中 $s_{11}$ 双端口网络输入端的反射系数, $s_{11}$ 为反向传输系数, $s_{21}$ 为正向传输系数, $s_{22}$ 为输出端的反射系数。探测器的 3-dB 带宽即为 $s_{21}$ 相对于初值衰减 3dB 时所对应的频率值。测量探测器 S 参数矩阵所需要的实验设备包括可调谐激光器、商用LiNbO<sub>3</sub>调制器、矢量网络分析仪以及 T 型偏置器(Bias T)等。测试的原理框图如图 4.25 所示。

图 4.25 探测器 S 参数矩阵测试原理框图

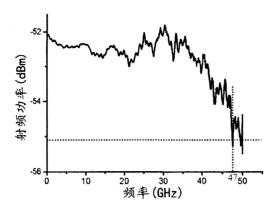

图 4.26 给出了 $15\mu m \times 4\mu m$ 探测器的 S 参数矩阵中 $s_{21}$ 随频率的变化关系

图 4.26 探测器的S21参数随频率的变化关系曲线(@-2V@1530nm)

曲线,由该图可知该探测器在-2V偏压下1530nm波长处的3-dB带宽高达47GHz。由式(2.10),降低探测器 Ge 的厚度可以减小载流子的渡越时间从而改善其频率响应特性,但由式(2.11)可知,Ge 厚度的减薄必将增大探测器的结电容劣化其影响频率响应特性。这种矛盾在垂直 PIN 结构的光电探测器表现的尤为突出而水平 PIN 结构的光电探测器则几乎不受其影响,这正是文献[5]中在 Ge 区厚度仅为160nm的情况下带宽仍高达67GHz的原因。此外,通过减少探测器的结面积即减小探测器 Ge 区的宽度或者长度可以减少 RC 时间常数从而提高带宽,但是这是以牺牲探测器的光响应度为代价的。因此,在提高探测器性能的同时,带宽应与其他参数折中考虑。

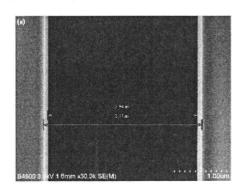

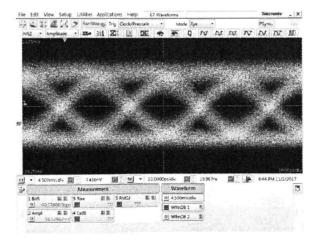

探测器的眼图是评估探测器在数字传输系统中数据处理能力的一种十分简便但有效的手段。测试系统通过产生等速率的伪随机 0、1 图案来构建眼图,当这些脉冲图案同时叠加在一起时形成了眼图图案。眼图中含有十分丰富的信息,可以很容易地从中获取数字通信时的码间串扰及系统噪声。通过压力眼图测试可以预测探测器能正常工作的最大速率范围。探测器眼图测试的原理如图 4.27 所示。探测器的眼图测试结果如图 4.28、图 4.29 所示,测试结果表明15μm × 3μm 及15μm × 4μm的两种尺寸的探测器在-2V 反偏压下的数据传输速率均达到了40Gpbs,完全具备了应用于 100Gbps 光互连与光通信系统的能力。从图中可知系统的噪声比较大,系统的噪声的主要来源为测试链路中前置放大器 TIA 的电

阻热噪声及探测器本身的暗电流。

图 4.27 探测器眼图测试原理框图(@-2V@1530nm)

图 4.28 15μm×3μm探测器眼图(@-2V@1530nm)

图 4.29 15μm×4μm探测器眼图(@-2V@1530nm)

# 4.5 小结

本章对本文所制备的波导集成型 PIN Ge 光电探测器的结构进行表征,通过对表征结果的分析指出了探测器制备过程中存在的一些问题并给出了合理的解释。结合 SEM 及 TEM 分析数据重点对 Ge 的选择性外延前后的相关联工艺上出现的一些问题的成因进行了分析同时给出了相关的解决方案。

对探测器的光电性能进行了较为全面的测试,结合探测器器件的结构表征数据详细地分析了工艺参数对波导的光传输性能、光栅的光耦合性能的影响。此外全面地分析了探测器结构参数及工艺参数对暗电流的影响,同时点明了进一步优化的方向。对探测器的光响应度及频率响应做了简要分析,结果表明探测器的暗电流对光响应度及频率响应均有重要影响。

# 第5章 总结与展望

# 5.1 本文工作的总结

本文在系统调研波导集成型光电探测器的基础上开展了对 SOI 基波导集成型垂直 PIN Ge 光电探测器的研究。主要的研究内容如下

- (1)基于硅基光子技术高速发展的大背景,充分而系统地调研了近年来国内外在 Si 基波导集成型光电探测器领域的研究进展,充分认识到波导集成型光电探测器发展所面的两大难题; 高质量的异质外延及探测器与波导的高效集成。

- (2)在系统学习光电探测器基本工作原理的基础上,对包括暗电流、光响应度及频率响应在内的探测器的主要性能参数展开详细的讨论和分析。经过系统地分析发现垂直面入射探测器的光响应度与带宽存在相互制约的关系,而波导集成型光电探测器中波导的引入能有效的克服上述缺点。

- (3)利用中科院微电子所 8 英寸标准 CMOS 工艺线,采用低-高温生长与选择性外延相结合的方法在 SOI 衬底上生长出了较高质量的 Ge 膜,并以此为基础制备出了高性能的波导集成型垂直 PIN Ge 光电探测器。此外,通过工艺优化解决了 Ge 的选择性外延工艺模块中出现的 Ge 被腐蚀的问题,最终使得制备出探测器得以正常工作。

- (4)主要利用了 SEM 及 TEM 对探测器的器件结构进行表征分析。对探测器的光电性能进行了最基本的测试,包括暗暗电流测试、光响应度测试以及频率响应特性测试。测试结果表明,由于所设计的 Poly-Si Taper 的最小尺寸超出了光刻机的工艺能力,所以最终这一结构没能正常实现,这可能是导致探测器光响应度普遍偏低的一个重要原因。光波导的传输损耗高达11.48 dB/cm,导致这一问题的最直接可能原因是光波导侧壁的粗糙度过大。尽管光电探测器的暗电流在正常工作状态下随反偏压呈指数趋势快速上升,然而所有尺寸的探测器在-IV~-3V偏压下的暗电流均达到了应用于高速光电收发芯片的要求,15µm×1µm探测器在-IV 反偏压下的暗电流仅为7nA,这已经和国际先进水平处于同一数量级。然而在反偏压下的指数增长趋势以及 Ge 的 TEM 表征结果然表明外延 Ge 的质量还

有待于进一步的提高。最后对探测器的频率响应特性测试的结果表明,15μm×4μm探测器在-2V 反偏压 1530nm 波长处的 3-dB 带宽高达 47GHz,数字通信测试表明该探测器完全能够满足 100Gpbs 的光通信与光互连系统对于探测器带宽的要求。

# 5.2 展望

通过本文对波导集成型 PIN Ge 光电探测器开展的研究,结合实际的探测器制备工过程中遇到的一些问题,本文认为可以在今后围绕以下几个方面对探测的性能进行优化:

### 1.探测器的结构优化

(1)探测器版图: 在探测器的制备过程中,尤其是在选择性外延的窗口的定义过程中需要兼顾不同宽度的外延窗口,而刻蚀过程中的负载效应不可避免,因此后续的流片过程中建议在 Ge 版这一层加入 Dummy 结构以减轻负载效应带来的工艺压力; 此外,若在 Ge 版这一层中加入 Dummy 结构也能在 CMP 这一版的工艺中有效的抑制负载效应带来的负面影响。

(2)对 Poly-Si Taper 结构的光耦合增强效果进行仿真, 重新定义其结构尺寸使 其能够用现有的标准 CMOS 工艺加工。

2.Ge 的外延工艺模块的优化:

从第三章可知,只采用干法刻蚀工艺定义 Ge 的外延窗口会导致窗口底部的 Si 变得粗糙,这将极大地影响外延 Ge 的质量,从而增大探测器的暗电流。目前 作者等人提出了两种优化方案:(1)采用干法刻蚀与湿法腐蚀相结合的方法制备外延窗口(2)只采用干法刻蚀制备外延窗口,但是在干法刻蚀后通过热氧化的方法来降低外延窗口底部的粗糙度从而达到提升外延质量的目的。

此外,从第三章及相关文献可知,采用选择性外延生长 Ge 时,高温 Ge 层中的穿透位错密度通常比低温 Ge 层低 2~3 个数量级;这也就意味着高温 Ge 层中的位错密度随着高温 Ge 层的厚度的增加而逐渐下降,然而由第二章可知,Ge 层厚度过大将影响探测器的频率响应特性。结合 CMOS 器件发展过程中的源漏提升技术,作者等人提出了一种的新型波导集成型垂直 PIN Ge 光电探测器<sup>[63]</sup>。

该探测器与目前文献中报道的各类 Ge 光电探测器的一个最显著的区别是 Ge 是外延生长在衬底 Si 之上而非顶层 Si 之上。

# 此页不缺内容

# 参考文献

- [1] Bardeen J, Brattain W H. The Transistor, A Semiconductor Triode [J]. Physical Review, 1948, 74(1):29-30.

- [2] Noyce R N. Semiconductor Device-and-Lead Structure: U.S. [P] 2981877.1961.

- [3] 酷 睿 i7- 百 度 百 科 [EB/OL].[2017-3-10] https://baike.baidu.com/item/ 酷 睿 i7/1347847?fr=aladdin#2 5.

- [4] Wang J. Fabrication and characterization of germanium photodetectors [D]. National University of Singapore, 2011.

- [5] Michel J, Liu J F, Ahn D H, et al. Advances in fully CMOS integrated photonic devices[C]. Silicon Photonics II. International Society for Optics and Photonics, 2007:64770P-64770P-11.

- [6] Liu J, Beals M, Pomerene A, et al. Waveguide-integrated, ultralow-energy GeSi electro-absorption modulators[J]. Nature Photonics, 2008, 2(7):433-437.

- [7] Liu J, Sun X, Camacho-Aguilera R, et al. Ge-on-Si laser operating at room temperature [J]. Optics Letters, 2010, 35(5):679-81.

- [8] Colace L, Masini G, Assanto G, et al. Efficient high-speed near-infrared Ge photodetectors integrated on Si substrates[J]. Applied Physics Letters, 2000, 76(10):1231-1233.

- [9] 李冲.高性能Ge/Si长波长光电探测器的研究[D]. 中科院半导体研究所,2014:16-19.

- [10] Luryi S, Kastalsky A, Bean J C. New infrared detector on a silicon chip [J]. Electron Devices IEEE Transactions on, 1984, 31(9):1135-1139.

- [11] Samavedam S B, Currie M T, Langdo T A, et al. High-quality germanium photodiodes integrated on silicon substrates using optimized relaxed graded buffers [J]. Applied Physics Letters, 1998, 73(15):2125-2127.

- [12] Dosunmu O I, Cannon D D, Emsley M K, et al. Resonant Cavity Enhanced Ge Photodetectors for 1550 nm Operation on Reflecting Si Substrates [J]. IEEE JOURNAL OF SELECTED TOPICS IN QUANTUM ELECTRONICS, 2004, 10(4):694-699.

- [13] Suh D, Kim S, Joo J, et al. 36-GHz High-Responsivity Ge Photodetectors Grown by RPCVD[J]. IEEE Photonics Technology Letters, 2009, 21(10):672-674.

- [14] Suh D, Kim S, Joo J, et al. 35 GHz Ge p-i-n photodetectors implemented using RPCVD[C].IEEE International Conference on Group IV Photonics. 2008:191-193.

- [15] Xue C, Xue H, Cheng B, et al. 1×4 Ge-on-SOI PIN Photodetector Array for Parallel Optical Interconnects[J]. Journal of Lightwave Technology, 2009, 27(24):5687-5689.

- [16] Zhou Z, He J, Wang R, et al. Normal incidence p—i—n Ge heterojunction photodiodes on Si substrate grown by ultrahigh vacuum chemical vapor deposition[J]. Optics Communications, 2010, 283(18):3404-3407.

- [17] Roucka R, Mathews J, Weng C, et al. High-Performance Near-IR Photodiodes: A Novel

- Chemistry-Based Approach to Ge and Ge-Sn Devices Integrated on Silicon[J]. IEEE Journal of Quantum Electronics, 2011, 47(2):213-222.

- [18] Kim I G, Jang KS, Joo J, et al. High-performance photoreceivers based on vertical-illumination type Ge-on-Si photodetectors operating up to 43 Gb/s at  $\lambda$ ~1550nm.[J]. Optics Express, 2013, 21(25):30718-25.

- [19] Jang K S, Joo J, Kim T, et al. A CWDM photoreceiver module for 10 Gb/s x 4ch interconnection based on a vertical-illumination-type Ge-on-Si photodetectors and a silicabased AWG[J]. Proceedings of SPIE - The International Society for Optical Engineering, 2015, 9368:93680C-93680C-6.

- [20] Liu Z, Yang F, Wu W, et al. 48 GHz high-performance Ge-on-SOI photodetector with zero-bias 40 Gbps grown by selective epitaxial growth[J]. Journal of Lightwave Technology, 2017, PP(99):1-1.

- [21] Stillman G E, Wolfe C M, Melngailis I. Monolithic integrated In\_x Ga\_(1-x) As Schottky-barrier waveguide photodetector [J]. Applied Physics Letters, 1974, 25(1):36-38.

- [22] Masini G, Colace L, Assanto G. Near-infrared waveguide photodetectors based on polycrystalline Ge on silicon-on-insulator substrates[J]. Optical Materials, 2001, 17(1):243-246.

- [23] Liu J F, Ahn K Y, Hong C Y, et al. Waveguide Integrated Ge p-i-n Photodetectors on a Silicon-on-Insulator Platform[C]. Optics Valley of China International Symposium on Optoelectronics. IEEE. 2006:1-4.

- [24] Ahn D, Hong C, Liu J. F., et al. High performance, waveguide integrated Ge photodetectors[J]. Optics Express, 2007, 15(7):3916-21.

- [25] Yin T, Cohen R, Morse M M, et al. 31 GHz Ge n-i-p waveguide photodetectors on Silicon-on-Insulator substrate[J]. Optics Express, 2007, 15(21):13965-71.

- [26] Masini G, Capellini G, Witzens J, et al. A 1550nm, 10Gbps monolithic optical receiver in 130nm CMOS with integrated Ge waveguide photodetector[C]. IEEE International Conference on Group IV Photonics. IEEE, 2007:1-3.

- [27] Derose C T, Trotter D C, Zortman W A, et al. Ultra compact 45 GHz CMOS compatible Germanium waveguide photodiode with low dark current[J]. Optics Express, 2011, 19(25):24897.

- [28] Vivien L, Polzer A, Marrismorini D, et al. Zero-bias 40Gbit/s germanium waveguide photodetector on silicon.[J]. Optics Express, 2012, 20(2):1096-101.

- [29] Chen H, Verheyen P, De H P, et al. -1 V bias 67 GHz bandwidth Si-contacted germanium waveguide p-i-n photodetector for optical links at 56 Gbps and beyond[J]. Optics Express, 2016, 24(5):4622.

- [30] SiFotonics inc.硅光集成技术进步显著一SiFotonics 推出100G/200G全集成相干发射接收 芯片[EB/OL].http://sifotonics.com/index.php?m=default.news\_content&aid=4&bid=99.

- [31] Wang J, Loh W Y, Chua K T, et al. Low-Voltage High-Speed (18 GHz/1 V) Evanescent-Coupled Thin-Film-Ge Lateral PIN Photodetectors Integrated on Si Waveguide[J]. IEEE Photonics Technology Letters, 2008, 20(17):1485-1487.

- [32] Osmond J, Vivien L, Fédéli J M, et al. Ge-on-silicon waveguide photodetectors for optical telecommunications[J]. Proceedings of SPIE The International Society for Optical Engineering, 2009, 7366(1).

- [33] Feng D, Liao S, Dong P, et al. Horizontal p-i-n high-speed Ge waveguide detector on large cross-section SOI waveguide[C]. Optical Fiber Communication. IEEE, 2010:1-3.

- [34] Vivien L, Virot L, Marrismorini D, et al. 40Gbit/s germanium waveguide photodiode[C].Optical Fiber Communication Conference and Exposition and the National Fiber Optic Engineers Conference. IEEE, 2013:1-3.

- [35] Fujikata J, Miura M, Noguchi M, et al. (Invited) Si Waveguide-Integrated High-Speed Ge Photodetector[J]. Ecs Transactions, 2014, 64(6):723-727.

- [36] Chen H T, Verheyen P, Heyn P D, et al. High-Responsivity Low-Voltage 28-Gb/s Ge p-i-n Photodetector With Silicon Contacts[J]. Journal of Lightwave Technology, 2015, 33(4):820-824.

- [37] Virot L, Benedikovic D, Szelag B, et al. Integrated waveguide PIN photodiodes exploiting lateral Si/Ge/Si heterojunction.[J]. Optics Express, 2017, 25(16):19487-19496.

- [38] 刘道群, 李志华, 唐波, 等. 高性能波导集成型锗pin光电探测器的制备 [J].2018 55(5):305-310.

- [39] Kasap S O. 光电子学与光子学-原理与实践[M]. 北京: 电子工业出版社, 2015.

- [40] Chrostowski L, Hochberg M. Silicon Photonics Design from Device to System [M]. Cambridge: Cambridge University,2015.

- [41] Neamen D. A. Semiconductor Physics and Devices Basic Principles [M]. 赵毅强等译, 北京: 电子工业出版, 2013: 159-162.

- [42] Dilello N A, Johnstone D K, Hoyt J L. Characterization of dark current in Ge-on-Si photodiodes[J]. Journal of Applied Physics, 2012, 112(5):054506.

- [43] Takenaka M, Morii K, Sugiyama M, et al. Dark current reduction of Ge photodetector by GeO<sub>2</sub>-surface passivation and gas-phase doping [J]. Optics Express, 2012, 20(8):8718-8725.

- [44] 余金中. 半导体光电子技术 [M].北京: 化学工业出版社 (2003).

- [45] 施敏, 伍国钰.半导体器件物理[M].西安: 西安交通大学出版社, 2008: 508-511.

- [46] Xiao H. Introduction to Semiconductor Manufacturing Technology [M]. Washington: SPIE Press, 2012: 24.

- [47] Ye H, Yu J. Z. Germanium epitaxy on Silicon [J] Science & Technology of Advanced Materials, 2014, 15(2):02461-1-02461-8.

- [48] Wong L H, Liu J P, Romanato F, et al. Strain relaxation mechanism in a reverse compositionally graded SiGe heterostructure [J]. Applied Physics Letters, 2007, 90(6):

- 061913-061913-3.

- [49] Campbell S. A. 微纳尺度制造工程 [M]. 严利人等译. 北京: 电子工业出版社, 2011: 22.

- [50] Huangfu Y, Zhan W, Hong X, et al. Heteroepitaxy of Ge on Si(001) with pits and windows transferred from free-standing porous alumina mask.[J]. Nanotechnology, 2013, 24(18):185302.

- [51] Li Q, Jiang Y B, Xu H, et al. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO<sub>2</sub>[J]. Applied Physics Letters, 2004, 85(11):1928-1930.

- [52] Liu J, Camacho-Aguilera R, Bessette J T, et al. Ge-on-Si optoelectronics[J]. Thin Solid Films, 2012, 520(8):3354-3360.

- [53] Michel J, Liu J, Kimerling L C. High-performance Ge-on-Si photodetectors [J]. Nature Photonics, 2010, 4(8):527-534.

- [54] Yin T, Cohen R, Morse M M, et al. 31GHz Ge n-i-p waveguide photodetectors on Silicon-on-Insulator substrate [J]. Optics Express, 2007, 15(21):13965-13971.

- [55] Dimoulas A, Tsipas P, Sotiropoulos A, et al. Fermi-level pinning and charge neutrality level in germanium [J]. Applied Physics Letters, 2006, 89(25):1-33.

- [56] 柯星星. 基于CMOS工艺的Ge p-i-n 光电探测器[D]. 中国科学院大学, 2015: 25-35.

- [57] 吴细鹏. 用于CMOS硅光子集成的Ge光电探测器的研究[D]. 贵州大学, 2017: 9-36.

- [58] 吴细鹏, 王桂磊, 李志华等. 硅基锗薄膜的选择性外延生长[J]. 微纳电子技术, 2017, 54(2):136-140

- [59] Graham T. R., Andrew P. K. Silicon Photonics: an introduction [M]. England: John Wiley & Sons, Ltd: 2004.

- [60] Kang J, Zhang R, Takenaka M, et al. Suppression of dark current in GeO<sub>x</sub>-passivated germanium metal-semiconductor-metal photodetector by plasma post-oxidation [J]. Optics Express, 2015, 23(13):16967-16976.

- [61] Takenaka M, Morii K, Sugiyama M, et al. Dark current reduction of Ge photodetector by GeO<sub>2</sub>-surface passivation and gas-phase doping [J]. Optics Express, 2012, 20(8):8718-8725.

- [62] Weber J R, Janotti A, Rinke P, et al. Dangling-bond defects and hydrogen passivation in germanium[J]. Applied Physics Letters, 2007, 91(14):473-766.

- [63] 刘道群, 李志华, 唐波等. 光电探测器: 中国, 201810162647.2[P].2018-02-27.

# 致谢

硕士研究生 3 年一晃而过, 我依然忘不了 2015 年入学以及 2016 年回所时的情景。

3年来,我经历了很多,懂得了很多。首先我要感谢我的导师-李志华研究员,他始终以一种谦逊严谨的科研态度影响着我;他始终是那么的平易近人,无论我遇到什么问题都可向他倾诉一番。如果说李志华研究员向我传递的是一种认真负责的学习与科研态度,那么闫江研究员则更多地在思维方法与为人之道上给予我颇多启示,而这些指点无疑会给我今后的人生带来诸多益处;借此机会,我想向闫江研究员表示衷心的感谢。

"你这一生过的太顺利了,高考一次成功,考研一次成功,……,要提高自己的心理素质,……"。每当想起余金中研究员,这些他曾经对我的谆谆教诲总是浮现于脑海。余金中研究员虽已入古稀之年,但是他对科研的热爱与执着深深地感染着我。感谢余金中教授对我不倦的教诲,他对国势的关心深深地打动了我。我始终能从他的一言一行中深刻地感受到一个优秀共产党员对于祖国的热爱以及报效祖国的满腔热情。

感谢课题组唐波老师、张鹏老师及李彬老师在流片以及论文撰写期间提供的诸多帮助。感谢师兄吴细鹏,他使我了解并熟悉 CMOS 工艺流程。感谢中科院 微电子研究所 8 英寸 CMOS 工艺线的全体工程师及操作员,没有他们的协助,流片工作不可能顺利完成。感谢中科院半导体所李智勇研究员与武汉邮电科学研究院的肖希、王磊博士,他们在器件测试方面给予了很大帮助。

最后,我想感谢我父母、妹妹及女朋友在攻读硕士学位期间给予我的精神上及物质上的支持,他们一贯的理解与支持是我在科研道路上不断前行的不竭动力。

刘道群

2018年6月

# 作者简历及攻读学位期间发表的学术论文与研究成果

# 作者简历:

2011 年 9 月—2015 年 7 月,在合肥工业大学电子科学与应用物理学院获得微电子学理学学士学位。

# 已发表的学术论文:

一作论文:

[1] **刘道群**,李志华,冯俊波等. 高性能波导集成型锗 pin 光电探测器的制备[J].微纳电子技术,2018.

### 合作论文:

[1] Zhihua Li, Jiang Yan, **Daoqun Liu**(第六), et al. Silicon photonics process development based on a 200-mm CMOS platform[C]. SPIE/COS Photonics Asia, 2016.

# 申请或已获得的专利:

刘道群, 李志华, 唐波等. 光电探测器(专利号: 201810162647.2)(申请受理中)