我国数字频率合成芯片获突破进展 中国大陆首篇芯片研发论文在国际学术界产生影响

时间:2005-08-19

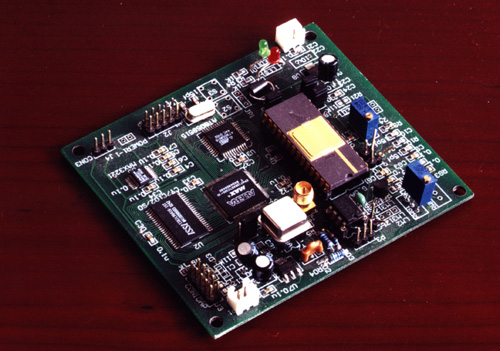

近日,中国科学院半导体研究所科研人员在新型高速直接数字数字频率合成(DDS)芯片研制中取得突破性进展,采用0.35微米(mm)常规互补金属氧化物半导体电路(CMOS)工艺,研制出合成时钟频率达2千兆赫兹(GHz)新一代不需要只读存储器的低功耗直接数字频率合成(ROM-LESS DDS)高速芯片。目前,这种CMOS DDS结构方式的芯片速度指标处于国际同类芯片领先地位,国际上之前报道类似芯片的合成时钟频率仅为1.2千兆赫兹。

半导体所的此项成果所撰写的学术论文被国际电气电子工程师学会(IEEE)电路与系统的顶级学术会议IEEE ISCAS2005录用并邀请在分会作报告。与此项研发工作的同时,半导体所有关科研人员还提出并流片验证了一种新型融入Σ/Δ技术的DDS芯片,这一原始性集成创新技术工作所撰写的学术论文作为中国大陆首篇被国际报道芯片研发前沿和最高技术水平的权威学术两大年会之一的“国际电气电子工程师学会(IEEE)超大规模集成电路(VLSI)2005年会”录用并邀请为分会作报告。上述两项研究报告在国际顶级学术会议宣讲后,与会者反响热烈。其意义不仅实现了中国大陆在IEEE VLSI学术会议上论文零的突破,也表明中国在国际信息产业界地位的提高。

随着全球信息化的不断深入和信息容量的增加,频率参量作为信息的载体,在通信领域有着极其重要的应用,其研究具有重要意义。频率合成的思想源于上世纪七十年代初,经历了三代发展历程。第一代采用电容、电感直接合成,存在体积大,稳定性差的弱点;第二代采用锁相环方式的闭环合成,性能稳定,体积小,但频率改变的稳定时间较长;第三代采用高性能数字模拟转换器(D/A转换器)加相位存储器、相位累加器等构成直接数字频率合成的方法,是上世纪九十年代后出现的新一代频率合成方式,其特点是保持了锁相环的优点外,频率改变稳定时间快,是高速跳频通信的首选方式式但常规直接数字频率合成由于采用只读存储器来寄存相位信息息芯片功耗较大。本世纪初出现的融入算法的非线性数字模拟转换器结合相位累加器的方式实现了新一代不需要只读存储器的直接数字频率合成(ROM-LESS的DDS)方式,降低了电路功耗,是直接数字频率合成中最前沿的技术。

中国科学院半导体研究所半导体神经网络及模糊逻辑高速电路实验室的科研人员基于长期积累的电路超高速工作芯片设计及高速数字模拟转换器芯片设计两项技术,并结合专为直接数字频率合成开发的算法,在目前性/价比较高的0.35微米常规互补金属氧化物半导体电路工艺平台上,采用电流型逻辑电路结构及流水线的系统结构方式实现了2千兆核资的时钟合成,试验流片后的芯片测试证实了设计的正确性,证明了研发人员掌握了当今世界在该领域最前沿的技术。值得一提的是,这种方式的实现,意味着该实验室目前已经具备了在0.35微米常规互补金属氧化物半导体电路工艺上设计2千兆赫兹的高速数字模拟转换器的能力,另一方面若采用尺寸更小的更为先进的制作工艺来设计制作直接数字频率(DDS)芯片,合成频率将会更高。

常规直接数字频率合成(DDS)方法的优点是合成频率精确,合成速度快。缺点是,由于合成中采用不同的脉幅信号拼接而成,因此,合成信号存在截断噪声,影响信号的分辨率。

半导体所科研人员利用实验室研发的数字模拟转换器集成电路(DAC IP)硬核,提出结合Σ/Δ技术,将截断噪声进行频谱搬移,研发新型高分辨率直接频率合成芯片。本工作由产生思想到提出算法,进而开展系统仿真及电路仿真设计,到实际芯片设计,并经芯片代加工流片及测试分析,完整地和无可挑剔地证明了新型直接数字频率合成(DDS)芯片的准确性。这是世界上首次完整地开展此方案的研究工作。新方案的实现,意味着直接数字频率合成在实现相同精度下,采用Σ/Δ技术后,可以降低数字模拟转换器的分辨率要求。而数字模拟转换器在直接数字频率合成芯片中所占面积最大,这又意味着在相同参数指标下,新技术方案在系统集成中可以使芯片面积大大缩小,因此具有重要的实用价值,受到IEEE VLSI2005与会者的高度重视和热烈欢迎。大会后经评选,大会主席已来函特邀该研究论文作为国际电气电子工程师学会固体电路分会权威杂志-IEEE JSSC专刊学术论文发表。

上一篇:第十五届中国神经网络大会(CNNC2006)在哈尔滨召开

下一篇:无