Jinmin Li G. Q. Zhang *Editors*

# Light-Emitting Diodes

Materials, Processes, Devices and Applications

# **Solid State Lighting Technology and Application Series**

Volume 4

#### **Series Editors**

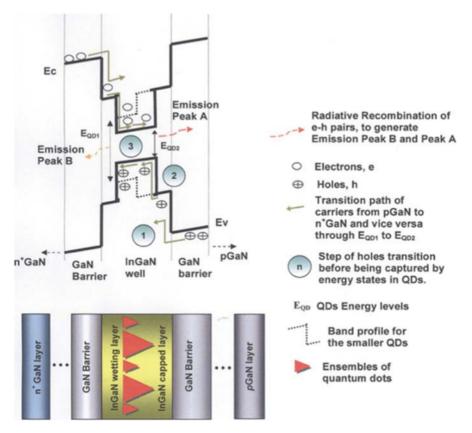

Guo Qi Zhang, Eindhoven, The Netherlands Wu Ling, Beijing, China

Driven by societal needs and challenges, fast development of LED and semiconductors technologies, lighting is going through a radical transformation. This transformation is characterized by continuous and aggressive efficacy increase and cost reduction to replace traditional light sources by LED; revolution of forms and fixtures; seamless integration of LED light sources with semiconductors to create digitalized and smart lighting systems and solutions; emerging of "more than Illumination" functions and applications by using LED for healthcare and wellbeing, horticulture and food, communication, safety and security, etc. The success of this lighting transformation depends on not only the industry and market development, but also the creation and exploitation of new fundamental knowledge and talent development. This book series is the concerted action of global experts from industry and academia. It aims to provide the state-of-the-art fundamental theory and knowledge, the latest technology development, best industrial practices and guidance for academic research, technology and industrial development. It will cover all aspects of development of SSL, such as materials, device technologies, packaging and modules, luminaries & systems, thermal management, testing, reliability, total life time management, equipment, power management, sensors, communication and control, design and architecture, and other newly emerged scientific domains.

More information about this series at http://www.springer.com/series/8864

Jinmin Li • G. Q. Zhang Editors

# Light-Emitting Diodes

Materials, Processes, Devices and Applications

Editors

Jinmin Li

Chinese Academy of Sciences

State Key Laboratory of Solid State Lighting

Solid State Lighting R&D Center

Beijing, China

G. Q. Zhang Delft University of Technology DELFT, Noord-Brabant The Netherlands

ISSN 2196-4203 ISSN 2196-4211 (electronic)

Solid State Lighting Technology and Application Series

ISBN 978-3-319-99210-5 ISBN 978-3-319-99211-2 (eBook)

https://doi.org/10.1007/978-3-319-99211-2

Library of Congress Control Number: 2018962860

© Springer International Publishing AG, part of Springer Nature 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### **Foreword**

From the report of red light-emitting diodes (LEDs) by Nick Holonyak in the 1960s to the Nobel Prize in Physics awarded for the invention of blue LEDs in 2014, we have witnessed many historical milestones of LED research, development, and industrialization. It is no exaggeration to say that solid-state lighting (SSL) based on compound semiconductor materials has revolutionized artificial lighting. Benefits of the progress in lighting technology on civilization have led to a greatly improved standard of living for all of mankind. For instance, SSL has enabled the realization of bright and energy-saving white light sources, full-color display, and projection. Besides, many novel and emerging applications have been possible thanks to the SSL technology, such as visible light communications, LED-enabled medical treatment, and lighting for semiconductor manufacturing, agriculture, fish industry, horticulture, and animal breeding. These achievements have dramatically expanded the application boundary of lighting, marking a brand new horizon of illumination. At the same time, they have also triggered new challenges for future research and technology development.

Contributors to this book are global leading SSL engineers and scientists. They provide an overview of the latest developments in the relevant areas, as well as their personal views about future development directions. It covers wide aspects of the device from deep ultraviolet to the visible spectrum made from compound semiconductor materials. This book is divided into four parts, and the concept covers all key processes of the research, from epitaxial growth of the materials on different substrates, structure design and optimization, packaging, and reliability to the emerging applications. This book will be of interest to scientists and engineers working on LED technology and applications, as well as graduate students in material science, optical engineering, applied physics, and electrical engineering.

Nagoya University, Nagoya, Japan

Hiroshi Amano

Thuficon

#### Contents

| 1  | GaN Substrate Material for III–V Semiconductor  Epitaxy Growth                                                                                                                                               | 1   |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | SiC Single Crystal Growth and Substrate Processing                                                                                                                                                           | 41  |

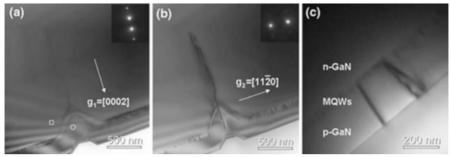

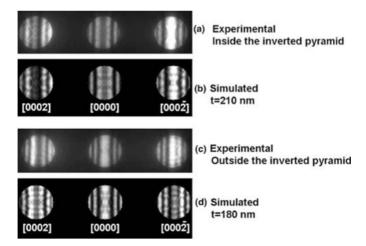

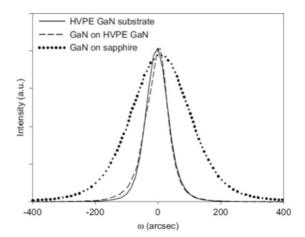

| 3  | <b>Homoepitaxy of GaN Light-Emitting Diodes</b> Ke Xu, Miao Wang, Taofei Zhou, and Jianfeng Wang                                                                                                             | 93  |

| 4  | <b>GaN LEDs on Si Substrate</b>                                                                                                                                                                              | 133 |

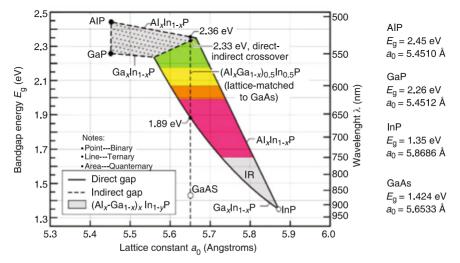

| 5  | The AlGaInP/AlGaAs Material System and Red/Yellow LED Guohong Wang, Xiaoyan Yi, Teng Zhan, and Yang Huang                                                                                                    | 171 |

| 6  | The InGaN Material System and Blue/Green Emitters                                                                                                                                                            | 203 |

| 7  | Al-Rich III-Nitride Materials and Ultraviolet Light-Emitting Diodes Jianchang Yan, Junxi Wang, Yuhuai Liu, and Jinmin Li                                                                                     | 245 |

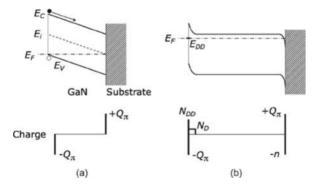

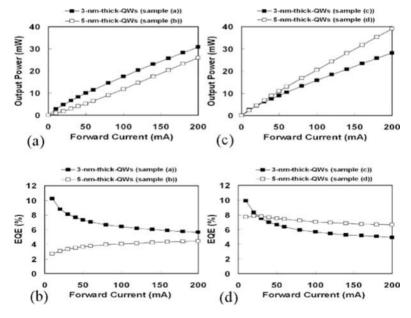

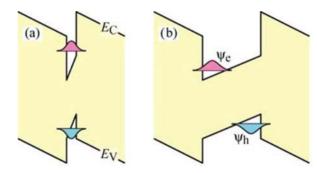

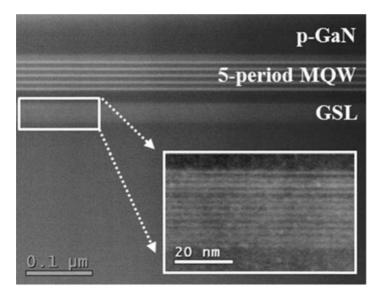

| 8  | Technology and Droop Study for High Internal Quantum Efficiency Bo Shen and Zhizhong Chen                                                                                                                    | 281 |

| 9  | On the Light Extraction Efficiency for III-Nitride-Based Light-Emitting Diodes Zi-Hui Zhang, Yonghui Zhang, Sung-Wen Huang Chen, Wengang Bi, and Hao-Chung Kuo                                               | 311 |

| 10 | Enhancing Wall-Plug Efficiency for Deep-UV Light-Emitting Diodes: From Crystal Growth to Devices  SM Islam, Vladimir Protasenko, Shyam Bharadwaj, Jai Verma, Kevin Lee, Huili (Grace) Xing, and Debdeep Jena | 337 |

viii Contents

| 11  | Reliability of Ultraviolet Light-Emitting Diodes                                                                                                                          | 397 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

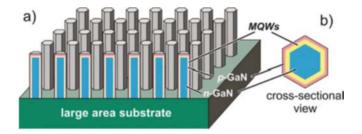

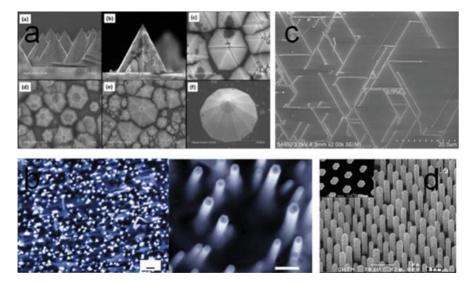

| 12  | Nitride Nanowires for Light Emitting Diodes  Nan Guan, Xing Dai, François H. Julien, Joël Eymery, Christophe Durant, and Maria Tchernycheva                               | 425 |

| 13  | Light-Emitting Diodes for Healthcare and Well-being                                                                                                                       | 485 |

| 14  | <b>Light-Emitting Diodes for Horticulture</b>                                                                                                                             | 513 |

| 15  | The Effect and Mechanism of Light on the Growth, Food Intake, and Gonad Development of Atlantic Salmon (Salmo salar) Reared in RAS  Ying Liu, Xiaolong Gao, and Liang Chi | 549 |

| Ind | index                                                                                                                                                                     |     |

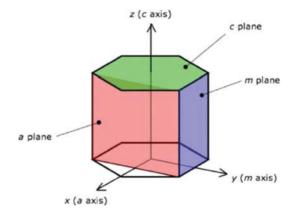

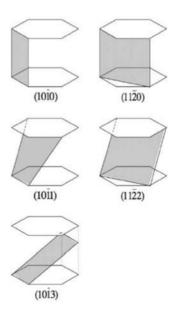

# Chapter 1 GaN Substrate Material for III–V Semiconductor Epitaxy Growth

Rong Zhang and Xiangqian Xiu

#### 1.1 Introduction

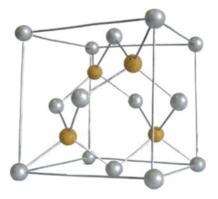

Wide bandgap semiconductor is known as the third-generation semiconductor material, as the engine and key technology of high-temperature, high-frequency, high-power semiconductor devices and IT industry. Wide bandgap semiconductor refers to the wide bandgap in 2.0–6.0 eV semiconductor materials, including SiC, GaN, ZnO, AlGaN, etc. The excellent properties, such as big bandgap, high breakdown electric field intensity, high saturated electron drift speed, big thermal conductivity, small dielectric constant, strong radiation resistance, and good chemical stability, make them well suitable for the radiation-resistant, high-frequency, high-power, and high-density integration of semiconductor devices. Based on the wide bandgap, the blue, green, and ultraviolet light-emitting devices (LEDs) and light detector have been developed and commercialized.

The III-N materials enable new semiconductor devices with previously unobtainable performance capabilities in terms of light output, power handling, and efficiency, and these attributes will make possible the reinvention of existing technologies in ways that benefit many facets of our lives. More application fields accelerate the marketization. While there are many potential applications for these materials, the biggest applications appear to be light generation and the control of electrical power. Driven by optoelectronics, particularly GaN-based laser diodes (LDs) and high-brightness GaN-on-GaN LEDs, the market for bulk GaN substrates is expected to grow at a CAGR (compound annual growth rate) of 10% from 2017 to 2022 and could reach more than 100 M\$ in 2022, according to a recent market survey from Yole Développement.

R. Zhang  $(\boxtimes) \cdot X$ . Xiu

School of Electronic Science and Engineering, Nanjing University, Nanjing, China

e-mail: rzhang@nju.edu.cn

In this paper, we summarize the major efforts in GaN substrate development and present the current progress in producing large-scale high-quality GaN substrate materials. We discuss the advantages of using the native GaN substrates with respect to the current heteroepitaxial nitride-based devices.

#### 1.1.1 Importance of GaN Substrates

Bulk crystals of nitrides cannot be obtained by well-known direct synthesis methods such as Czochralski or Bridgman growth from stoichiometric melts, because of the extreme physical conditions, such as high melting temperature and very high decomposition pressure at the melting point (molten gallium nitride under 2225 °C and the pressure of 6 GPa). Growth of semiconductor-quality crystals at these conditions would be practically impossible. Therefore the crystals have to be grown by the methods requiring lower temperatures. In the past, large-scale high-quality GaN films are mostly grown on the heterogeneous substrate for a long time.

Sapphire is the most commonly used substrate for the hetero-epitaxy of GaN but is far as a kind of ideal substrate for GaN-based LEDs except the low cost. Its two biggest disadvantages are that the obvious difference of the lattice constant and the thermal expansion coefficient compared with GaN. This will cause the strain in the GaN epitaxial layer, and strain can produce point defects and dislocations, which reduces the quality of GaN epitaxial layers and InGaN quantum wells. The defects and dislocations can limit the light-output efficiency of LED devices.

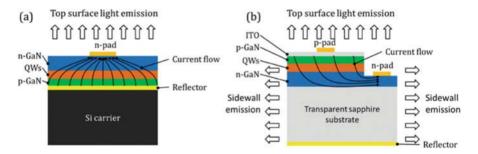

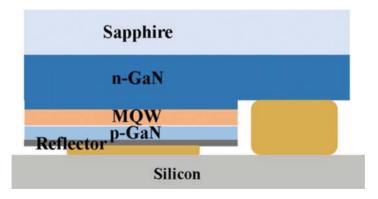

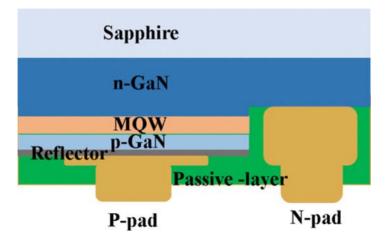

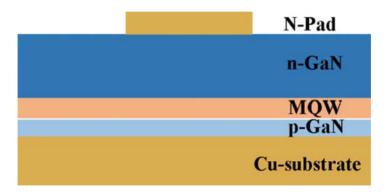

As a substrate for sapphire, there are two very important obstacles in the manufacturing of high-performance LED. One is the electrical insulating properties of sapphire. Sapphire substrate with the high resistivity is not ideal for the LED devices, because the top contact electrode restrained its transverse current density for the inversion structure of LED devices. This will lead to the current crowding effect and local hotspots, which will be unfavorable factors for the LED luminous efficiency and the maximum brightness of the device. The second, sapphire, has the characteristics of big thermal resistance and also can seriously hinder the ability of heat dissipation, which in turn will further restrict the luminous efficiency and the life and brightness of the devices.

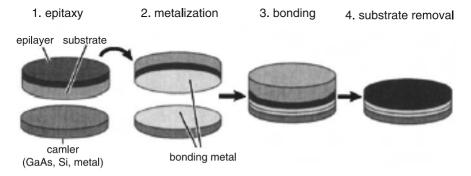

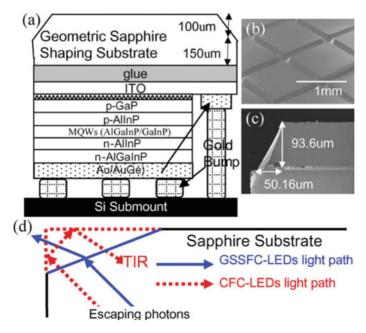

In order to solve these problems, people invented all kinds of technology to improve the luminous efficiency, life, and power. According to the above two obstacles, high-end technology used by LED chip maker is GaN epitaxial layer transferred to the substrates of good electrical and thermal conductivity properties. Usually by laser stripping and wafer bonding process, the LED chip structure will be laser stripping down from sapphire substrate and then transferring to bond with another kind of thermally conductive substrate. The laser stripping process involves usage of pulsed 248 nm KrF excimer laser. The laser is strongly adsorbed at the the sapphire/GaN interface and results in decomposition of the 100 nm thick GaN thin layer, which lead to the separation of sapphire and GaN. The technology is widely applied in the high-power LED device.

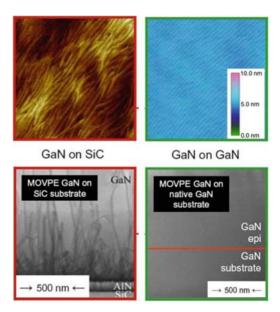

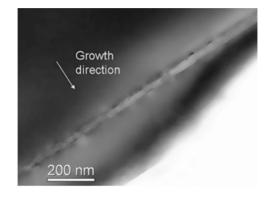

Fig. 1.1 Homogeneous epitaxial GaN films have higher quality and lower dislocation density, even compared with the best foreign substrate SiC

In fact, the most suitable substrate materials for the fabrication of LED should be native GaN substrate. Availability of lattice-matched GaN substrates can bring not only a high quality in GaN-based devices to improving device performance through eliminating the structural defects and providing better vertical electrical and thermal conductivity; moreover, it will lead to cost-efficient device processing through simplification of the epitaxial growth process by eliminating the need for low-temperature buffer layers.

As shown in Fig. 1.1, even if compared with the best foreign substrate, homogeneous epitaxial GaN has a higher quality and lower dislocation density [1]. It can improve the quality of the epitaxial layer and quantum well because of the proper lattice and thermodynamics match. It also has almost all of other advantages as follows. Although GaN substrate is more expensive, the area of one single chip on GaN substrate wafer is greatly reduced, which means that a single chip can use as three traditional chips. LEDs based on the GaN substrate have greater drive current, higher luminous efficiency, and simple process to the very good application prospect. Usually, GaN substrate is n-type conductive, which is beneficial to make vertical structured LED. Compared with traditional vertical structure in production of sapphire substrate to use laser liftoff process, it can bring the simplified processes and can reduce costs, raising the yield to achieve the higher cost performance.

In recent 10 years, researchers around the world have made an important progress in the study of the freestanding GaN substrate. And in the next few years, GaN substrates suitable for the devices with a diameter from 3 in. to 6 in. will be mass production.

### 1.1.2 Key Drivers for GaN Substrate Commercialization Success

One of the areas for the application of GaN substrates is in GaN laser diodes (LDs), where GaN substrates provide a clear and immediate benefit in the earlier days. The new applications for GaN-based LDs are primarily for next-generation, high-definition DVD players and recorders, although other applications include high-definition video projectors and displays, commercial printing, and testing and measurement applications, such as spectroscopy and bio-sensing.

There is no doubt that LED technology will take market share over the traditional lamp and tube business. In either a cautious or a more aggressive scenario, LED applications will certainly be the key drivers for the bulk GaN market, according to Yole Développement.

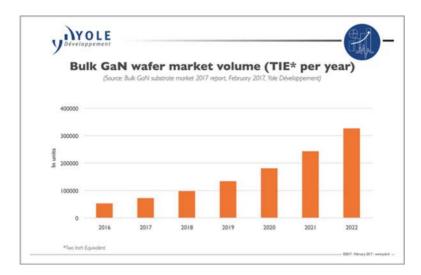

The report "Bulk GaN substrate market 2017" from Yole notes that while the Blu-ray segment which in the past was the GaN-based laser industry's main driver continues to decline, it is expected to be offset by nascent, growing segments like projectors (office projector, mobile pico projector, head-up display, etc.) and automotive lighting, leading to new growth opportunities for bulk GaN substrates. When new devices are developed and demonstrated and new areas of commercial demand are generated, this can provide further motivation for substrate manufacturers to increase manufacturing capacities. For example, Fig. 1.2 shows the forecast for TIE (2 in. equivalent) GaN wafer volume for device applications, with unit volumes at nearly 350,000 in 2022. This volume forecast represents a tremendous opportunity for GaN substrates but will require significant cost reduction in order to meet expected cost requirements.

Fig. 1.2 TIE GaN wafer forecast for device applications. Source: Yole Développement

Considerable technology development is needed to enable penetration of GaN devices into the solid-state lighting (SSL) and power electronics markets. The performance of the GaN devices must be improved in many areas: LED luminous efficacy at high lumen output, FET and diode breakdown voltage and on-resistance, and power switching reliability, among others. The latest report reveals more and more GaN-based devices fabricated on advanced GaN substrate. At the same time, with the increase of demand of blue laser diode, UV LED, and high-power, high-frequency devices, the amount of GaN or AlN substrates is increasing. Only the high quality of substrate can provide high-performance device because of lattice matching and excellent thermal management features. Bulk GaN substrates are expected to be used for many devices addressing these market opportunities, but there are numerous challenges facing the adoption of bulk GaN substrate technology.

Above all, substrate cost must also be significantly reduced in order to become economically practical in the device applications, which is particularly challenging due to incumbent GaN device technology based on foreign substrates. GaN substrate materials provide clear and immediate benefits for GaN-based LD applications over sapphire-based approaches, particularly at higher operating current density, and GaN substrate manufacturers are currently focused on addressing this market. Other benefits for LEDs, RF FETs, power devices, and photodetectors have been shown, but commercialization of these devices requires high volumes of low-cost substrates. These improvements will occur through the continued development of bulk growth techniques, such as HVPE, ammonothermal growth, solution growth, and combinations thereof.

As these improvements are made, the potential for III-N devices to do more (more light, more power) with less (higher energy efficiency, less electricity, less waste heat) will be enabled.

#### 1.2 The Technical Routes for GaN Substrate Materials

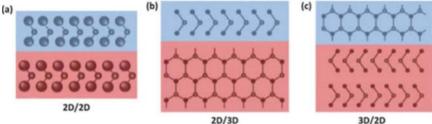

Because the homo-epitaxy on GaN substrates has better advantages compared with the hetero-epitaxy, then research about GaN substrate is of great practical value. Now the basic ways for GaN substrate materials have generally the following three technical routes (as shown in Fig. 1.3) (Substrates for Nitride Epitaxy, IWN2008, Switzerland, 2008).

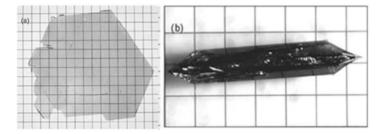

#### 1.2.1 Native GaN Substrates

One of the most important approaches to obtain GaN substrate wafers is to obtain a larger dimension of columnar bulk crystals or boule. A lot of experimental studies have shown that GaN at the top of the columnar crystal has very high quality. Bulk GaN crystals can be obtained by high-temperature and high-pressure solution method, ammonothermal growth, Na-flux growth, or the combination of a variety

6 R. Zhang and X. Xiu

Fig. 1.3 Three technical routes for GaN substrate materials (IWN2008, Switzerland, 2008)

#### · Single wafers

#### Boules

WS-1 "Substrates for Nitride Epitaxy" IWN2008, Switzerland 2008

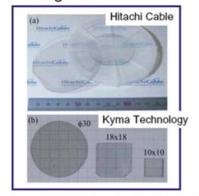

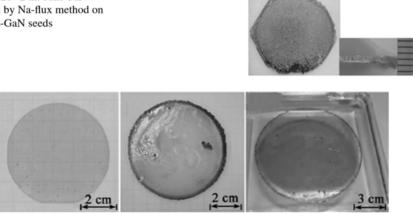

Fig. 1.4 Native GaN substrates reported by some companies (IWN2008, Switzerland, 2008)

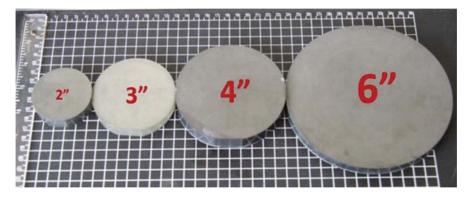

of ways. High-quality GaN chips can be got by cutting GaN crystal into flakes and polishing, and the dislocation density for GaN crystal in different ways is usually between  $10^4$  and  $10^6$  cm<sup>-2</sup>. Thicker pear-shaped or columnar crystals can not only produce more chips, but also can further reduce the defect density. So the most ideal solution to solve the problems of GaN substrate is to obtain single crystal GaN substrate chips by the abovementioned methods. But although GaN substrates have been reported (as shown in Fig. 1.4), GaN native substrates with a large size of more than 2 in. have not been commercialized. As shown in Fig. 1.4, the large size of columnar crystal is still mainly grown for a relatively long time by the method of hydride vapor-phase epitaxy (HVPE) or the combination of HVPE and other technologies.

Among all the bulk growth techniques under investigation today for nitrides, HVPE is the most promising technique since it utilizes a process with more favorable conditions, such as the low pressure and relatively low growth temperature. Because of the high growth rate, its growth process is also cost-effective. Other techniques, such as Na-flux or ammonothermal growth, are still under development.

#### 1.2.2 GaN Liftoff Substrate Wafers

Until now, hydride vapor-phase epitaxy is considered as a highly practical method by growing the GaN thick films for quasi-bulk substrates after the separation from the foreign substrates or obtaining GaN boules with a thickness of more than centimeter grades to be sliced to fabricate native bulk substrates.

The biggest advantage of the technique is its ability to produce high-quality material at high growth rates due to a high surface migration of the halide species. The versatility of HVPE as a growth method is motivated for both device applications and substrate application.

HVPE-GaN thick film is usually grown on foreign substrate with the thickness of more than 500  $\mu$ m and less than 1000  $\mu$ m at a growth rate of between several microns and 1000  $\mu$ m. And then the foreign substrate is peeled by laser liftoff (such as sapphire substrate), chemical corrosion (such as Si and GaAs substrate), or mechanical thinning or self-separation by utilizing the change of stress. After the thinning or polishing of self-standing GaN thick film, GaN substrate wafers would be obtained. Due to the lattice mismatch from the heterogeneous substrate, the lattice distortion introduced by the atom cannot completely eliminate the stress, so the dislocation density is roughly between  $10^6$  and  $10^8$  cm<sup>-2</sup>. Now, 2 in. GaN wafers by HVPE method have been commercialized, but the price is quite higher. Due to the technical reasons, the yield is low. The HVPE-GaN wafers are mainly used in industry of GaN LDs; the mass application in the field of LEDs is not yet mature.

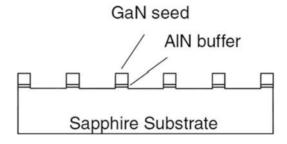

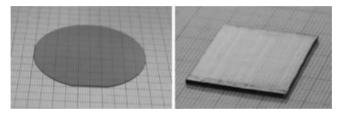

#### 1.2.3 GaN Templates

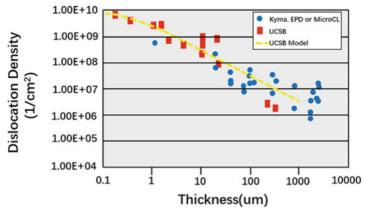

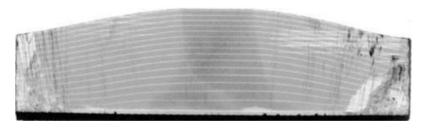

GaN template refers to the compound substrate grown on heterogeneous substrate, which the thickness is more than 10  $\mu$ m (Fig. 1.5). And compared with MOCVD GaN of the thickness of a few microns, the dislocation density is slightly lower and generally  $10^8$  cm<sup>-2</sup>. The increase of the thickness will further reduce the dislocation density, and the dislocation density of free standing GaN substrate can reduce about two orders of magnitude (Fig. 1.6). The results show that with the increase of the thickness of GaN template from 5 to 50 to 150  $\mu$ m, the dislocation density is reduced from  $10^9$  cm<sup>-2</sup> to  $5 \times 10^8$  cm<sup>-2</sup> to  $1 \times 10^8$  cm<sup>-2</sup>. The thickness of GaN templates is generally less than 50  $\mu$ m, and GaN template with the thickness of more than 50  $\mu$ m will be easily cracked due to large lattice and thermal mismatch between

8 R, Zhang and X, Xiu

Fig. 1.5 GaN templates on sapphire substrate

Fig. 1.6 Comparison of the dislocation density of different GaN films (source: Cree, Inc.)

GaN and sapphire. Due to the low cost and high quality, GaN templates by HVPE have the very big potential applications.

#### 1.3 Major Methods for the Growth of GaN Substrate

GaN at high temperatures is decomposed into Ga and  $N_2$ , only melting in the physical conditions of more than 2200 °C and 6 GPa above nitrogen pressure. So the traditional Czochralski or Bridgman method cannot be used for the growth of GaN single crystal. At present, GaN is generally grown by hetero-epitaxy of MOCVD and MBE. In order to get high-quality GaN film, almost all the growth of technology and the substrates have been tried. But the high defects in the hetero-epitaxy GaN can limit the improvement of the GaN-based device performance. At the same time, research on the growth technologies for bulk GaN crystals has never stop, and a lot of trial and effort has been carried out, including the liquid-phase and gas-phase growth.

#### 1.3.1 The Liquid-Phase Growth

The common liquid-phase growth methods are mainly high-pressure nitrogen solution growth (HPNSG), Na-flux dissolved agent method, and ammonothermal method, which all these three methods can prepare high-quality bulk GaN crystal.

As the homo-epitaxy substrate, GaN obtained by the liquid-phase growth will overcome the deficiency of the hetero-epitaxy. In addition, the photoelectric properties of GaN crystal by the liquid-phase growth are excellent, which is suitable for the high-performance devices. So the liquid-phase methods have also attracted more attention for the preparation of high-quality GaN crystal.

#### 1.3.1.1 High-Pressure Nitrogen Solution Growth (HPNSG)

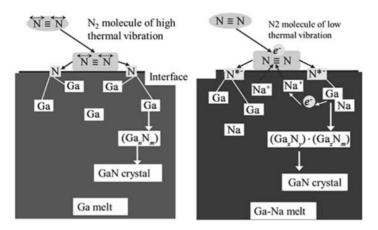

In the liquid phase growth technology of gallium nitride, high-pressure nitrogen solution growth is the most commonly used method for single crystal growth. Early in the mid-1970s, GaN single crystal with a diameter of about 1 mm was obtained by this technology. Its growth principle is shown in Fig. 1.7 (left); to put the high-pressure nitrogen gas into the molten state of Ga in the high temperature of crucible, enough N can be dissolved into the high-temperature molten metal Ga; nitrogen molecules on the surface of the molten Ga would be decomposed into N atoms and react with Ga to form GaN. GaN single crystal would be prepared at a certain temperature gradient for the local supersaturation of N atom. At that time, the temperature and pressure were only 1200 °C and 10.8 GPa. Because GaN is very stable at high temperature and high pressure, the dissolvability of N atoms is very

**Fig. 1.7** Growth mechanism of GaN by HPNSG (T=1300-1600 °C, PN<sub>2</sub> > 1 GPa) (left) and Na-flux method (T=600-850 °C, PN<sub>2</sub> > 0.1 GPa) (right)

low in the molten metal Ga (atomic number scores less than 1%) [2], which leads to a decline of GaN crystal growth rate (about 1 mm/24 h) [3]. So it must be long enough to grow the large-size and high-quality GaN single crystal. Of course, due to the growth conditions of the high pressure, the crystal defect is extremely low and suitable for the preparation of high-quality crystal [4].

After more than 10 years of development, as the experimental conditions change, the temperature and pressure have been effectively improved to 2300 °C and 4 GPa. GaN single crystal by HPNSG method is generally a hexagonal flake structure, along with the [0001] direction of wurtzite structure. A suitable temperature gradient can improve the growth rate of [0001] direction at a certain extent. But too large temperature gradient will affect the stability of the growth, which will lead to the honeycomb structure in the GaN surface [2]. HPNSG GaN single crystal has good crystallization quality commonly by XRD rocking curve test; the full width at half maximum along the major axis and the vertical straight in the axis direction is only, respectively, 0. 028° and 0.017°, which is similar to the quality of the crystal.

High-pressure nitrogen solution method can be used for the preparation of high-quality GaN crystals, but this growth of GaN requires very high pressure in the range of GPa which sets rigorous standards for the growth facilities, the high production costs is not conducive to large-scale industrial production.

#### 1.3.1.2 Ammonothermal Growth

From the angle of the crystal growth, the basic principle of ammonothermal crystal growth is similar with that of hydrothermal method. The ammonothermal process is a solvothermal process that allows the solubilization of polycrystalline III-nitride nutrient or feedstock in supercritical ammonia under high pressure by utilizing a solubilizing agent or mineralizer. The dissolved nutrient is then transported to the region of crystallization, where it recrystallizes on seed crystals or through self-seeding. A schematic of the internally heated growth system and a photo of a 2 in. diameter crack-free, as-grown bulk crystal are shown in Fig. 1.8, respectively [5, 6].

The growth process of GaN single crystal by ammonothermal method can be summarized as follows: dissolve the needed III-nitride nutrient or feedstock in supercritical ammonia fluid (such as KNH<sub>2</sub>) containing mineralizer to form a saturated solution under high pressure, and then take appropriate technical measurements to make the saturated solution into metastable supersaturated solution, and begin to grow GaN single crystal on the seed crystal. Here, the choice of mineralizer agent, reaction source distribution, and transport of dissolved material are the key factors in the process of ammonothermal GaN crystal growth.

The specific process is to seal the nutrient, seed the crystal and mineralizer solution in the autoclave, and control the temperature difference of nutrient area and seed crystal area, respectively, so as to accelerate the convection of the solute and seed for the crystal growth. For various kinds of growth process, the largest difference is caused by the different mineralizer, because the solubility of crystal is different from temperature dependence in different mineralization agent solution.

**Fig. 1.8** (a) Schematic of high-pressure ammonothermal GaN growth apparatus employed at Soraa; (b) As-grown nominal 2 in. diameter GaN(0001) crystal produced using the ammonothermal method

The ammonothermal growth is conducted by transporting the mass from high-to low-temperature zones, and this method has been reported to possess several advantages, including lower dissolution density due to solubilizing in the higher-temperature zone, lower contamination probability due to recrystallization in the lower-temperature zone, lower probability for cubic formation, and absence of disastrous effect of the basic solution on the autoclave materials, which results in the improvements of safety and cost-effectiveness. In contrast, the acidic approach requires special, usually costly, Au or Pt liners, and the safety operation still remains problematic.

When the crystal in mineralizer solution has the solubility of positive temperature coefficient (higher solubility while varying with temperature), the bottom of the autoclave used for nutrient is generally designed as the high-temperature zone, and the top of the autoclave as low-temperature area is used to hang the seed crystal. Usually the crystal nucleation can be easily controlled for the growth of the solubility of positive temperature coefficient. When the crystal in mineralizer solution has a negative solubility coefficient (the solubility of crystal drops while varying with temperature), it should be seed crystal hanging in the high-temperature area and put nutrient at low-temperature area.

GaN solubility in pure ammonia is small because of ammonia with weak polarity; thus in the ammonothermal method, pure ammonia solution is not suitable for GaN crystal growth. To refer the hydrothermal method for the selection principle of mineralizer, ammonothermal GaN crystal growth also needs to choose a suitable mineralizer. The type of the mineralizer used determines the main type of the ammonothermal approach, with respective advantages and disadvantages. Selection of mineralizer is conformed to the following two points: (1) the solubility and solubility temperature coefficient of the basic crystal material in the ammonia solution is enough to achieve an effective growth rate; (2) in the ammonothermal system, crystalline materials are the only stable solid phase; thus it will not affect

the system's phase relationship. At present in ammonothermal GaN crystal growth, two kinds of mineralizer are mainly adopted, a kind of alkali XNH (X = Li, Na, K) and another for acidic NHX (X = C1, Br, I). The neutral mineralizer was not suitable for GaN crystal growth. GaN crystal is generally not grown by neutral mineralizer, such as KX (X = C1, Br) and NaX (X = C1, Br). Only when the mineralizer is KI, a small amount of wurtzite GaN is generated, but it is mixed with zinc blende GaN.

Of course, there are many factors, such as temperature and concentration of mineralizer, impurity, growth, and so on, to influence the growth of GaN crystal.

In general, the ammonothermal technique is characterized with relatively low growth rate capacity; but in this technique, the relatively low temperature and reasonable pressure allow controllable recrystallization at close to equilibrium conditions for the production of high-quality material. And the technique also allows large-scale wafer growth and the multiple-seeded growth in a single run. Up to now, Poland Ammono Inc. has been able to achieve the commercial mass production of 2 inch GaN wafer with m- and c- direction. But as a result, the ammonothermal growth needs GaN seed crystal, and it is affected by seed crystal size. GaN single crystal with more than 2 in. in diameter is still in the development stage. Nevertheless, the approach is expected to be capable of handling higher growth rates at higher pressures.

The quality of this type of material is still in the beginning of detailed evaluation. Given the fact that a reasonable large crystal is a result of a very long process, optimization of the growth conditions and a systematic series for thorough analysis will take more time.

#### 1.3.1.3 Na-Flux Method

An alternative solution growth approach by using Na flux instead of nitrogen solution was proposed by Yamane et al. [7] several years ago. So far, as a self-nucleation growth, it is quite similar to that of high-pressure solution growth approach.

On the basis of high-pressure nitrogen solution method, the researchers developed a Na-flux method, and the growth mechanism is shown in Fig. 1.7 (right). Na is added in the molten Ga solution. Because of the very high reducibility of Na, N<sub>2</sub> molecules can be ionized and easily dissolved into molten Ga-Na solution under low temperature and low pressure, which thus greatly increase the N solubility in the solution. So GaN crystal will be synthetized at relatively low pressure. The results of GaN crystal by this self-nucleation growth are quite similar to that obtained by high-pressure solution growth approach. But the advantages of Na-flux method are mostly related to the more favorable growth conditions of typically 800 °C and 5 MPa. In the 1990s, Yamane et al. [7] got the GaN crystal by solvent method using Na as cosolvent for the first time.

In the early stages of Na-flux research period, the crystal nucleation position is uncertain; the crystal has often been found in the crucible wall. So the liquid-phase epitaxy (LPE) has been developed in order to limit the nucleation on the seeds.

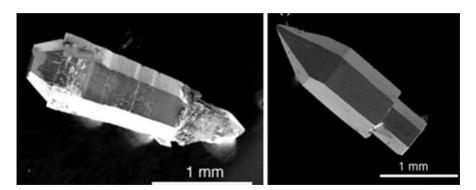

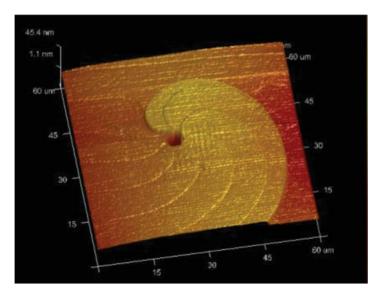

Fig. 1.9 GaN seeded growth with a (left) Na-Ga premixed melt and (right) with the Ga melt and Na vapor

Aoki et al. studied the influence of the growth temperature and  $N_2$  pressure on the crystal morphology and growth rate during the epitaxial growth of seed crystal. However, increasing the solubility of the nitrogen in the molten Ga-Na solution, at the same time, the initial GaN seed and GaN epi-crystal also become much easier to decompose, which make the crystal surface rough before and after the crystal growth. In order to overcome the shortcomings, Yamada et al. [8, 9] proposed the Na-vapor assisted GaN growth to obtain the high-quality surface of GaN crystal, and the obvious difference can be seen from Fig. 1.9.

In the early study, GaN grown by Na-flux method is the colored crystal due to the lack of N in the process of crystal growth, because N solubility is not high in the solutions. In order to improve the N solubility in the Ga-Na melt, joining the alkali metal element such as Li and Ca into the Ga-Na melt in the hybrid cosolvent significantly increased the N solubility in the melt and improved the permeability of GaN crystals [10].

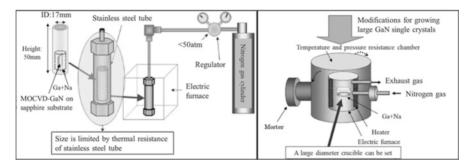

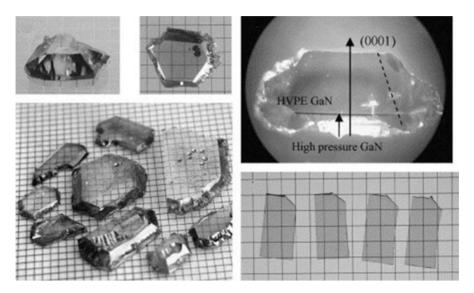

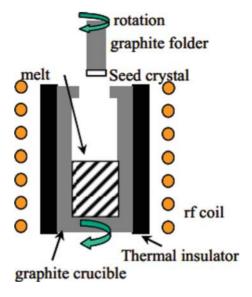

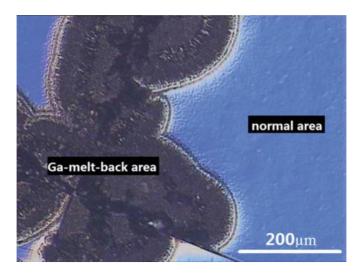

In the absence of the GaN seed, two growth habits were demonstrated—prisms or platelets—with length and lateral sizes of a few millimeters. In order to increase the size of GaN crystal, F. Kawamura and Y. Mori et al. used HVPE-GaN substrate as a seed crystal for the epitaxial growth of 2–4 in. GaN film. Kawamun et al. [11, 12] developed a set of equipment for large-size GaN single crystal substrate. The schematic diagram of the equipment is shown in Fig. 1.10, and one of the most critical improvements is to put the heating system (crucible and electric furnace) in the stainless steel compression cavity with a water cooling system, by shaking the cavity to stir the melt at the same time. After this modification, the growth system can be used to grow large-size GaN chip. In the case of using GaN film grown by MOCVD, growth rates up to 20  $\mu$ m/h were obtained, and a boule with a thickness of 3 mm was shown.

In order to improve the crystal quality, Kawamura et al. [14] join carbon (C) to inhibit the polycrystalline growth. By optimizing the growth conditions, Mori et al. [13, 15] have successfully carried out the epitaxial growth of 2–4 in. GaN on the large size of seed crystal, GaN crystals are highly uniform and free of cracks, and

Fig. 1.10 Schematic of the modified Na-flux method for GaN growth on 2 in. templates

the thickness can be up to more than 750  $\mu$ m, as shown in Fig. 1.29. GaN crystal has a good permeability and lower impurities, although the dislocation density of the initial seed crystal HVPE-GaN is up to  $10^8$  cm $^{-2}$  orders of magnitude, but the chip dislocation density decreased to  $2.3 \times 10^5$  cm $^{-2}$  after growth by the liquid-phase epitaxy (LPE). A decrease of dislocation density from  $10^8$  cm $^{-2}$  in the seeds to  $10^4$  cm $^{-2}$  in the regrown crystal was reported and explained in terms of a change in the dominating growth mode from vertical in the seed to lateral in the Na-flux solution growth [14]. It is also found that Na and C additives are not doped into the GaN crystals by the test of the secondary ion mass spectrometry.

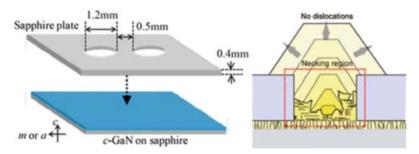

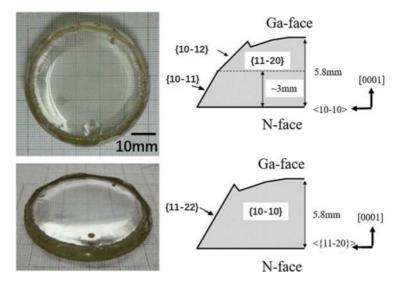

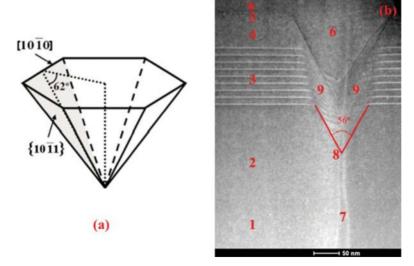

Although its dislocation density of GaN crystal by Na-flux method has been greatly reduced, but with the demand for higher crystal quality of GaN-based photoelectric device, lower dislocation density or even no dislocation GaN crystal is needed. Similar to the Czochralski method for the growth of Si ingot, a necking technique was adopted to realize the growth of large-size GaN crystal without dislocations [16], as shown in Fig. 1.11. A dislocation generally propagates perpendicularly to the growing surface. Therefore, in the initial growth layer that consists of numerous (10-11) facets, the dislocations propagate perpendicularly to the (10-11) facets, and they are bent. Usually in the necking technique, the dislocation begins to extend like a bent neck from the growth surface and end in the sapphire wall, so that further propagation does not occur. The growth of (10–11) facets in this initial growth layer and the dislocation behavior are unique phenomena of the Na-flux method. Because the area of crystallography is without continuity, and the bent dislocation will end at the interface between the initial growth layer and single crystal, almost all of the dislocations from GaN seed crystal will eliminate inside the hole, and the final GaN crystals show no dislocation. In addition, the dislocations that propagate in the (0001) direction also terminate at the boundary between the initial growth layer and the preferentially grown single grain so that propagation of dislocations to a single grain cannot occur. Almost all dislocations which originated from the GaN seed layer are eliminated in the holes (i.e., the necking region), resulting in a GaN crystal free of threading dislocations. Imanishi et al. [17] have already succeeded in growing dislocation-free bulk GaN crystals with a diameter of more than 2 cm and a height of about 1.2 cm by the GaN small

Fig. 1.11 Schematic drawings of the configuration of two GaN point seeds and that of the growth model with a necking technique

Fig. 1.12 Schematic of coalescence growth from two isolated small seed crystals and SEM images of the sliced crystals (left), and schematic of coalescence growth from many periodically arranged small GaN seed crystals (right) [15]

seed crystal growth. The necking technique in the Na-flux GaN growth may be a major breakthrough for fabricating dislocation-free GaN ingots.

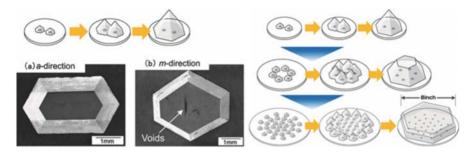

In order to grow large-scale GaN crystal without dislocations, they put forward the joint growth of multiple isolated small seed crystals for the large-scale GaN crystals. Figure 1.12 (left) is the experiment schematic of two seed crystals' joint growth; it can be found that GaN crystal quality is very high along one orientation and poor along the orientation of m-direction with a lot of defects [15]. Recently, they got high-quality GaN crystals from three isolated small seed crystals along a joint growth orientation, as shown for SEM images of GaN crystals in Imanishi et al. [17]. Obviously the joint growth is possible for manufacturing large diameter GaN crystals without dislocations. As shown in Fig. 1.12 (right), it is the schematic for GaN crystal by a periodic array of small seed crystals' growth [15].

One advantage of Na-flux method is simple for the growth equipment and low pressure for crystal growth, which can grow a large-scale, high-quality GaN crystal and even GaN crystals without dislocations using small seed crystal growth. So this method is gradually becoming the key technology of high-quality GaN crystals.

Another advantage of Na-flux method is its ability to reduce some structural defect density, consistent with reports for other material systems such as SiC. The dislocation density of GaN grown by high-pressure nitrogen solution method is lower than  $10^2~{\rm cm}^{-2}$ , and no dislocation GaN crystal can even be prepared by the union of HPNSG method and Na-flux small seed crystals. Similar results of reducing the dislocation density have been reported for alternative low-pressure solution growth (LPSG) at growth temperature in the range of 900–1020 °C [18] by employing a different chemical solution. A growth rate of 1  $\mu$ m/h was reported for growth on metalorganic vapor-phase epitaxy (MOVPE) GaN template on sapphire up to 3 in. in diameter. Also, at nearly atmospheric pressure and temperature of about 800 °C, employing another chemical solvent, seeded growth on HVPE-GaN seeds was demonstrated [19].

Up to now, the reported growth rates of a few micrometers per hour are not suited for bulk crystal growth. In addition, in these approaches, since nitrogen has to be dissolved and then diffused through the Ga melt to the growth front, maintaining homogeneous growth over large areas remains a challenge.

#### 1.3.2 Gas-Phase Growth for GaN Substrates

#### 1.3.2.1 Gas-Phase Transport Method

Since Johnson and others synthesized polycrystalline GaN with  $NH_3$  and molten Ga, many people began to study the gas-phase transport method for GaN single crystal growth, which is to transmit the Ga vapor at high temperature to react with  $NH_3$  for GaN single crystal. If the molten Ga metal is replaced with GaN powder as Ga resource, it is known as "sublimation method." The growth rate by the sublimation method is relatively slow but steady. But the sublimation method itself has a technical problem, which must keep a continuous supply of GaN powder during the growth. While molten Ga metal is used as Ga source, it can get the maximum growth rate, but not very much stable. Here, the high growth rate is thought to form the Ga droplets, and the instability of the growth rate is attributed to the formation of GaN shell in the surface of molten Ga metal, causing the growth stopping. Besides, the reaction of Ga and  $NH_3$  at the surface of Ga metal will cause the splash of Ga droplets on the surface of GaN crystal, which will change the growth mechanism.

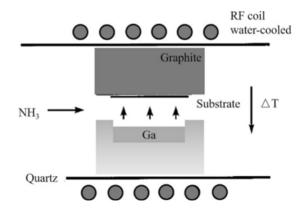

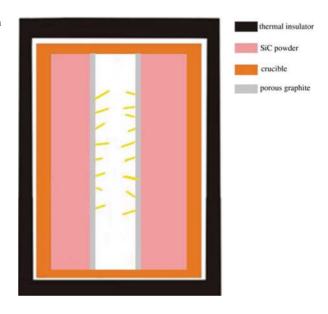

Now the improved gas-phase transport process is mostly studied, called the sublimation sandwich transport method (SST) [20], as shown in Fig. 1.13. In SST, a powder or polycrystalline material (Ga, GaN, or their mixture) is evaporated, transported across a small gap by a thermal gradient, and recrystallized on a substrate. The evaporation of metallic Ga in the ammonia ambient is a very convenient alternative to grow the thick, high-quality GaN films. This technique has all the characteristics of a vapor-phase epitaxy performed at an unusual high temperature.

Fig. 1.13 Schematic of the high-temperature vapor-phase epitaxy reactor. The graphite crucible containing the metallic Ga and the substrate is heated inductively via a water-cooled coil. Ga vapor is transported over a short gap of a few millimeters

The distance between the Ga source and the substrate is only several millimeters, the pressure of reaction tube is an atmospheric pressure, and the growth temperature is  $1170\text{--}1270~^\circ\text{C}$ . The SST growth rate is more than  $100~\mu\text{m/h}$ , and the fastest rate is up to about  $1100~\mu\text{m/h}$ . The SST method is simple, low cost, and faster, but the SST GaN crystal quality is also very poor. There are still some technical problems to solve, not up to the practical level.

#### 1.3.2.2 Hydride Vapor-Phase Epitaxy (HVPE)

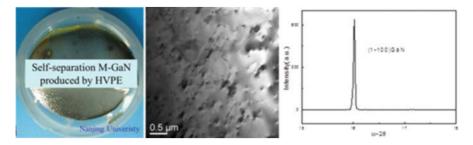

Although ammonothermal growth and Na-flux method seem to have more developing potential for the preparation of single crystal GaN substrate, it is not suitable for commercial application because of the small size ( $\leq 2$  in.) and low growth rate (50  $\mu$ m per day). Therefore, atmospheric hydride vapor-phase epitaxy is still the main method to obtain large-scale, high-quality self-standing GaN substrate. As a chemical vapor-phase transport, HVPE method has not only high growth rate, compared with other methods of substrate preparation, but also versatility as a method for the fabrication of both substrates and devices, with a larger application direction and development prospects.

In history, HVPE methods have played an important role in the research and development of arsenic and phosphide semiconductor materials. Although the extensive research and full development have been done for HVPE growth for arsenide and phosphide, little is known in terms of nitride growth. The reason is that there is no suitable substrate and the chemical growth is different, leading to HVPE growth of the nitride more complex. In spite of this, HVPE is still the first and the most common method of GaN epitaxial growth until the early 1980s.

The first growth of GaN by HVPE was reported by Maruska et al. in 1969, using a sapphire substrate by modified hydride equipment for gallium arsenide (GaAs) and indium phosphide (InP) [21]. In the 1970s to the early 1980s, the researchers attempted to grow GaN thick film on sapphire and then made the self-supported GaN substrate [22]. However, the HVPE-GaN film has a large number of crystal defects,

high background carrier concentration, and poor crystal quality. At the same time, it is difficult to realize p-type doping and effective doping control, which hinders the production and research of GaN-related devices.

Due to the serious difficulties in reducing the intrinsic carrier concentration and realizing the p-type doping, HVPE technology was almost entirely abandoned after the 1980s. However, there are still some reports about HVPE growth of GaN film, and its optical and electrical properties reported can still be the best results compared with that of GaN grown by metal organic vapor-phase epitaxy (MOVPE) or molecular beam epitaxy (MBE). In fact, even by the standards of the 1970s, the quality of GaN film grown by HVPE is still remarkable [23, 24]. From the late 1990s, most of the attention has been focused on the hetero-epitaxy of GaN on foreign substrates such as sapphire, Si, NdGaO<sub>3</sub>, and GaAs to realize freestanding GaN wafers. The first thick GaN (approximately 400  $\mu$ m) with a smooth surface was reported by Detchprohm et al. in 1992, using a ZnO buffer layer on sapphire [25]. Usui et al. [26] achieved a freestanding GaN wafer of 2 in. diameter size by the use of a new technique, epitaxial lateral overgrowth (ELO), to reduce the density of dislocations significantly, and by a laser irradiation from behind to remove GaN thick layer from the sapphire substrate.

HVPE system equipment is relatively simple and convenient to maintain, and with the improvement of growth technology, the crystal quality of HVPE-GaN has been improved unceasingly. Its growth rate is high and it is easy to obtain homogeneous and large-scale GaN thick film, which make it very hopeful to solve the problem of self-standing GaN substrate. Meanwhile, the existence of halide in the growth environment of HVPE can significantly affect the equilibrium of GaN reaction and improve the ELO growth rate. Using the HVPE-ELO technology, GaN thick film can also be grown at high growth rate in situ growth, and then low-density GaN substrates can be obtained by a variety of substrate separation technologies (such as corrosion, laser liftoff technology or mechanical polishing technology, etc.). HVPE, therefore, becomes the important method to prepare freestanding GaN substrates for the large-scale application of GaN-based optoelectronic devices.

#### 1.4 HVPE for GaN Substrate Materials

## 1.4.1 Chemical Reaction in the Growth of GaN by Hydride Vapor-Phase Epitaxy

HVPE for the growth of nitrides is a chemical vapor deposition method, and the reaction is usually carried out within the atmospheric quartz reactor. The reaction process is to introduce the hydrogen chloride under carrier gas into the reactor, reacting with metal gallium in the low-temperature zone, to flow the generated gallium chloride to the high-temperature zone and being mixed with ammonia to grow GaN. Unreacted gas is absorbed by the tail gas treatment system.

Nitride growth is actually using metal chloride disproportionation reaction, by raising the temperature to improve the stability of low compounds. Ga chloride has a variety of valence states (such as GaCl, GaCl<sub>3</sub>, etc.), and GaCl is stable at high temperatures in HVPE system, decomposing into GaCl<sub>3</sub> below a certain temperature. The above features make us adjust the temperature of the reaction chamber, realize the GaCl generation, and transfer and deposit GaN. So, in usual nitride HVPE growth system, they are divided into a high and low temperature reaction chamber area.

Therefore, the novel of HVPE method is the primary reactant (GaCl) generated in the reactor, where the liquid metal Ga react with HCl gas in the range of 800–900 °C. Then GaCl with the carrier gas are carried into the substrate and mixed with NH<sub>3</sub>, depositing GaN on the substrate. Substrate temperature is kept at 900–1100 °C, and N2 or H2 is the carrier gas. The chemical reaction is as follows:

$$Ga(s) + HCl(g) = GaCl(g) + \frac{1}{2}H_2$$

(low-temperature zone)

$$GaCl(g) + NH_3(g) = GaN(s) + HCl(g) + H_2(g)$$

(high-temperature zone)

The following six species were chosen as the necessary vapor species in analyzing the HVPE growth of GaN: GaCl, GaCl<sub>3</sub>, NH<sub>3</sub>, HCl, H<sub>2</sub>, and inert gas (IG) such as nitrogen or helium. Here, group III elements such as chloride (usually a single chloride) were transported to the substrate, so hydride vapor-phase epitaxy is usually known as chlorine gas-phase epitaxy. Due to relatively low saturated vapor pressure of metal chloride at room temperature, chloride molecules can easily condensed on the substrate at room temperature, and HVPE growth usually adopts a hot wall reaction chamber for in situ synthesis of chloride.

Using in situ synthesis chloride and hot wall reaction chamber, the complex gas transportation system and assistant heating systems can be avoided. In addition, if the metal chloride was pre-synthesized out the reactor, the strong absorbent and corrosive metal chloride will make their preservation and transportation very difficult. However, high corrosive HCl gas can also cause some difficulties. For example, if there is air leakage into the gas path or reactor, HCl will soon destroy the reactor. Based on this, some of the research team reported synthetic GaCl<sub>3</sub> instead of in situ synthesis of HCl to GaCl [27–29]. Using these precursors, researchers grow single crystal GaN and improve the purity of metal chloride source.

Based on the purity and operability, HCl is usually more common than chlorine. Because the Chloride has higher saturation vapor pressure than bromide and iodide, the chloride is the most commonly used halogen for transportation. Bromide and iodide have a lower decomposition temperature, and it is reported that they are often used in the growth at low temperature [30, 31].

In hydride vapor-phase epitaxy system, the chemical reaction will produce large amounts of NH<sub>4</sub>Cl, GaCl<sub>3</sub>, GaCl<sub>3</sub>, and NH<sub>3</sub>, which will be condensed and even

block the exhaust system, unless they are heated to a high enough temperature (>340 °C) or the reaction is under low-pressure conditions.

Although there are a lot of difficulties in the design of HVPE system due to the chemical reaction, it also provides a unique advantage. For example, unlike MOVPE, HVPE growth process is no carbon in nature, which is easier to grow high-purity GaN film. In addition, strong corrosive chlorine and hydrogen chloride can help to remove the excess growth of metal components on the substrates, so as to suppress the formation of rich gallium materials or separated Ga droplet. The self-stabilization effect and high mobility of adsorbed GaCl can be used to explain that HVPE is much higher in the growth rate than other epitaxial methods. Because of the self-stabilization effect in rich gallium conditions, GaN film by HVPE has a higher quality than that of other epitaxial methods (such as MBE or MOVPE). Although HVPE growth rate is at least one order of magnitude higher than other methods, the dosage of NH<sub>3</sub> is far lower. The impurities from NH3 and the cost are both significantly reduced in the growth of the VPE nitrides.

The consciously introduction of additional HCl to the growth zone at high temperature can effectively improve the Cl/Ga ratio, which plays a very important role in the growth of high-quality GaN film. The introduction of HCl may enhance the GaCl local saturation and improve the lateral growth, leading to a larger grain size. The early experiment research from Nanjing University showed that the introduction of additional HCl can improve the surface morphology and the crystal quality. Some patents point out that additional HCl can also reduce the pre-reacted GaN particles in space before depositing on the substrate. In addition, the presence of HCl can also enhance the decomposition of other impurities.

#### 1.4.2 Hydride Gas-Phase Epitaxial Growth System

It should be pointed out that HVPE-GaN growth with groups' III–V semiconductor materials is completely different in nature. For example, the HVPE synthesis of GaAs, As<sub>4</sub>, and As<sub>2</sub> molecules with volatile and chemical activity formed by thermal decomposition of arsenic compounds can continue to participate in the growth of thin films. But in the process of HVPE-GaN growth, the N<sub>2</sub> molecules formed by NH<sub>3</sub> decomposition are very stable in the temperature range which we are interested in. In fact, HVPE-GaN growth is based on the feasibility of the NH<sub>3</sub> relatively low decomposition, which may be helpful for transporting the reactive nitrogen effectively to the growth surface of substrate [32], to prevent the generation of black-rich Ga GaN film [33]. Another difficulty of HVPE-GaN growth is that there are unforeseen gas-phase reaction, space particles, and wall deposition problems except the formation of GaN.

HVPE growth system generally consists of four parts: the furnace, reactor, gas configuration system, and exhaust gas system. There are two types of design including the horizontal and vertical HVPE system. As shown in the abovementioned disproportionation reaction, HVPE growth system is designed into a dual

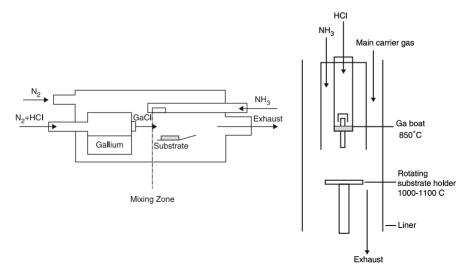

Fig. 1.14 Schematic diagram of (left) horizontal HVPE and (right) vertical HVPE

temperature zone: high- and low-temperature area. Low-temperature zone is used for generating GaCl and high-temperature zone for the deposition for GaN. The growth mechanism in different HVPE system is the same in nature. Figure 1.14 (left) shows the schematic diagram of the horizontal growth system (named as horizontal HVPE) [34], which is widely used in the growth of groups' III–V and II–VI material. At present, most of the reported HVPE for the growth of GaN is based on the horizontal HVPE growth system from RCA laboratory. Figure 1.14 (right) is the schematic diagram of vertical HVPE growth system (named as vertical HVPE) [35], which can improve the uniformity of GaN film by more easily introducing the rotation of the substrate. Substrate can also be dropped down and cooled slowly in ammonia atmosphere, to reduce the decomposition of GaN film.

#### 1.4.3 The Growth and Doping of HVPE Nitrides

One of the difficulties for the growth of high-quality GaN by HVPE is the nucleation on the substrate. A lot of experiments show that the heterogeneous nucleation is very critical for the growth of high-quality GaN. If without any pretreatment, GaN directly on the sapphire is from highly transparent to brown. And the high-temperature growth after depositing the low-temperature buffer layer can often form polycrystalline GaN. Several kinds of different pretreatment, such as GaCl pretreatment of substrate surface and ZnO buffer layer technology [25, 36–38], are used to improve the heterogeneous nucleation density and quality of GaN on sapphire (0001).

In general, HVPE-GaN has the very high intrinsic shallow donor levels, usually in the level of  $10^{18}$ – $10^{20}$  cm<sup>-3</sup>. Therefore, a great deal of doping research has been done for a suitable acceptor dopant to compensate for the donor and for p-type doping to realize the p-n junction. However, as a hot wall epitaxy, HVPE growth is vulnerable to the quartz reactor and gas-phase dopant in the chemical reaction. Some oxide doping agent might be more stable than SiO<sub>2</sub> in thermodynamics. Possible interactions will occur, such as the reduction of quartz reactor components, deposition of oxidized dopant on the pipe wall, and the corrosion of the quartz tube, leading to n-type Si impurities into the epitaxial layer, etc.

Although p-type conductivity has not been obtained, Mg doping in HVPE-GaN has been reported recently [39, 40]. Some studies by ion implantation in GaN show that zinc may be the third choice of shallow acceptor dopant. As a result, most acceptor doping research is focused on the introduction of Zn acceptor [41]. But the large ionization energy zinc acceptor and typically high intrinsic donor level in GaN made Zn doping for GaN p-type conductivity very difficult.

The HVPE technique was proven to be capable to produce n-type, p-type, and semi-insulating material. Hydride vapor-phase epitaxy is not only used to grow GaN but also to grow other nitride compounds (such as InN and InGaN, AlN and AlGaN, etc.) and the doping growth of nitrides.

Cubic GaN Cubic GaN has a unique advantage in the cleavage and doping. But compared with wurtzite GaN, cubic GaN in thermodynamics is metastable and only observed in the film. Several preparation techniques available have been adopted for the growth of cubic GaN, but the quality is very poor, because there is no lattice match suitable substrate. So far, there have been several research reports, using hydride vapor-phase epitaxy technology to grow high-quality cubic GaN thick film [42, 43]. And the most commonly used substrate is GaAs (100), because it can deposit a homogeneous epitaxial layer first on GaAs to modify the surface polishing damage, forming a nitride buffer layer to prevent further intrusion of ammonia gas. At that time, it was generally supposed that a low-temperature buffer layer of GaN could not be grown on a foreign substrate using HVPE system since only non-equilibrium growth system realized a GaN buffer layer. Here, the researchers think that it is necessary to control the lower growth rate (<4  $\mu$ m/h) to prevent the formation of wurtzite GaN [44]. Further work is to obtain a device quality GaN material.

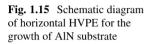

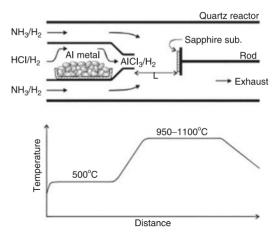

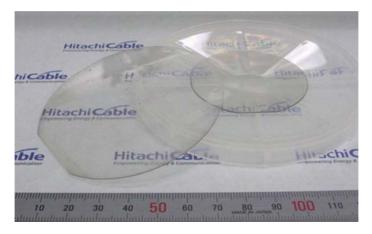

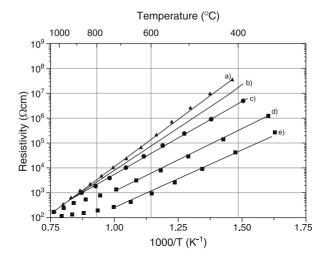

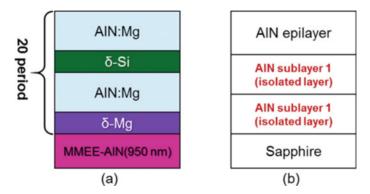

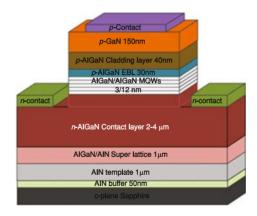

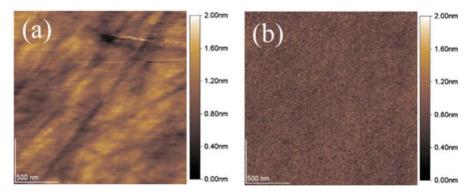

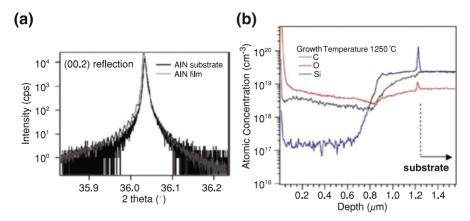

AIN-AIGaN Studies show that the growth of AIN-based nitrides is more complex by hydride vapor-phase epitaxy. The schematic diagram of horizontal HVPE for the growth of AIN substrate is shown in Fig. 1.15. And there are very strong interactions between AICl and hot quartz reactor, which can lead to the excessive impurities introduced into the film and may decrease the quality of quartz reactor. Only a small amount of research has been done about the growth of AIN [45] and AIGaN [46, 47] by hydride vapor-phase epitaxy. Some companies, such as TDI, Crystal IS, The Fox Group, etc., have made progress in the growth of AIN template or AIN substrates by HVPE. Due to patent restrictions of AIN single crystal, TDI turned to the growth of AIN template rather than freestanding AIN substrate, as shown in Fig. 1.16. AIN

**Fig. 1.16** HVPE-AlN templates by TDI Inc. (2 in. AlN-on-sapphire, 3 in. AlN-on-sapphire, 4 in. GaN-on-sapphire, and 6 in. AlN-on-Si from left to right)

template refers to the deposited AlN layer on the heterogeneous substrates, such as Si or sapphire or SiC, for the further epitaxy of AlGaN devices.

The advantage is that the wafer size depends on that of the original substrate. But for the HVPE growth of AlN template compared with the growth by MOCVD and MBE, there is a same problem that serious cracks would be found while the thickness of AlN layer is up to several micrometers. So TDI developed a new stress control technology for the epitaxy of HVPE AlN template. By their self-owned multi-wafer HVPE growth system, they have achieved AlN templates of the thickness of 75  $\mu m$  without cracks. The thickness of 2 in. AlN/SiC template without cracks is up to 10–30  $\mu m$ , and the dislocation density is about 1  $\times$  10 $^7$  cm $^{-2}$ , which is lower one order of magnitude than that of previous AlN/SiC template.

Research on the growth of AlN single crystals has been conducted for decades. Freestanding AlN substrates have been fabricated by sublimation, physical vapor transport (PVT), or sublimation-recombination technique, flux methods, and solution growth. The two most promising techniques are PVT and solution growth.

At present, freestanding AlN substrate with the diameter of more than 1 in. was prepared by HVPE.

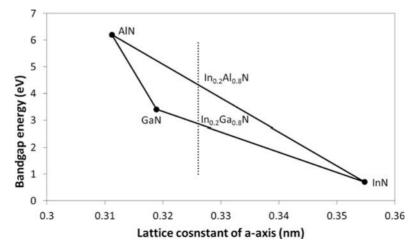

**InN-InGaN** InN and InGaN compounds can extend the bandgap to the visible region of the spectrum. Thermodynamic instability of InN brings serious limitations to the growth of InN-based film. For example, the growth temperature of InGaN is below 800 °C, and the growth of InN is only at temperatures below 650 °C. The growth of stoichiometric InN is very difficult, because the ammonia at that temperature has very low cracking efficiency. Another important problem is that it is obviously impossible to use InCl to grow In-based compounds. Like the HVPE growth of GaN, InCl<sub>3</sub> is stable at low temperature. Presumably, at lower temperatures, an additional product of gas-phase InCl<sub>3</sub>·NH<sub>3</sub> plays a very key role for subsequent InN deposition. Even so, the thermodynamic instability of InN and poor efficiency of ammonia cracking make the growth of InN become very difficult.

#### 1.4.4 The Main Difficulties of HVPE

As is known to all, HVPE-GaN growth has the very high growth rate, for the growth of almost of any GaN orientation can reach 100  $\mu\text{m/h}$  in the order of magnitude, which means that HVPE is possible for the preparation of GaN substrates. But up to now, there are only a few research reports that the HVPE growth of large-scale GaN can be sustained for more than 10 h, and the thickness is rarely more than 10 mm, which is mainly caused by the technical characteristics of HVPE method. The main difficulties of HVPE are as follows:

- Space parasitic reaction. The parasitic reaction outside the substrate in HVPE system under atmospheric pressure is more outstanding than other growth method. A large number of parasitic GaN particles will be deposited on the exit of GaCl tube, the inner wall of quartz glass tube, and the substrate surface. GaN deposited on the exit of GaCl tube will consume GaCl so as to reduce the growth rate and cause the damage of the GaCl tube; GaN particles deposited on the growth surface forming defects will reduce the quality of the material, while GaN deposited on the wall of quartz reactor can cause the breakage of quartz reactor.

- Consumption of liquid gallium source. With the consumption of metal Ga source, the growth rate of GaN will be affected. In the growth process for a long time, the consumption of the gallium source cannot accurately be known, and it is also difficult to add during the growth process. Although we can increase the capacity of Ga container, the weight of Ga is limited at high temperature in quartz glass container. And while the temperature changes between high- and low-temperature changes, the stress from the liquid-solid gallium metal and quartz increases the chances of the breakdown of quartz reactor.

- Ammonium chloride powder. Another technical problem in HVPE method is that the growth reaction under atmospheric pressure will produce large amounts

of ammonium chloride powder, aggregating in the downstream blocking the exit of quartz reactor even to explode, which may affect the growth. The long continuous growth is needed for the growth of GaN boule. Although most of HVPE equipment claims to solve the problem, so far, the continuous growth of HVPE system still is little more than 10 h.

• *Brittle quartz reactor*. The HVPE reactor is usually made of quartz because of the strong corrosive gases. The high price of high-quality quartz material, the precision processing, and the difficulties in installation and maintenance greatly increase the cost, which affects the mass preparation of GaN material.

In spite of the disadvantages, with the deepening of the research, most of the problems can be solved with in-depth research.

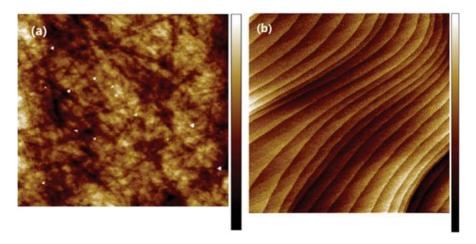

#### 1.4.5 Epitaxial Lateral Overgrowth by HVPE

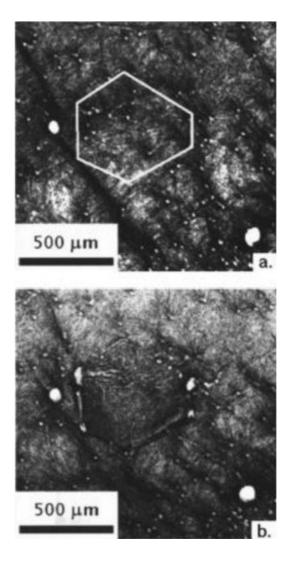

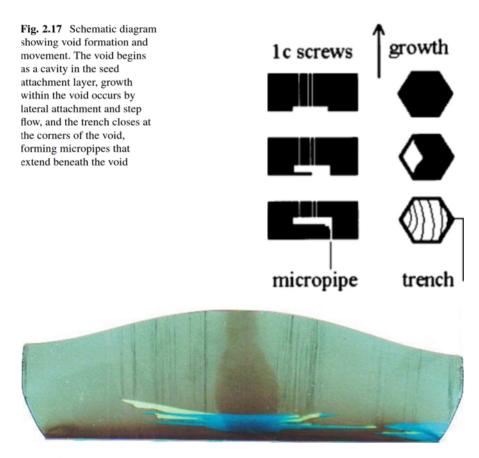

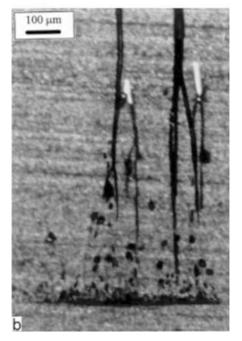

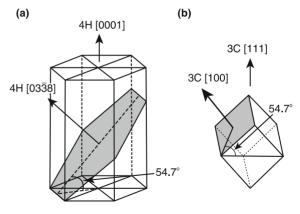

The heterogeneous epitaxial growth of GaN will certainly cause high dislocation density in the epitaxial layer, typically up to  $10^{10}~\rm cm^{-2}$ . A variety of methods have been used to reduce the dislocation density, achieving preliminary results. Compared with other growth technologies such as MOCVD and MBE, HVPE has the potential advantage in preparing large-scale GaN film with low dislocation density. In HVPE-GaN film, several microns of terrace structure and hundreds microns of honeycomb cell structure can often be observed, which all shows that HVPE-GaN growth has the very high ratio of horizontal/vertical growth rate, more suitable to the ELO technology. Using the ELO technology, Japan Nichia greatly improved the life of blue LDs, more than 10,000 h of continuous running.

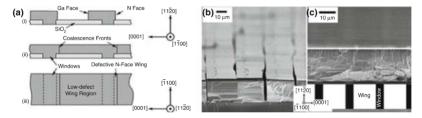

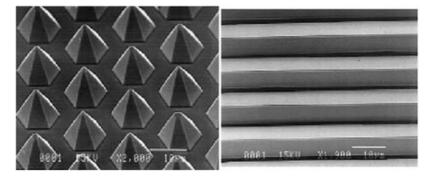

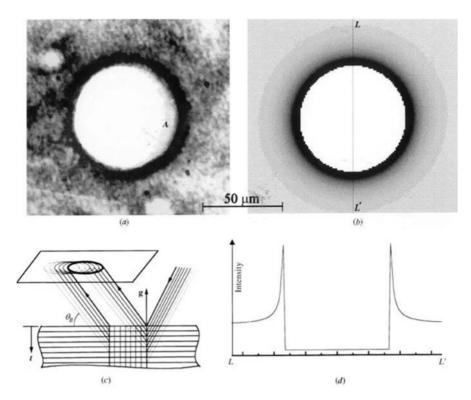

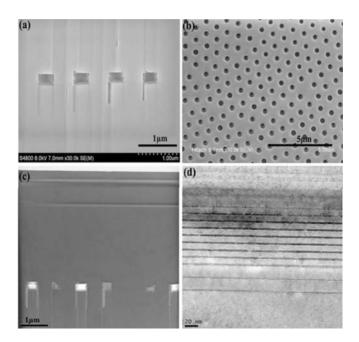

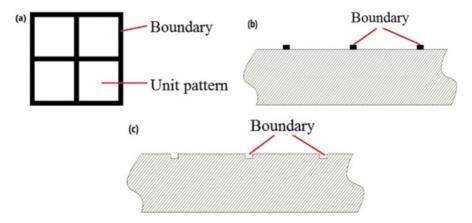

The ELO process is to prepare the patterned masks on HVPE- or MOCVD- GaN layer by applying conventional photolithographic processing or wet etching to 130nm-thick SiO<sub>2</sub> layers deposited by plasma-enhanced chemical vapor deposition. As a result of surface energy choice, GaN is only grown in the window part, and the nucleation on the covered SiO<sub>2</sub> parts is difficult [48, 49]. A variety of mask designs were investigated, including nonparallel stripes arranged in a "wagonwheel" pattern, arrays of circular apertures, parallel stripes oriented along the <0001> direction, parallel stripes oriented along the <1-100> direction, and parallel stripes oriented along higher index directions. When the thickness of epitaxial GaN in the window is more than that of masked SiO<sub>2</sub> layer, the vertical and lateral growth of GaN will happen at the same time. When the lateral growth reaches a certain degree, full cover GaN epitaxial layers can be obtained. Because the growth is quasi-free and perpendicular to the direction of the climbing dislocation from original GaN layer, GaN in the overgrowth regions ("wings") has a high quality. ELO regrowth was carried out under similar growth conditions to those used for the GaN films by HVPE. It was found that masks consisting of parallel stripes oriented along the <1-100> direction exhibited reproducibly vertical stripe sidewalls and

Fig. 1.17 (a) Schematics of HVPE LEO a-plane growth using mask stripes/openings oriented along the GaN <1-100> direction, (b) inclined cross-sectional SEM images of uncoalesced LEO stripes, (c) SEM cross-sectional image of coalesced a-plane LEO GaN film

**Fig. 1.18** SEM images of GaN ELO growth in the hexagonal window and parallel window along the <11-20> direction

thus were most effective to lower the dislocations and stacking-fault densities in the overgrown regions ("wings"), as shown in Fig. 1.17 [50].

ELO is an effective, direct means of significantly reducing the propagation of such defects via blocking and redirection. In a manner analogous to c-plane ELO, the stripe direction, width, and period all play an important role in the morphology and defect reduction during overgrowth. Figure 1.18 is the morphology of ELOG GaN [51]. The experimental results show that the dislocation density of GaN on the SiO<sub>2</sub> mask is several orders of magnitude smaller than that of GaN on window part.

As above mentioned, the biggest characteristic of HVPE system is high growth rate, which is suitable for the growth of GaN thick film. But when the thickness of GaN on sapphire is more than 20  $\mu m$ , the cracks will appear in GaN epitaxial layer. ELO technology can effectively alleviate the phenomenon, thus obtaining low-density, large-scale high-quality GaN thick film. In order to further improve the quality of ELO epitaxial layer, new methods have been tried. For example, two-step ELO growth of GaN is one of them, mainly considering that the lateral growth depends on the conditions, such as temperature, carrier gas flow rate, and V/III ratio. The ELO growth is first carried out at a relatively low V/III ratio in order to produce smooth vertical {11–20} interface and then at a higher V/III ratio to promote the lateral growth [52]. Another double-layer ELO technology is used to reduce the

Fig. 1.19 SEM micrographs of GaN by pendeo-epitaxial regrowth

dislocations in the interface of lateral GaN on SiO<sub>2</sub> mask, by changing the direction of second ELO GaN after the first ELO.

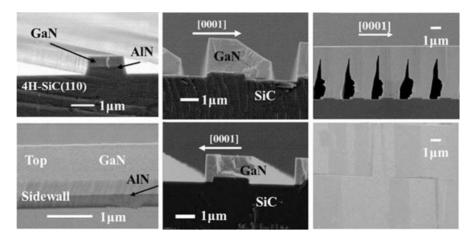

In addition, the pendeo-epitaxy growth technology is also very attractive. It is a technique of lateral epitaxy without mask, which is usually on SiC or SiC/Si heterogeneous substrate, using AlN buffer layer as the mask [53]. After etching out part of AlN layer, GaN is not directly grown on SiC substrate but only selective epitaxial growth on the AlN layer. GaN grow up along the longitudinal and lateral directions at the same time, and with the increase of the thickness, the front of lateral epitaxial growth also laterally extends. Because GaN cannot be grown on SiC substrate between adjacent AlN films, it seems that the lateral spreading of GaN on AlN layer is impending, like GaN crystals hanging on both sides of AlN, so-called pendeo-epitaxy. Figure 1.19 shows SEM images of GaN by pendeo-epitaxy process. The characteristic of the pendeo-epitaxy technology avoids the effect of the mask on ELO GaN, especially the impurity and the interface stress, leading to a higher quality of GaN.

#### 1.4.6 Freestanding HVPE-GaN Substrate

An alternative approach for GaN homo-substrates for a long time is the use of thick GaN layers grown by hydride vapor-phase epitaxy on sapphire. These thick layers are subsequently removed from the sapphire substrate by a suitable process and then can serve as quasi homo-substrates for device fabrication. Currently, hydride vapor-phase epitaxy (HVPE) provides the highest growth rate of GaN single crystals, reaching 1 mm/h or more. In addition, because the growth is usually performed at atmospheric pressure, large-scale HVPE reactors are available. For these reasons,

HVPE has considerable advantages for the mass production of large-area GaN crystals for freestanding wafers.

However, the process can suffer from serious problems of cracking of the thick GaN layer due to the large mismatch in the thermal expansion coefficients between GaN layer and the base substrate. Despite strenuous attempts to overcome this problem, difficulties still exist in reproducibly manufacturing GaN crystals that have a sufficiently large area for practical use. Reducing the density of dislocations is another important issue, because the HVPE method still involves hetero-epitaxial growth on a foreign substrate with a large lattice mismatch.

Here is to summarize the present state of research concerning such freestanding GaN homo-substrates, with special emphasis on laser-induced liftoff process and self-separation methods for the separation of the thick GaN layers from their sapphire substrates.

Because thick HVPE-GaN layers are generally hetero-grown on sapphire, a highly desirable process is required to enable a fast, reliable, and high-yield detachment. In practice, such a process will involve a sacrificial layer somewhere between the substrate and GaN layer, which is removed by a specific chemical or thermal treatment. One possibility would be to deposit a sacrificial layer which makes use of selective chemical etching, e.g., of AlN versus GaN in KOH. Another method is developed to cause GaN films to self-detach from its sapphire substrate during cooldown from growth temperature due to the accumulation of thermal stress and the lattice mismatch between GaN and sapphire. A third approach is the complete removal of the substrate by etching or polishing, which is quite time-consuming, especially in the case of sapphire or SiC substrates.

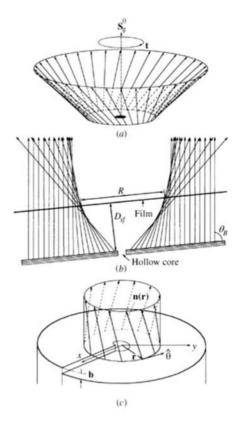

#### 1.4.6.1 Laser Liftoff Process

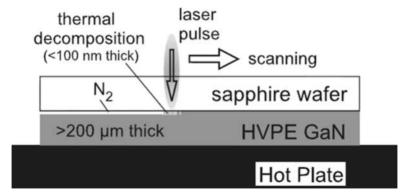

Another useful process, much more flexible and significantly faster than the abovementioned methods, is the laser-induced delamination from a transparent substrate such as sapphire, or laser liftoff (LLO). In this process, the separation of a GaN layer from the substrate is achieved by irradiation of the substrate-film interface through the substrate with high-power excimer laser pulses at a wavelength which is transmitted by the substrate but is strongly absorbed in the GaN layer [54]. The absorption of such high-intensity laser pulses causes a rapid thermal decomposition of the irradiated GaN interfacial layer into metallic Ga and gaseous N<sub>2</sub> (Fig. 1.20) [55]. High-intensity laser pulses enter the sample via the sapphire substrate and thermally decompose a thin GaN layer at the substrate interface. The energy density of laser pulses is often in the range between 400 and 900 mJ/cm<sup>2</sup>, and the threshold is approximately 250 mJ/cm<sup>2</sup>. Below this critical absorbed pulse intensity threshold, no visible alteration of GaN layer can be seen. A hot plate can be used to raise the substrate temperature during the process, in order to relieve some of the accumulated thermal strain. The temperature of hot plate is usually above 730 °C but below 830 °C (decomposition temperature of GaN). At this temperature range, the strain and the bowing were visibly reduced and hardly noticeable. Ideally,

Fig. 1.20 Schematic view of the laser liftoff (LLO) process

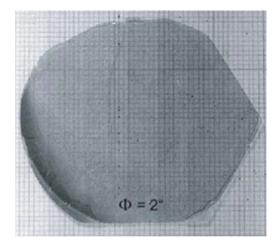

**Fig. 1.21** Photograph of a 275-μm-thick freestanding GaN film, after removal from 2 in. sapphire

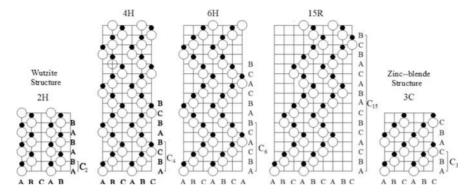

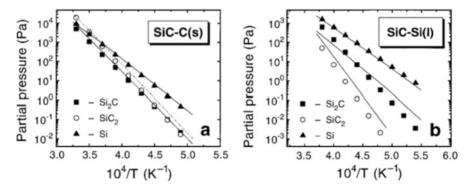

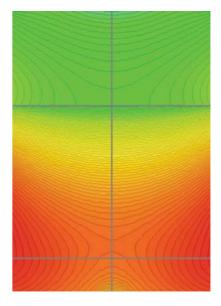

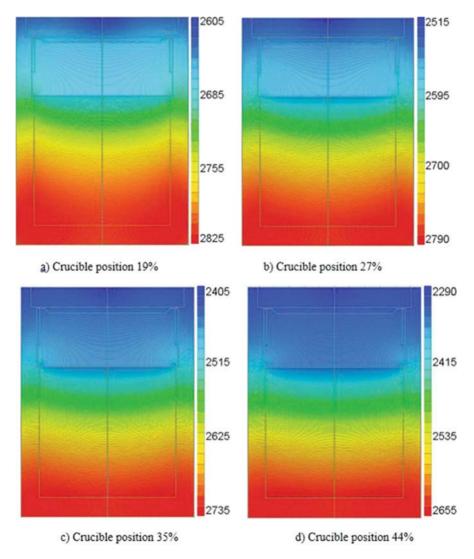

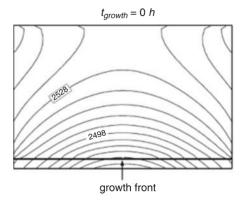

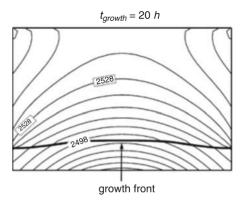

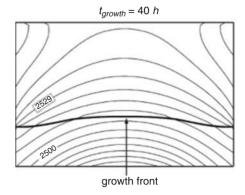

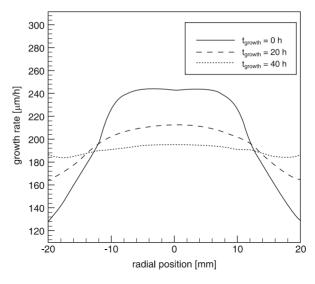

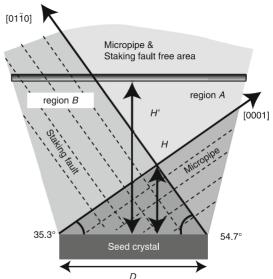

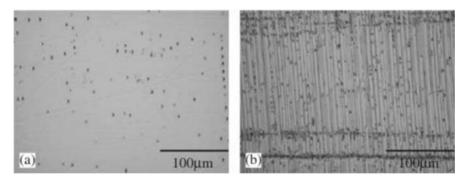

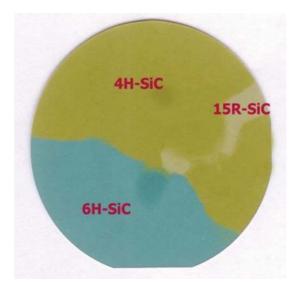

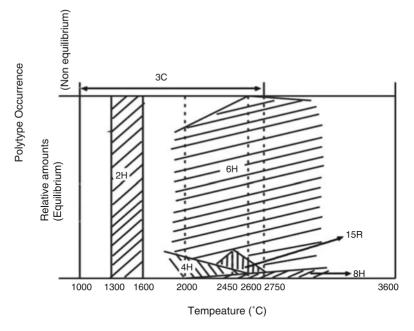

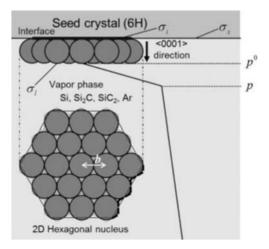

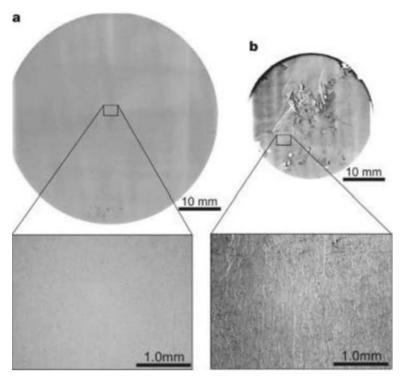

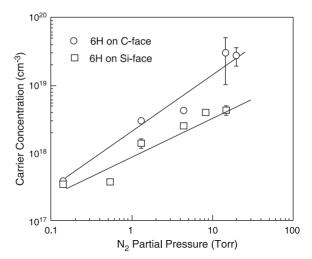

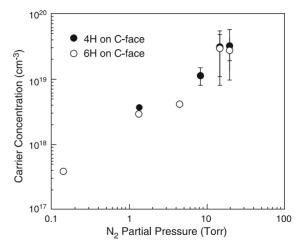

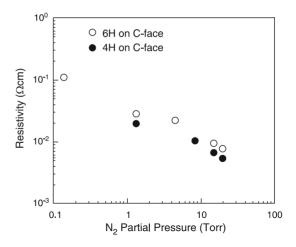

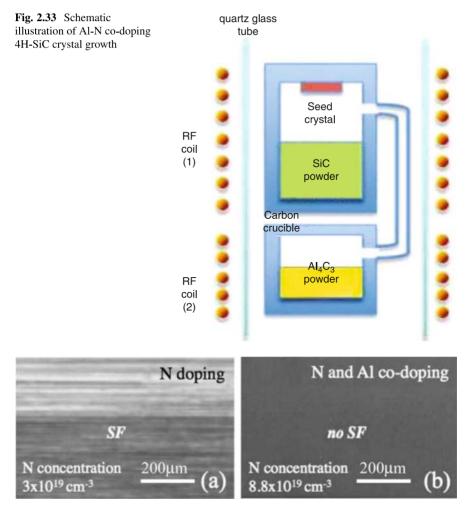

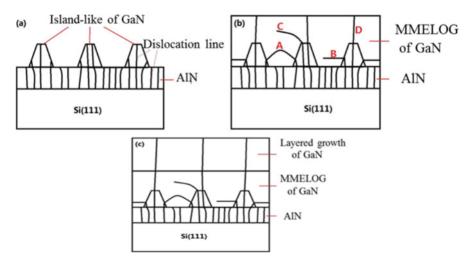

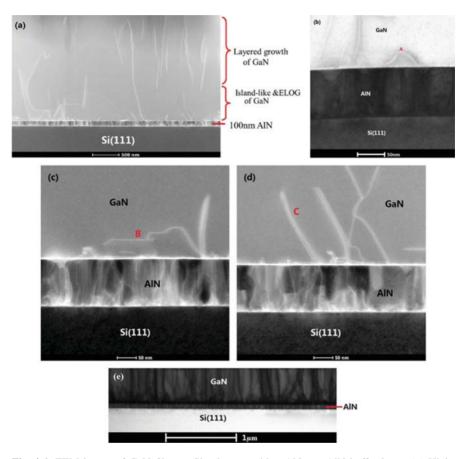

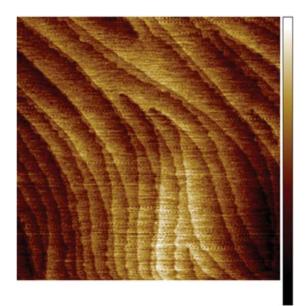

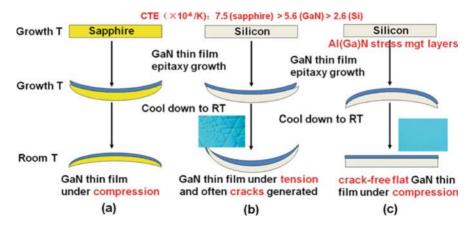

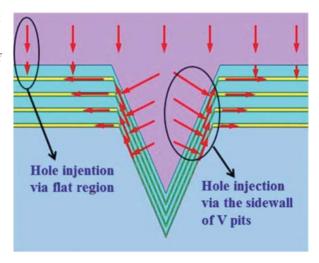

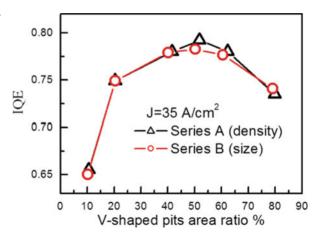

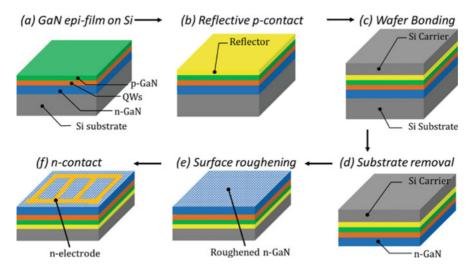

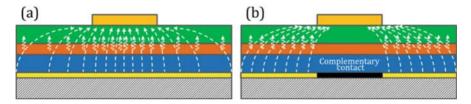

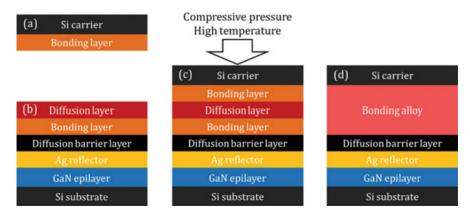

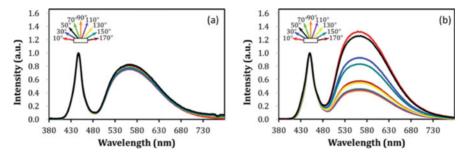

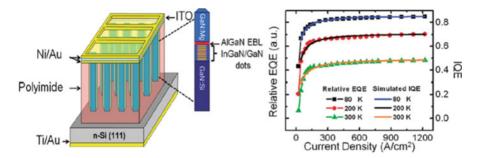

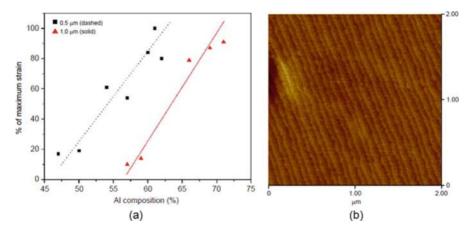

in situ laser liftoff in the deposition reactor close to growth temperature would be the best solution to avoid all bowing or cracking problems caused by the thermal expansion mismatch between GaN and the sapphire substrate.