## 3D IC Devices, Technologies, and Manufacturing

# 3D IC Devices, Technologies, and Manufacturing

**Hong Xiao**

**SPIE PRESS**

Bellingham, Washington USA

### Library of Congress Cataloging-in-Publication Data

Names: Xiao, Hong, 1961- author

Title: 3D IC devices, technologies, and manufacturing / Hong Xiao. Description: Bellingham, Washington, USA: SPIE, [2016] | Includes

bibliographical references and index.

Identifiers: LCCN 2016006975 (print) | LCCN 2016014372 (ebook) | ISBN

9781510601468 (softcover) | ISBN 9781510601475 (pdf) | ISBN 9781510601482

(epub) | ISBN 9781510601499 (mobi)

Subjects: LCSH: Three-dimensional integrated circuits.

Classification: LCC TK7874.893 .X53 2016 (print) | LCC TK7874.893 (ebook) |

DDC 621.3815--dc23

LC record available at http://lccn.loc.gov/2016006975

### Published by

SPIE

P.O. Box 10

Bellingham, Washington 98227-0010 USA

Phone: + 1 360.676.3290 Fax: + 1 360.647.1445 Email: books@spie.org Web: http://spie.org

Copyright © 2016 Society of Photo-Optical Instrumentation Engineers (SPIE)

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means without written permission of the publisher.

The content of this book reflects the work and thought of the authors and editor. Every effort has been made to publish reliable and accurate information herein, but the publisher is not responsible for the validity of the information or for any outcomes resulting from reliance thereon.

Printed in the United States of America.

The image of the 3D V-NAND memory chips on the cover has been provided by Samsung Electronics.

This book is dedicated to my wife, Liu Huang; my sons, Jarry and Colin; and my parents, Xian-ci Xiao and Hong-ting Zhou.

此书献给

父母: 萧先赐, 周宏廷

妻子: 黄柳

儿子: 萧嘉瑞, 萧凯瑞

## **Table of Contents**

| Pr | etace                                                |                                                      | İΧ  |  |

|----|------------------------------------------------------|------------------------------------------------------|-----|--|

| 1  | Manufacturing Processes of 3D IC Devices             |                                                      |     |  |

|    | 1.1                                                  | Introduction                                         | 1   |  |

|    | 1.2                                                  | 3D Devices in the DRAM and BWL DRAM Process          | 3   |  |

|    |                                                      | 1.2.1 DRAM introduction                              | 3   |  |

|    |                                                      | 1.2.2 3D devices in DRAM                             | 3   |  |

|    |                                                      | 1.2.3 BWL DRAM manufacturing processes               | 12  |  |

|    | 1.3                                                  | Brief Summary of DRAM                                | 44  |  |

|    | 1.4                                                  | Review Questions                                     | 48  |  |

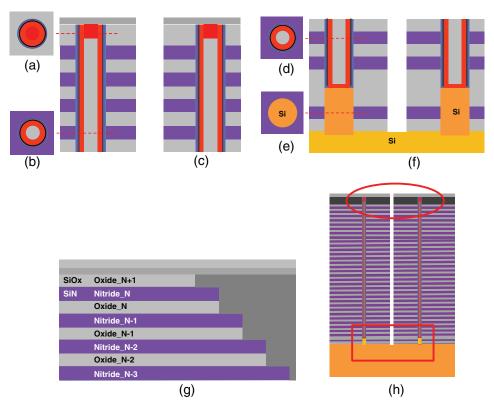

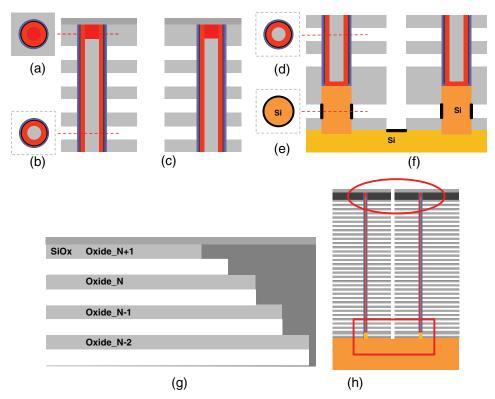

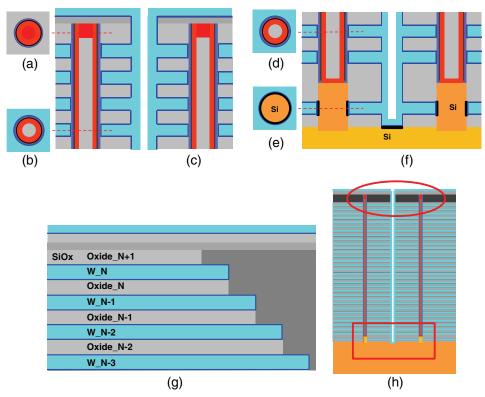

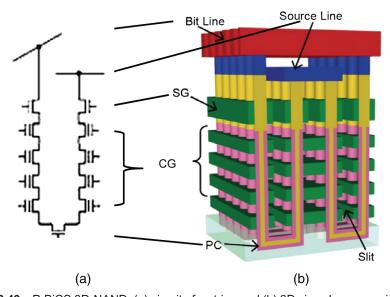

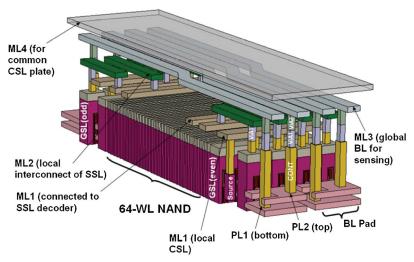

| 2  | 3D-NAND Flash and Its Manufacturing Process          |                                                      |     |  |

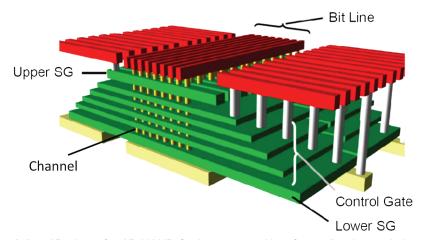

|    | 2.1                                                  | Introduction                                         | 49  |  |

|    | 2.2                                                  | 3D-NAND Flash Memory Manufacturing Processes         | 55  |  |

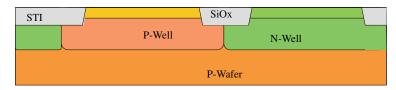

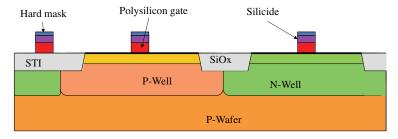

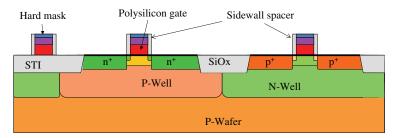

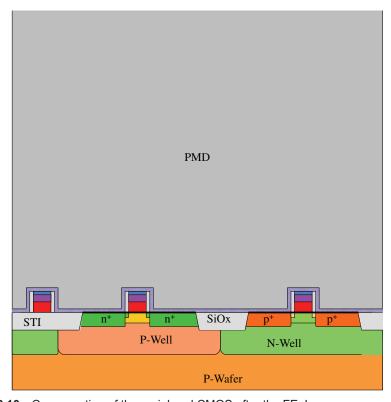

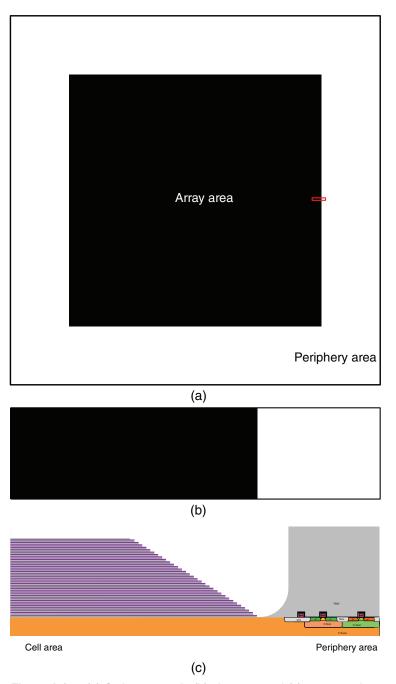

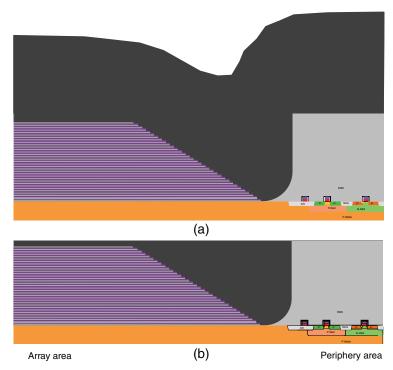

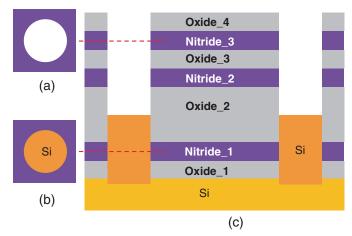

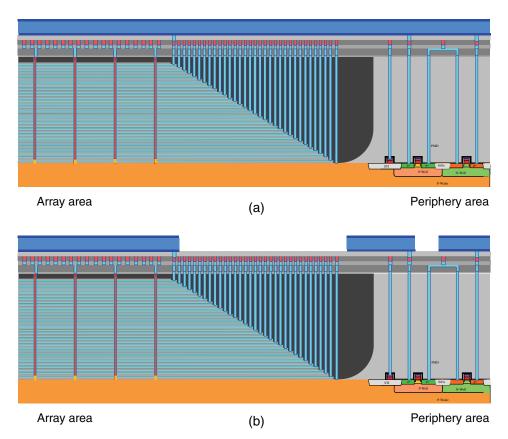

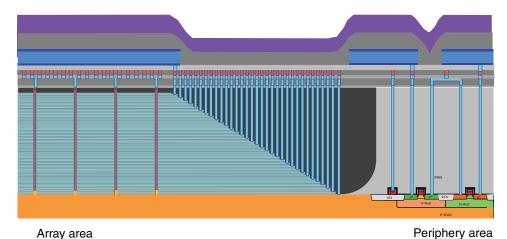

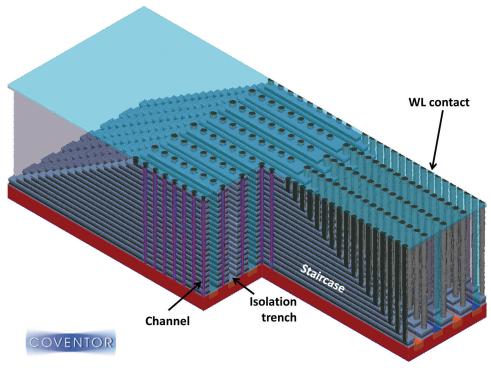

|    |                                                      | 2.2.1 Peripheral module                              | 55  |  |

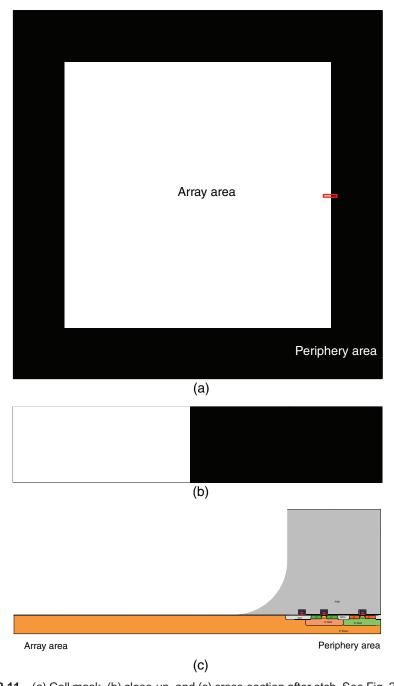

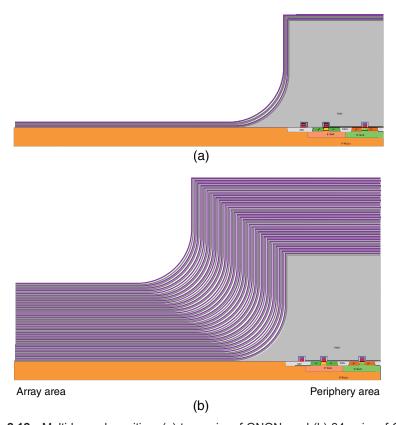

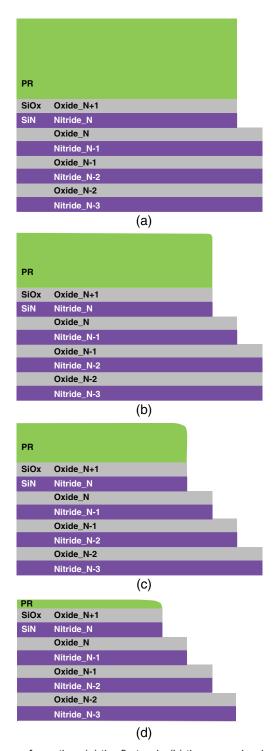

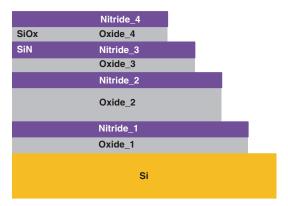

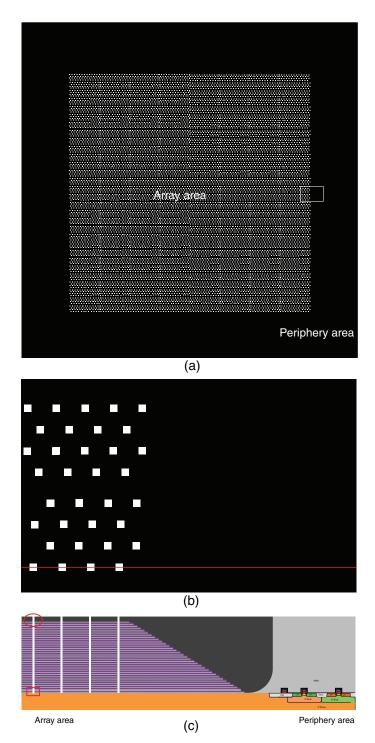

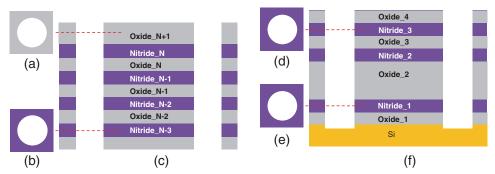

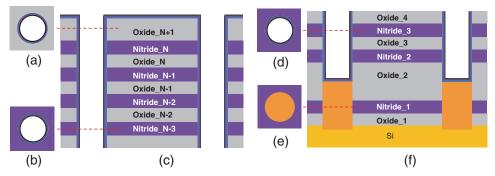

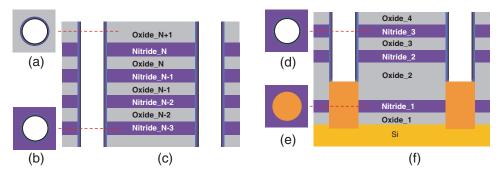

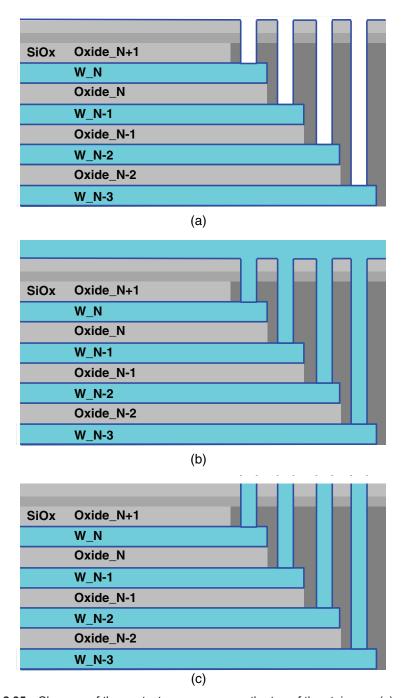

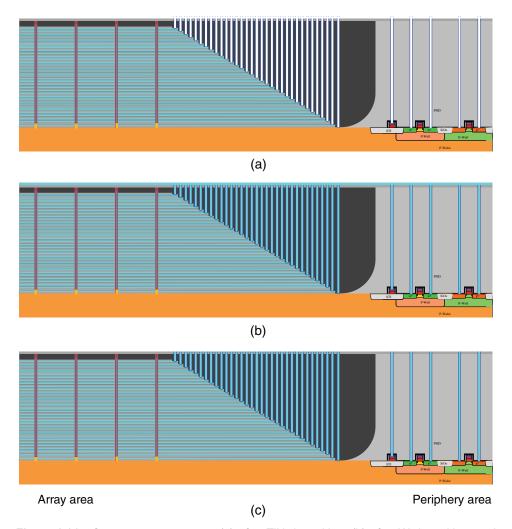

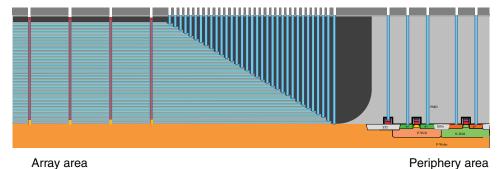

|    |                                                      | 2.2.2 Multi-layer deposition and staircase formation | 58  |  |

|    |                                                      | 2.2.3 Channel module                                 | 61  |  |

|    |                                                      | 2.2.4 Isolation module                               | 71  |  |

|    |                                                      | 2.2.5 Contact and interconnection modules            | 79  |  |

|    | 2.3                                                  | 3D-NAND Summary and Discussion                       | 87  |  |

|    | 2.4                                                  | Review Questions                                     | 94  |  |

| 3  | High-k, Metal-Gate FinFET CMOS Manufacturing Process |                                                      |     |  |

|    | 3.1                                                  | Introduction                                         | 97  |  |

|    | 3.2                                                  | FinFET Basics                                        | 99  |  |

|    | 3.3                                                  | FinFET Process                                       | 101 |  |

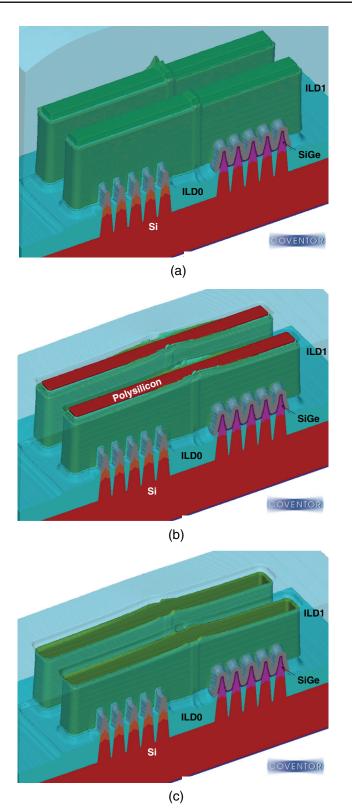

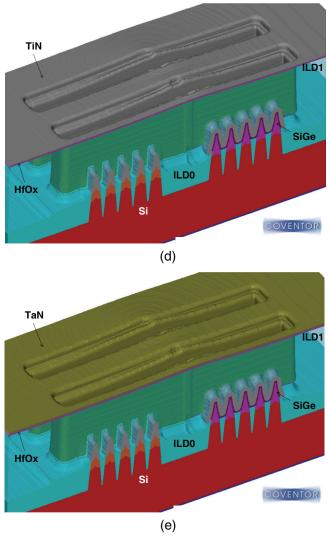

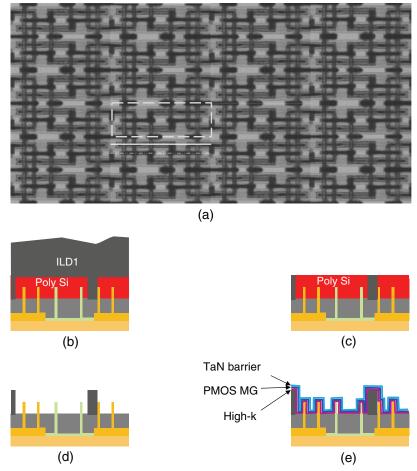

|    | 3.4                                                  | .4 Advanced FinFET CMOS Process                      |     |  |

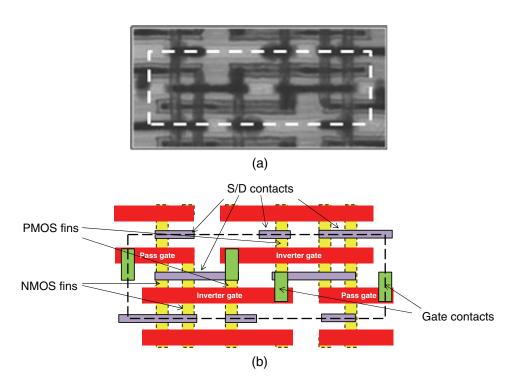

|    | 3.5                                                  | Advanced FinFET SRAM                                 | 122 |  |

|    | 3.6                                                  | 3                                                    | 148 |  |

|    | 3.7                                                  | Review Questions                                     | 150 |  |

| 4  | Summary and Future Trends of the 3D IC Process       |                                                      |     |  |

|    | 4.1                                                  | Scaling MOSFET Technology after 14 nm                | 153 |  |

|    | 4.2                                                  | Scaling and Development of Memory Devices            | 160 |  |

|    | 4.3                                                  | 3D Packaging                                         | 168 |  |

| viii       |     |                                                  | Table of Contents |

|------------|-----|--------------------------------------------------|-------------------|

|            | 4.4 | Other 3D Devices and 3D IC Processing Techniques | 173               |

|            | 4.5 | The End of Moore's Law?                          | 177               |

| References |     | 181                                              |                   |

| Index      |     | 187                                              |                   |

### **Preface**

My first exposure to the semiconductor industry was in 1975 at the Microwave Diode Department of Chengdu Guoguang Electric Co. with my middle-school classmates during a month-long "learn from workers" program [very common for Chinese children during the chaotic period of the "Cultural Revolution" (1966–1976)]. The silicon wafer size was 1 inch, and we were making crystal diodes used in radar as a microwave detector. The factory had several process bays, such as diffusion, wet clean, wafer dicing, assembly, and final test. I watched workers push the wafers into the pyrogenic oxidation furnace and was amazed by the barely visible bluish hydrogen flame in it. I still remember the story of a hydrogen-leakage-induced explosion told during safety training. I worked in final test, using a special instrument to test the diode and determine whether it passed or needed to be thrown into the trash bin underneath the tester.

Twenty years later, I started my career in the semiconductor industry. The wafer size at that time was 200 mm, and the technology node was 350 nm. When the first edition of my textbook *Introduction to Semiconductor Manufacturing Technology* was published by Prentice Hall in 2000, the technology had scaled down to 180 nm, and copper metallization was the state-of-the-art technology.

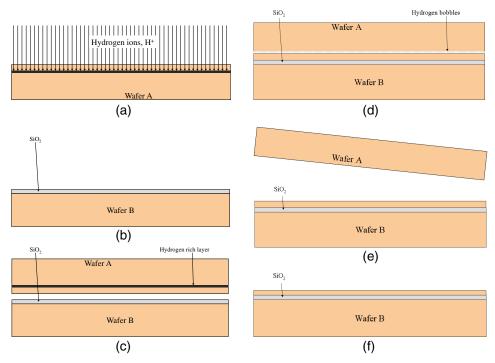

Ten years after publication of the first edition, the wafer size increased to 300 mm, and the technology node migrated to 32 nm. New technologies that were not mentioned in the first edition, such as immersion lithography, double patterning, selective epitaxial growth (SEG), and atomic layer deposition (ALD), were widely used to manufacture IC chips with high-k, metal-gate front-end and copper, ultra-low-k back-end. It became the main driving force for me to write the second edition of the book.

There are many new developments since I have summited the final manuscript of the second edition in the spring of 2012. Because simply scaling down the feature size of the planar MOSFET can no longer improve the device performance while reducing its power consumption, scientists and engineers have worked on scaling nanometer-scale electronic devices in the third dimension. FinFET technology is one such proposed device architecture that has been used to replace planar MOSFET technology. At the same

x Preface

feature size, FinFETs can improve the drive current by increasing the effective gate width at on-state while reducing standby leakage by operating with a fully depleted regime at off-state. Theoretically, FinFETs can migrate to the next-generation-technology node by just increasing fin height without shrinking the feature size. Because it is easier to control the fin height of the FinFET with the silicon thickness of the silicon-on-insulator (SOI) substrate, it was thought that FinFETs needed a SOI wafer. Due to the high cost of SOI wafers and the difficulties of fin height control with low-cost bulk-silicon wafers, many people regarded FinFET technology as a high-risk approach for the 22-nm or 20-nm technology node, even as late as 2009. In the summer of 2012, Intel announced its 22-nm FinFETs at the Symposium on VLSI Technology. Although FinFET technology was mentioned in the second edition published by SPIE Press at the end of 2012, it was not elaborated upon due to the lack of credible information about its manufacturing processes.

In recent years, the manufacturing technology of non-volatile memory (NVM), especially NAND flash memory, has developed rapidly, driven by the demands of data storage for mobile electronics devices, such as smartphones, tablet PCs, digital cameras/camcorders, etc. Multiple patterning is required to manufacture the planar NAND flash-memory chips due to the limitation of 193-nm immersion lithography. The cost of triple patterning or quadruple patterning required by the low-teen-nm planar NAND flash will become too high, and scientists and engineers have proposed and developed an alternative vertical NAND or 3D-NAND technology that utilizes the gateall-around vertical transistors to stack multiple memory cells in the vertical direction. In 2014, Samsung released a solid state drive (SSD) based on 3D-NAND with 32 stacks of NVM—only seven years after Toshiba published the concept. A SSD with 48-stack 3D-NAND is also available on the market. With 3D-NAND architecture, one can scale to a next-generation-technology node by increasing the number of stacks without shrinking the feature size. The second edition of Introduction to Semiconductor Manufacturing Technology mentions 3D-NAND in the last chapter, which discusses future trends. The future becomes reality in a very short time.

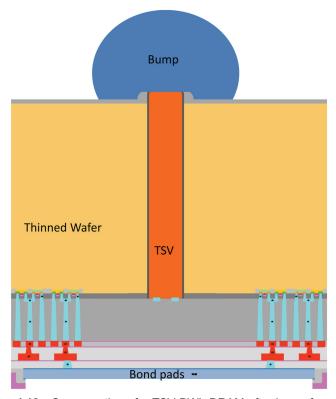

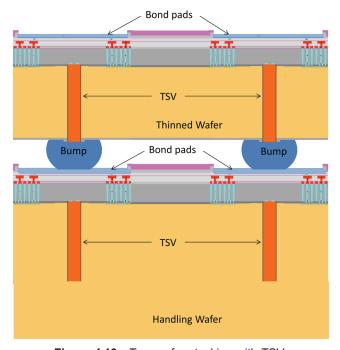

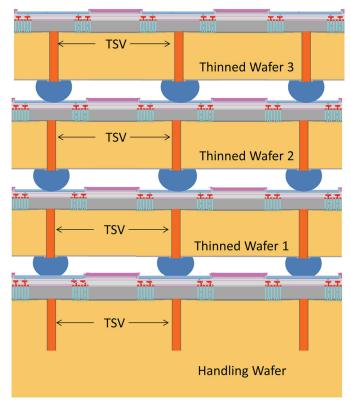

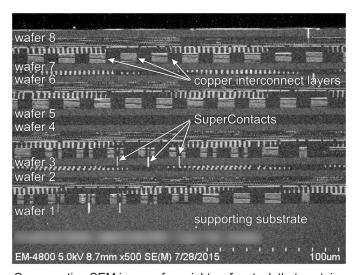

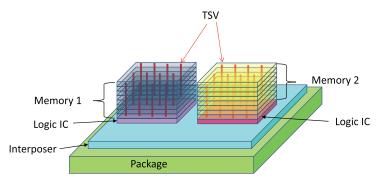

Another technology mentioned in the second edition but not described in detail is 3D packaging with through silicon via (TSV). By stacking multiple chips with TSV, one can increase the device density without shrinking the feature size, which has been limited by the capability of 193-nm immersion lithography technology and the delayed implementation of extreme ultraviolet (EUV) lithography. TSV has long been applied in CMOS image sensor packaging, which forms the tiny camera assembly used in mobile phones, tablets, and laptops. TSV wafer stacking requires very high yield for every wafer that is to be stacked; otherwise, the combined final yield will suffer. Although foundries are still proposing 2.5D packaging with an interposer due

*Preface* xi

to the high cost of TSV 3D packaging, Samsung released the first 3D TSV technology based on DDR4 modules for enterprise servers in 2014.

Many people helped me acquire the information and knowledge needed to write this book; many of them helped me by answering my questions, and some of them helped by asking me questions to which I had no clear answer at that moment, which motivated me to further study and research: Dick James, Oliver Paterson, Hanming Wu, Jong (John) Chen, Chih-Ming Ke, David Fried, Sandy Wen, Jay Guan, Xiaodong Wang, Victor Lim, Byoung-Ho Lee, Ming Lei, Qiang Zhao, Kevin Huang, Jeff Zhang, Wee Teck Chia, Takuji Tada, Jeff Barnum, Christina Wang, Paul MacDonald, Chris Mahr, Brian Duffy, Harsh Shiha, Rohan Gosain, Arun Lobo, Neeraj Khanna, Amir Azordegen, and Cecelia Campochiaro, just to name a few.

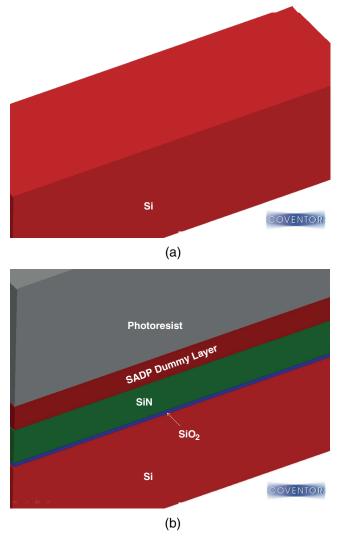

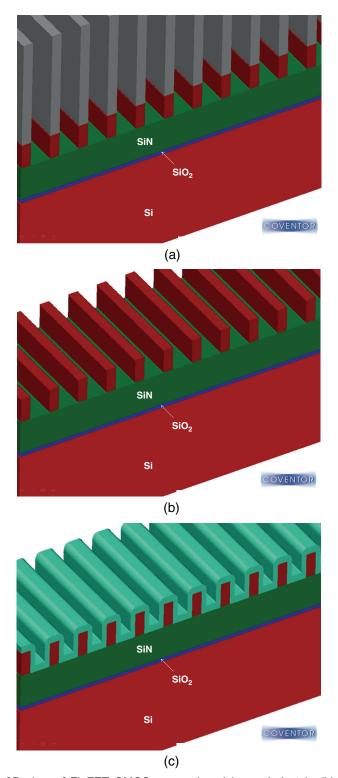

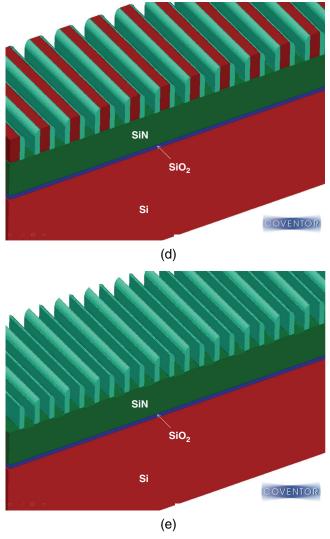

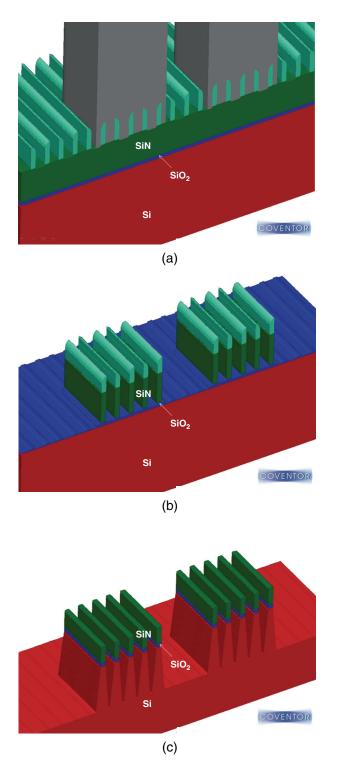

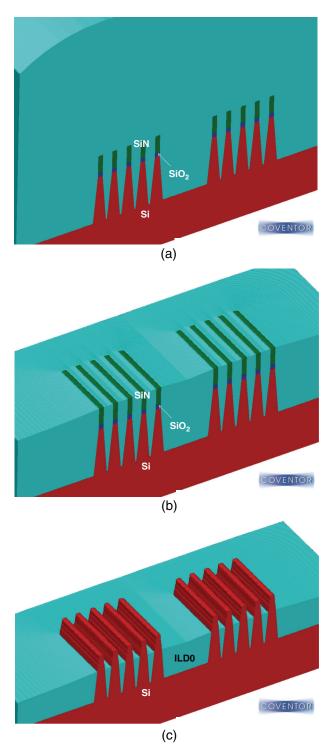

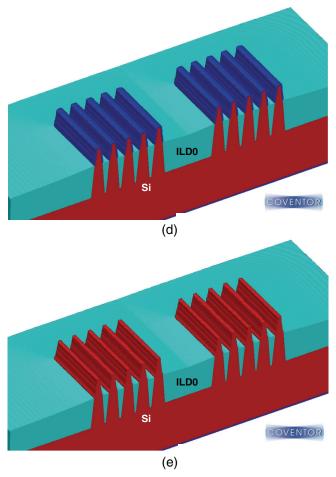

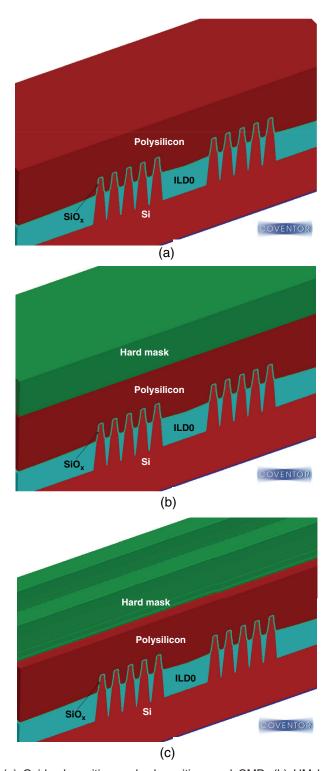

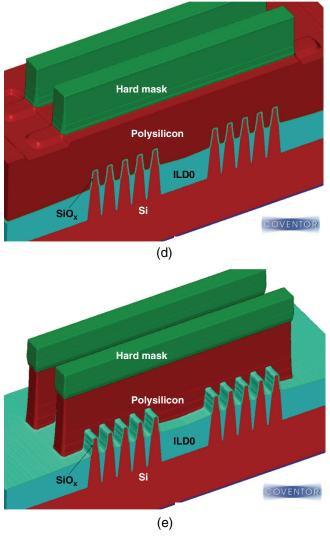

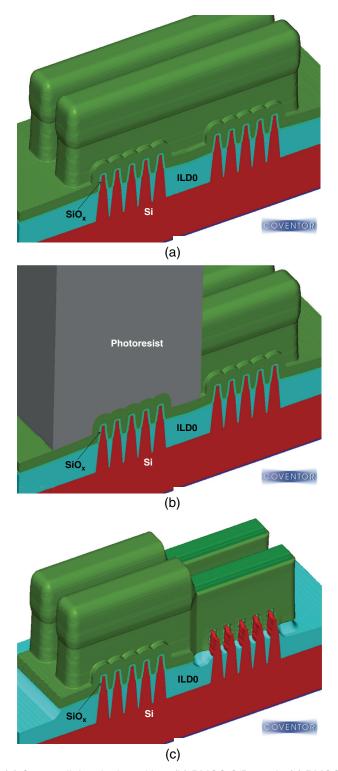

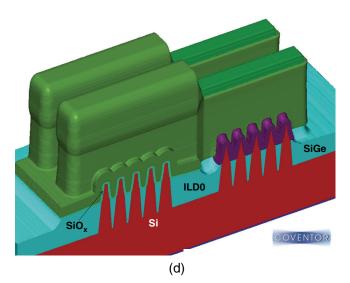

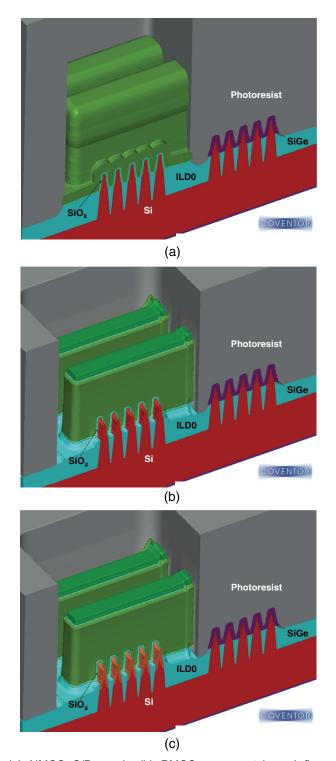

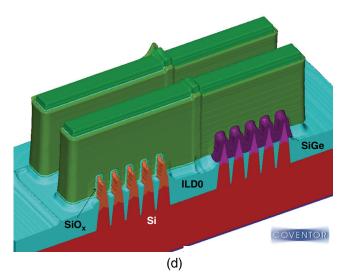

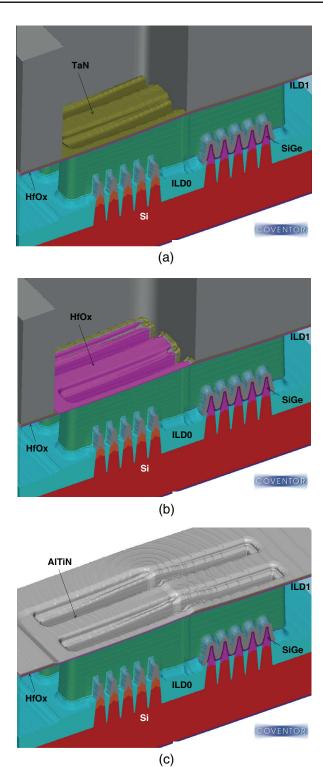

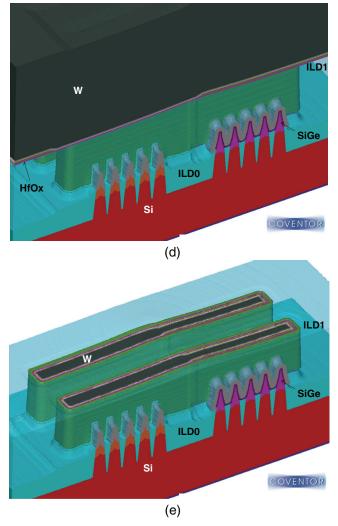

The image of the 3D V-NAND memory chips on the cover has been provided by Samsung Electronics. Figures 1.10(b)–(c) and 2.48 are provided by Coventor. Figures 3.9–3.17, used to describe the HKMG FinFET processes, were previously published in TechDesign Forums.\* These images were generated using Coventor's SEMulator3D virtual-fabrication software platform.

Colin Xiao, Jarry Xiao, Sameet Shriyan, and Shishir Ramprasad helped me proofread the draft and corrected many English errors. Without the support of my wife, Liu (Lucy) Huang, and sons, Jarry and Colin, it would have been impossible to write and finish this book on time.

My generation grew up in China without television. Thanks to the "Cultural Revolution," there were very few movies for kids in China at that time. So, hungry for movies, I watched anything that projected on the screen. One such film I watched many times was "Mechanical Drawing," an educational film for college students at the Chengdu Institute of Radio Engineering (currently the University of Electronics Science and Technology of China), where my parents worked as professors. Even today, I can still vividly remember this film taught me how a 3D object can be presented by a top view, side view, and face view. The 3D concept and its presentation with a 2D drawing helped me tremendously when I took an IC design class in graduate school. [IC layout is essentially the top view of mechanical drawing with a microscopic scale (maybe it should be called nanoscopic scale now)]. This knowledge was really useful for me to reconstruct the 3D structures of IC devices and figure out the manufacturing processes by correlating the top-view images and cross-section images. I really appreciate the person who showed the film and allowed me, an elementary schooler, to watch it with college students.

> Hong Xiao March 2016

<sup>\*</sup>http://www.techdesignforums.com/practice/technique/finfet-iedm-tipsheet

## 3D IC Devices, Technologies, and Manufacturing

# Chapter 1 Manufacturing Processes of 3D IC Devices

### 1.1 Introduction

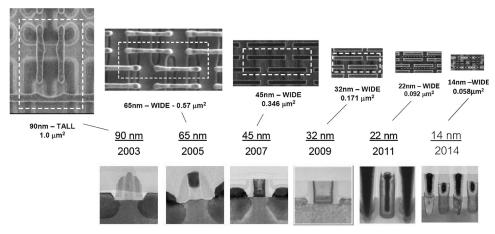

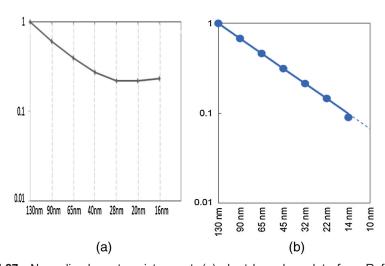

The scaling of integrated circuit (IC) chips becomes more and more challenging as IC technology pushes the feature size deep into the nanometer (nm) technology nodes. To extend the scaling, engineers and scientists tried to not only shrink the feature size in the *x* and *y* directions but also push IC devices into the third dimension. It took 14 years from the first publication of fin-shaped field effect transistors (FinFETs)<sup>1</sup> to high-volume manufacturing (HVM) of 22-nm FinFET IC chips in 2012.<sup>2</sup> In 2014, the first 3D-NAND-based solid state drive (SSD) was introduced to the market,<sup>3</sup> only seven years after the first publication.<sup>4,5</sup>

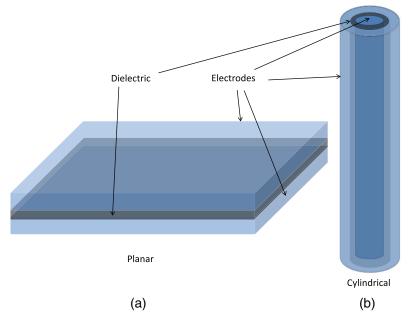

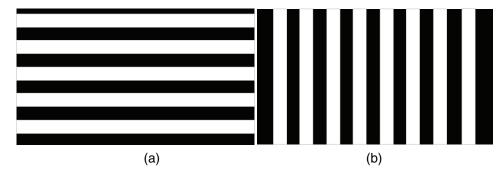

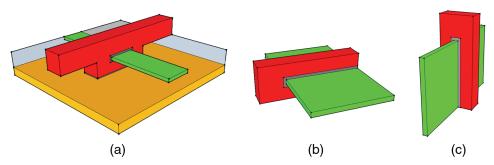

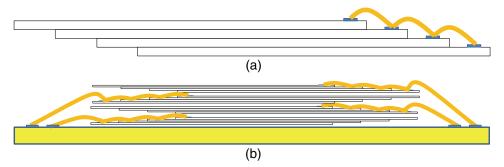

The same electrical performance and a significantly smaller footprint (equivalent to feature-size scaling) can be achieved by changing the IC device from a two-dimensional (2D) planar structure to a 3D structure. Figure 1.1 shows this effect for capacitors: Fig. 1.1(a) is a planar capacitor, and Fig. 1.1(b) is a cylindrical capacitor with the same capacitance. It is well-known that capacitance C = kA/d. Here, k is the constant and d is the thickness of the dielectric between the two electrodes, and A is the area of the electrode. The top-down area of the cylindrical capacitor is much smaller on the wafer surface than that of the planar version. Increasing the height of the cylinder can further reduce the top-down area of the capacitor while keeping the capacitance unchanged. This is the main reason why DRAM chips have used cylindrical capacitors, either stacked or deep-trench, for a long time.

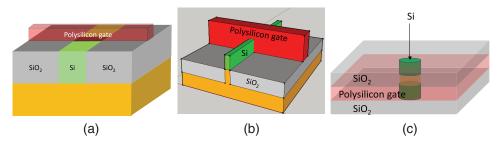

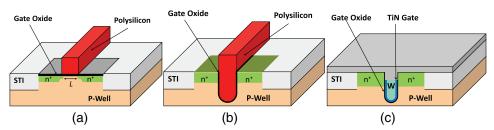

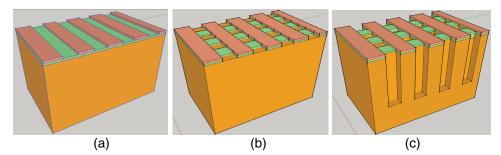

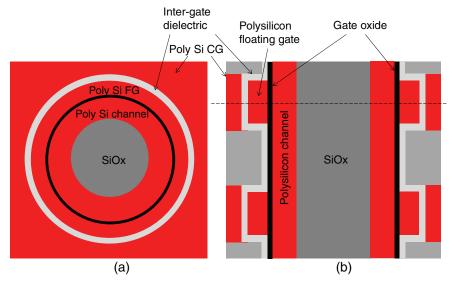

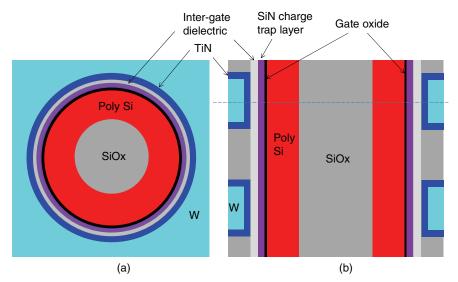

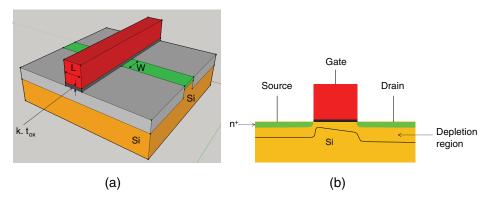

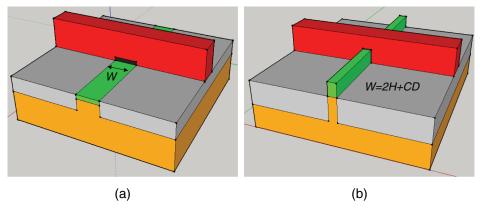

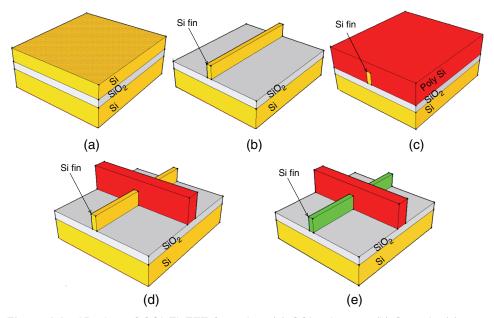

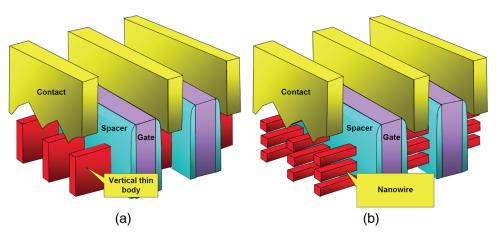

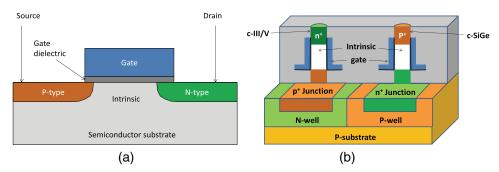

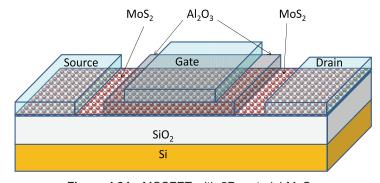

Figure 1.2 illustrates three types of metal-oxide semiconductor (MOS) field effect transistors (FET, or MOSFET). Figure 1.2(a) is a 2D planar MOSFET, Fig. 1.2(b) is a FinFET, which is a 3D device, and Fig. 1.2(c) is another 3D device, a vertical gate-all-around (GAA) MOSFET, or a silicon nano-wire device. The three devices have a similar gate critical dimension (CD) with a similar footprint; however, the channel width of the planar MOSFET is the narrowest and thus has the lowest drive current. The FinFET

Figure 1.1 (a) Planar capacitor and (b) 3D cylindrical capacitor.

Figure 1.2 (a) Planar MOSFET, (b) FinFET, (c) and vertical gate-all-around device.

channel width is two times the fin height plus the fin top CD, whereas the GAA channel width is the circumference of the channel pillar.

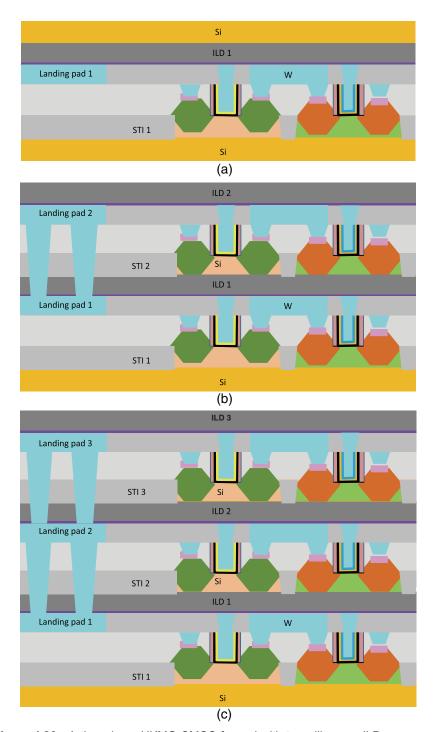

This book explains the advantages of the 3D devices and their applications in dynamic random access memory (DRAM), 3D-NAND flash, and advanced-technology-node complementary MOS (CMOS) IC. The development of DRAM cell transistors and storage node (SN) capacitors of the DRAM, as well as the detail-manufacturing process flow of the most-advanced buried word line (BWL) DRAM, are discussed in Chapter 1. The 3D-NAND flash process flow is described in detail in Chapter 2, and step-by-step 3D FinFET CMOS IC devices are discussed in Chapter 3. Chapter 4 addresses the scaling trends of CMOS logic and memory IC before providing a brief summary. Devices that may be used in the "post-CMOS" era are also discussed. Other topics briefly mentioned include 3D technologies such as 3D wafer process integration of silicon-on-inter-layer dielectric (ILD) and TSV-based 3D packaging.

### 1.2 3D Devices in the DRAM and BWL DRAM Process

After reading this chapter, you should be able to

- List the two devices in a DRAM cell and draw the circuit;

- List the three types of cell transistor that have been used in DRAM manufacturing;

- Name the two types of storage node (SN) capacitor used in DRAM chips;

- Explain why the planar capacitor was phased out in DRAM chips long ago;

- Explain how DRAM capacitor technology has evolved;

- List at least two benefits of buried word line (BWL) DRAM; and

- List at least two types of high aspect ratio (HAR) structures in a DRAM chip.

DRAM is widely used in smartphones, tablets, laptops, desktop computers, data servers, and all computational devices. One of the major driving forces of IC technology developments involves scaling down the DRAM feature size to increase storage and speed while reducing power consumption. DRAM is the first IC product that utilized 3D devices in HVM. A 3D capacitor was implemented in DRAM HVM long before 22-nm FinFET CMOS and 3D-NAND flash.

### 1.2.1 DRAM introduction

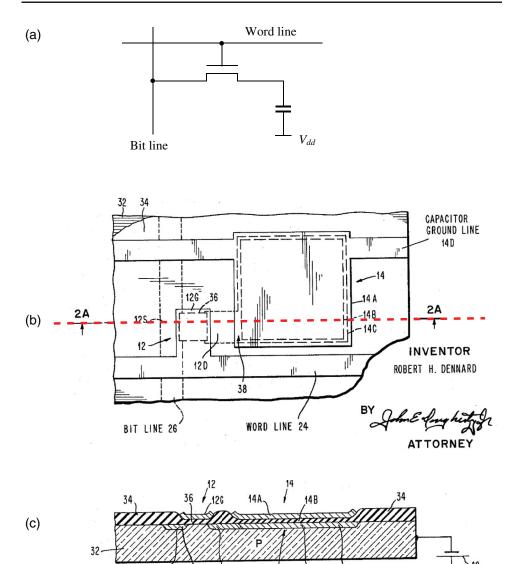

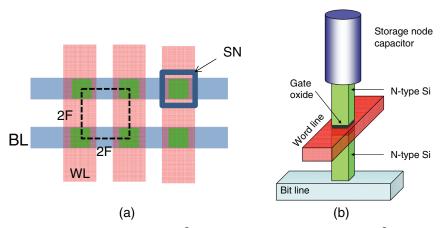

A DRAM cell has two devices: one n-channel MOSFET (NMOS) as an access transistor, and one capacitor for data storage, as shown in Fig. 1.3(a). DRAM was invented by Robert H. Dennard in 1967. Figure 1.3(b) portrays the DRAM layout, and Fig. 1.3(c) shows the cross-section in Dennard's patent.<sup>6</sup> For this DRAM, both the access transistor and SN capacitor are planar devices with silicon dioxide as the gate dielectric and capacitor dielectric.

For a DRAM cell, the capacitance C of the SN capacitor must be large enough to hold enough charge to maintain the memory. For a planar-cell transistor DRAM, C usually is about 35 femtofarads (fF). In order to scale down the feature size of the capacitor while keeping the C value unchanged, the DRAM developers initially reduced d to the reliability required leakage limit and used silicon nitride ( $k \sim 7$ ) to replace silicon dioxide (k = 3.9) for the capacitor dielectric. Due to the stress issue of nitride, the capacitor dielectric used oxide/nitride/oxide (ONO) for a long time.

### 1.2.2 3D devices in DRAM

An unchanged C and k made it very challenging to scale the feature size of a DRAM SN capacitor while maintaining its capacitance because the electrode surface area must be kept constant. The capacitor of the DRAM became the

**Figure 1.3** (a) DRAM circuit, (b) first DRAM layout, and (c) its cross-section. Figures (b) and (c) reprinted from IBM patent (1968, patentimages.storage.googleapis.com/pdfs/US3387286.pdf).

first IC device that became 3D after further scaling of the technology node, which helped reduce the footprint of the device.

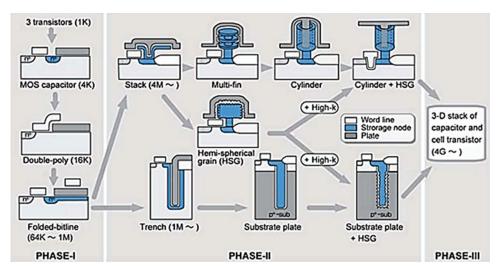

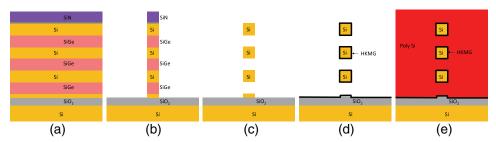

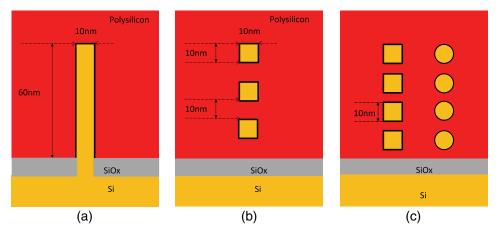

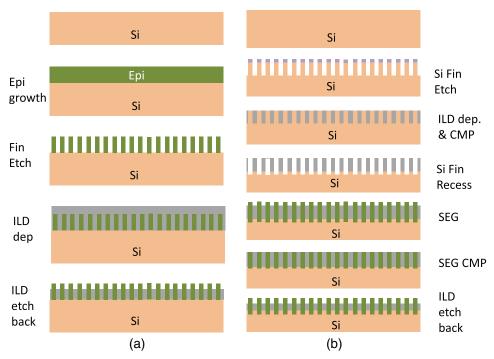

Figure 1.4 shows the evolution of the DRAM capacitor. Engineers and scientists demonstrated a lot of creativity to scale the geometry of the SN capacitor while keeping its capacitance unchanged. HSG in the figure stands for "hemispherical grain," which is polysilicon that features rough, hemispherical,

**Figure 1.4** Technology evolution of the DRAM capacitor. Image reprinted from Ref. A with permission from InTech.

and grainy surfaces. It had been widely used in DRAM manufacturing to increase the surface area of capacitor electrodes. When DRAM technology scales to PHASE-III, the CD of the cylinder becomes too small to grow HSG silicon; it has been replaced by a thinner metal-electrode (mostly TiN) layer.

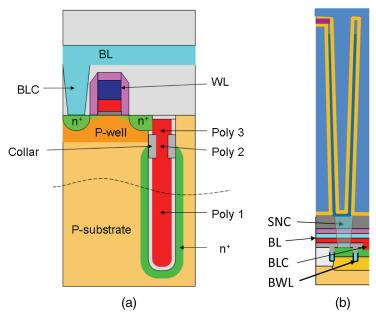

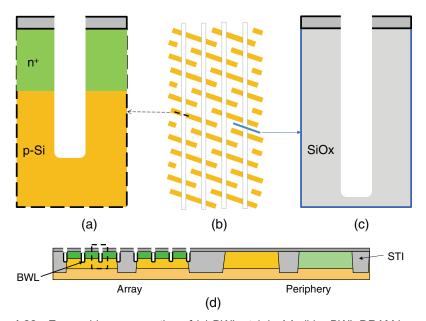

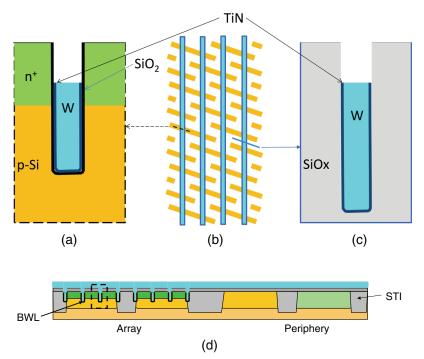

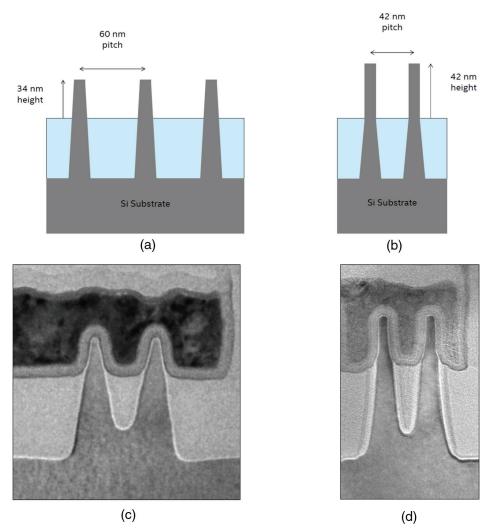

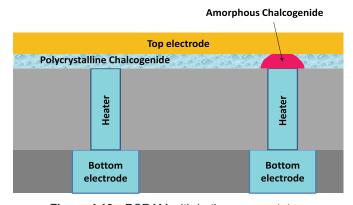

Figure 1.5 illustrates the advanced SN capacitors indicated in phase III of Fig. 1.4. Figure 1.5(a) shows a deep-trench capacitor DRAM; the dashed line indicates that a lot of substrate depth with the same structure has been omitted from the figure. The aspect ratio (trench depth versus trench CD) could be higher than 30:1. Currently, only a handful of silicon-on-insulator (SOI) IC chips use deep-trench capacitor DRAM as embedded DRAM, taking advantage of its compatibility in the back-end-of-line (BEoL) processes with normal CMOS processes and a lower capacitance requirement due to the SOI substrate. Most DRAM chips in the commodity market are DRAM with a cylindrical stacked capacitor, as shown in Fig. 1.5(b), which is described in detail in this chapter.

**Question:** For a cylindrical capacitor, how does the aspect ratio of a SN cylinder change when the DRAM feature size scales down by a factor of  $1/\sqrt{2}$  while C, k, and d remain unchanged?

**Answer:** In order to keep *C* unchanged in this scaling, the height of the cylinder must be increased to scale down its CD:

$$A_1 = \pi \times CD_1 \times h_1 = \pi \times CD_2 \times h_2 = A_2;$$

$CD_2 = CD_1/\sqrt{2}$ , and thus  $h_2 = \sqrt{2} \times h_1;$

$AR_2 = h_2/CD_2 = \sqrt{2} \times h_1/(CD_1/\sqrt{2}) = 2 \times h_1/CD_1 = 2 \times AR_1.$

If C, k, and d remain unchanged, then the aspect ratio of the SN cylinder will be **doubled** after scaling down the SN cylinder CD by a factor of  $1/\sqrt{2!}$

**Figure 1.5** (a) Deep-trench capacitor DRAM and (b) recessed cylinder-stacked capacitor DRAM.

Shrinking the footprint of the SN capacitor is the biggest challenge of DRAM scaling. Engineers and scientists are working to find new dielectric materials with higher k values and to reduce leakage of the off-state access NMOS to reduce the required capacitance C. When the feature size scales to the next generation, the scaling factor is no longer as aggressive as  $1/\sqrt{2}$ , which means that the increased aspect ratio of the SN cylinder is still manageable for each technology node.

When DRAM technology scaled toward the 80-nm node, short channel effects caused higher source/drain (S/D) leakage in the access transistor and shorter data-retention time. To overcome those issues, the DRAM access transistor transitioned from a planar structure to a 3D structure, and the recess gate (RG) transistor was introduced. Further development of the DRAM access transistor created the buried word-line (BWL) technology, which uses metal to form the gate electrode of the access transistor and the word line (WL), both of which are buried under the original silicon wafer surface. 8

Figure 1.6 illustrates the evolution of the DRAM access transistor, where L is the channel length. Figure 1.6(a) shows a planar MOSFET, and Fig. 1.6(b) illustrates a RG transistor; both use polysilicon as the gate electrodes. A comparison of Figs. 1.6(a) and 1.6(b) reveals that with the same gate critical dimension (CD), the RG transistor has a longer channel length than a planar transistor. Figure 1.6(c) shows a buried access NMOS with a titanium nitride (TiN) metal gate and a tungsten (W) WL buried underneath the silicon surface.

Figure 1.6 Evolution of the DRAM array cell NMOS: (a) planar, (b) RG, and (c) BWL.

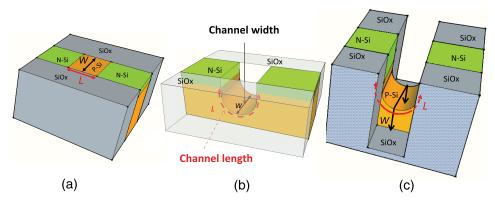

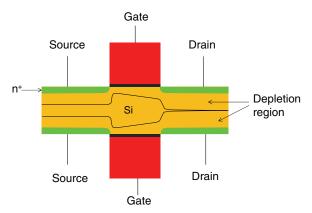

**Figure 1.7** 3D illustration of the channel width and channel length of DRAM cell transistors: (a) planar, (b) RG, and (c) BWL.

The channel length L and channel width W of the planar cell transistor, RG transistor, and BWL transistor are shown in Figs. 1.7(a)–(c), respectively. Note that L is the distance along the silicon surface between the source and drain, the heavily n-type-doped silicon (marked N-Si in the figure). At the same feature size, the RG transistor has the same channel width as the planar transistor, which is the CD of the AA; however, it has a much longer channel length. Furthermore, at the same geometry, the BWL transistor has the same L as the RG transistor, with a larger W, because there is more silicon surface exposed at the sides due to the deeper oxide etch in the BWL trench etch. The edge of the P-Si channel side and its curved top in real BWL devices is not that sharp—it is more like the shape of a saddle. Increasing the channel length can help to reduce leakage and maintain the retention time. Increasing the channel width can help to increase the drive current, and the BWL structure allows increasing the channel width without increasing the feature size of the device.

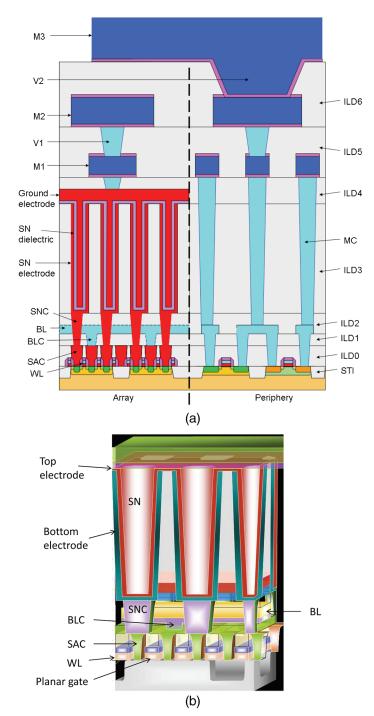

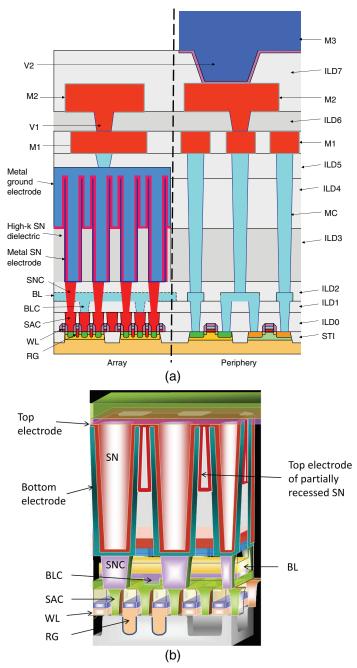

Figure 1.8 shows a DRAM with a planar cell NMOS and stacked cylinder capacitor. It represents the DRAM technology at  $\sim$ 110 nm or earlier technology nodes (described in detail in Chapter 14 of Xiao<sup>11</sup>), which used three layers of aluminum metal interconnection. The so-called aluminum metal layer in fact is a metal stack of Al-Cu ( $\sim$ 0.5% Cu) alloy bulk layers with a Ti/TiN barrier layer underneath and a TiN anti-reflective coating (ARC) on

**Figure 1.8** (a) Planar cell transistor DRAM and (b) 3D illustration of its memory cell structures. BL: bit line, BLC: bit-line contact, ILD: inter-layer dielectrics, MC: metal contact, Mx: metal x (where x = 1 to 3), SAC: self-aligned contact, SN: storage node, SNC: storage-node contact, and STI: shallow-trench isolation. (b) is modified from Ref. B.

**Figure 1.9** (a) Recessed-gate cell transistor DRAM, and (b) 3D illustration of its memory cell structures, which is modified from Ref B.

top. The W with the Ti/TiN barrier layer was used for the conducting plugs to connect the different layers.

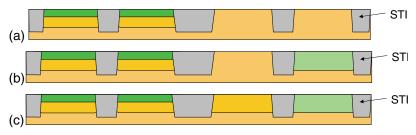

Figure 1.9(a) shows a DRAM with a RG transistor and partially recessed cylinder capacitor. These images represent DRAM technology after 90-nm

and before 3x-nm (i.e., 39-nm to 30-nm) technology nodes. Besides cell transistors and capacitors, another major development of this period was the introduction of copper metallization in 5x-nm DRAM. In comparison, logic CMOS IC chips used copper metallization in interconnects since the 180-nm technology node. There were two copper layers and one aluminum layer. The top aluminum-alloy layer allowed the use of Al-Cu bond pads for the standard gold wire bonding to keep the cost down. DRAM manufacturers are very cost-sensitive, and DRAM fabrication-process technologies are cost driven: two layers of copper can replace three layers of aluminum alloy, which reduces the overall cost.

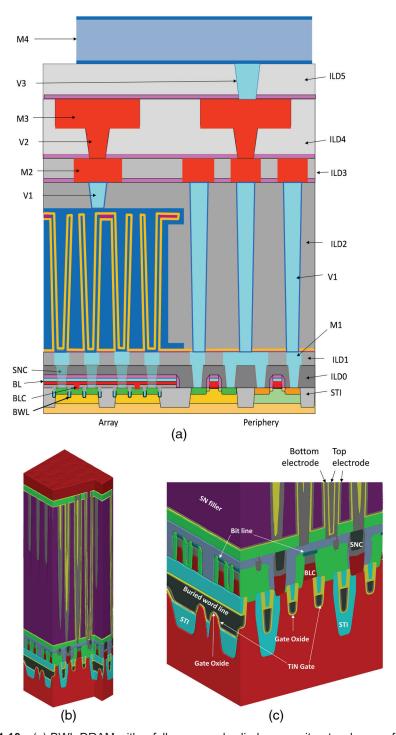

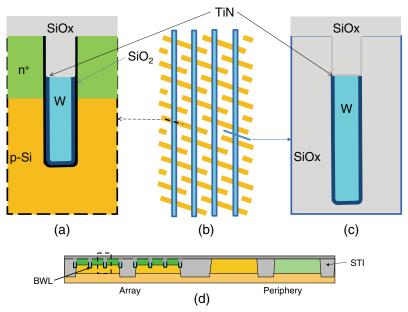

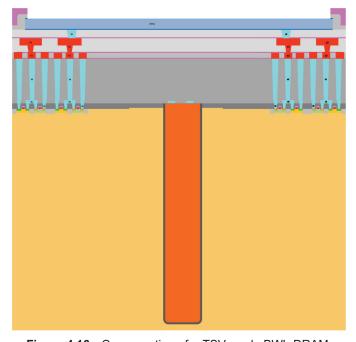

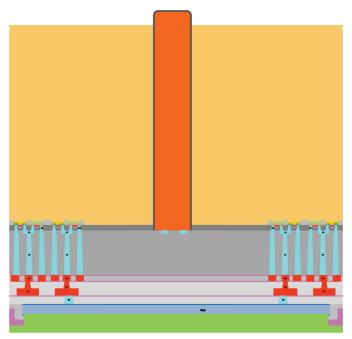

Figure 1.10(a) illustrates a BWL DRAM with a fully recessed cylinder capacitor, and Fig. 1.10(b) is the 3D illustration of its memory cell structures. Because the latter is based on the  $6F^2$  layout, it is quite different from Figs. 1.8(b) and 1.9(b), which are based on the  $8F^2$  layout (these layouts are discussed in Section 1.2.3). The BWL structure and  $6F^2$  layout have been widely used in 3x-nm and 2x-nm DRAM technology nodes. There are three metal interconnect layers: two copper layers and one aluminum-alloy layer.

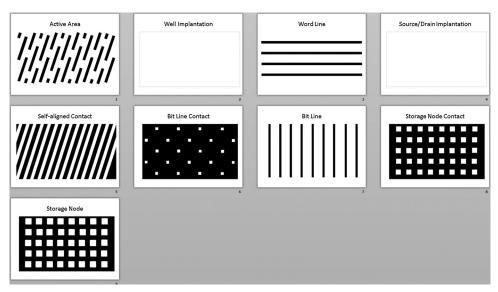

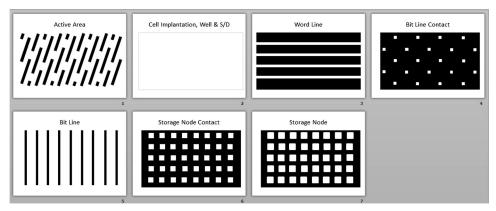

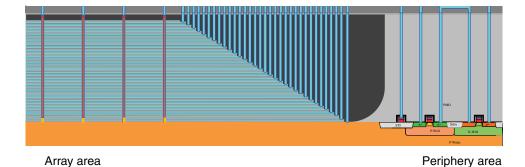

If DRAM can be made with these three types of cell transistors with the same single-patterning photolithography technology and the same capacitor materials and structure, then the planar-cell transistor DRAM requires nine masks, as shown in Fig. 1.11. The RG transistor DRAM adds a reversed WL mask for the silicon etch to form a RG cell transistor; thus, it needs ten masks in the array area, as illustrated in Fig. 1.12. The BWL DRAM uses one mask for both well implantation and S/D implantation, and one mask to form the RG and WL at the same time, while eliminating the SAC layer; thus, it only needs seven masks (Fig. 1.13). Fewer masks means lower cost, which is one of the most important reasons why BWL DRAM technology is used by all major DRAM manufacturers. Note that Figs. 1.11–1.13 only show the mask layers for the cell transistors and capacitors of the DRAM array area; they do not include the masks required to make CMOS devices in the peripheral areas.

Ion implantation masks in cell transistor formation and well implantation after active-area (AA) and S/D implantation after WL have a very large CD and require less strict control of the CD and overlay. In a DRAM chip, the feature sizes of peripheral circuits are much larger than the feature size of cell devices. The feature size of peripheral devices is usually two generations behind cell transistors. Advanced-technology nodes are processed separately to avoid loading effects caused by pattern-density and pattern-size variations on the processes such as photolithography, etch, CMP, etc. Although access transistors used 3D devices for multiple generations, peripheral devices still use planar MOSFET technology. Therefore, this book focuses on the manufacturing processes in 3D devices in array areas.

**Figure 1.10** (a) BWL DRAM with a fully recessed cylinder capacitor, two layers of copper, and one layer of aluminum interconnect, (b) 3D illustration of its memory cell structures, and (c) close-up of the memory cell. Both (b) and (c) are reprinted with permission from Coventor.

Figure 1.11 Masks for planar-access transistor DRAM in the array area.

Figure 1.12 Masks for RG transistor DRAM in the array area.

### 1.2.3 BWL DRAM manufacturing processes

This section discusses a generic manufacturing process of 2x-nm BWL DRAM technology. Although all DRAM manufacturers use BWL technology, each of them has a different design layout and different fabrication-process

Figure 1.13 Masks for BWL DRAM in the array area.

Figure 1.14 AA (a) mask 1 and (b) mask 2.

steps. Even for the same company, 3x-nm and 2x-nm BWL DRAM processes could be quite different.

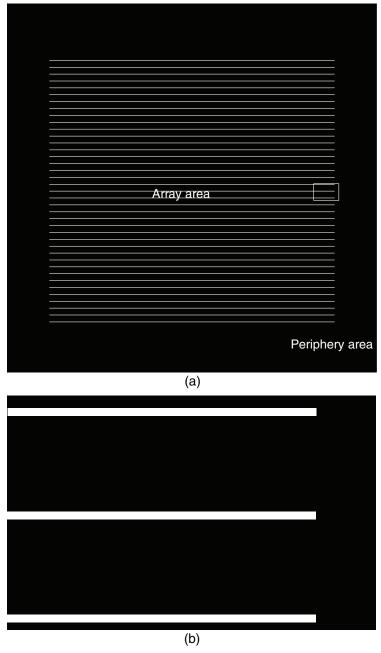

Just like CMOS IC chip manufacturing, BWL DRAM also starts with wafer cleaning. A pad oxide layer is then grown in a thermal furnace, and silicon nitride is deposited, usually with a low-pressure chemical vapor deposition (LPCVD) process. The SiN layer can be used as a hard mask for shallow-trench isolation (STI) etch. It is also used as a STI oxide CMP stop layer. Another hard mask layer is needed for a double-patterning process.

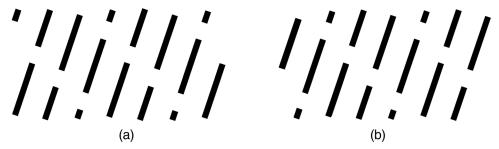

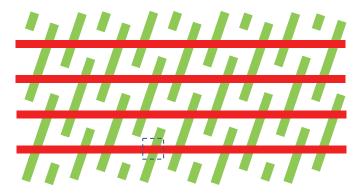

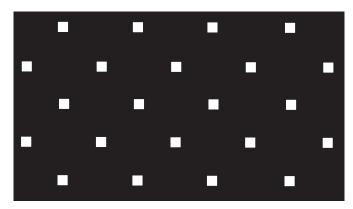

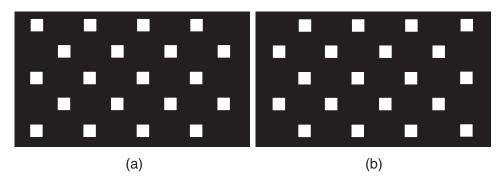

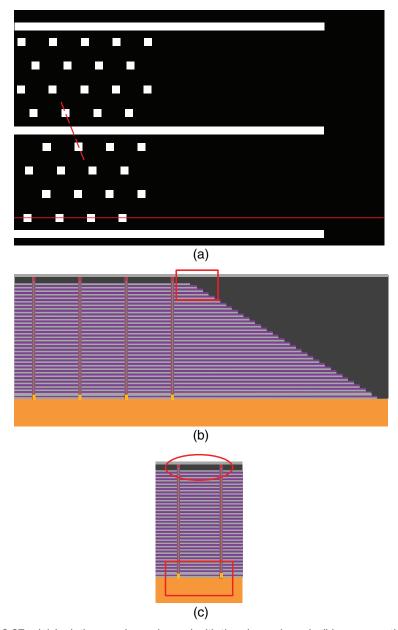

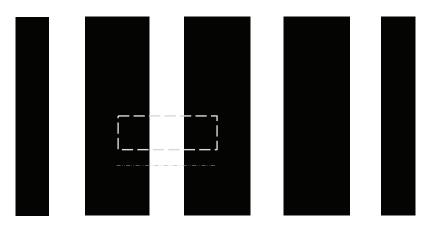

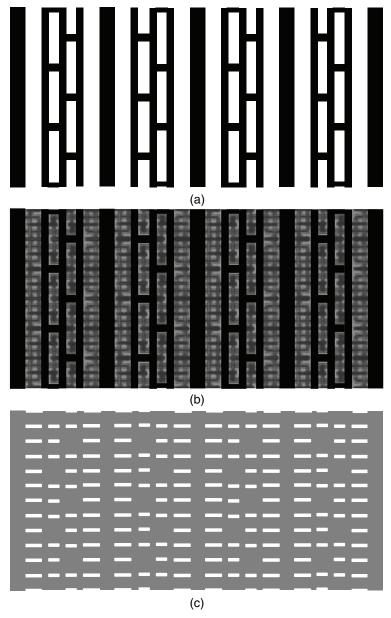

Double patterning is required for a 2x-nm DRAM, and the AA can be defined with two masks. Figure 1.14 shows the two masks of AA in a so-called "litho-etch-litho-etch" (LELE) double-patterning process. We only illustrate the masks in array area. Figure 1.15(a) illustrates the final AA pattern that is formed by combining AA mask 1 and AA mask 2. Overlay of the two masks becomes very critical. For example, the overlay shift in the *y* direction can affect the overlay budget of the contact layers later. The effects of the overlay shift in the *x* direction are shown in

**Figure 1.15** (a) The final AA pattern and (b) AA pattern with the AA2-to-AA1 overlay shifted in the *x* direction.

Fig. 1.15(b); they cause alternating wider and narrower STI gaps between AAs. The etch profile of narrower gaps is different from that of the wider gaps. The narrow gaps could have trouble performing void-free gap filling during oxide CVD. The gap aspect ratio and quality of the oxide-filled inside will affect the BWL trench etch process later.

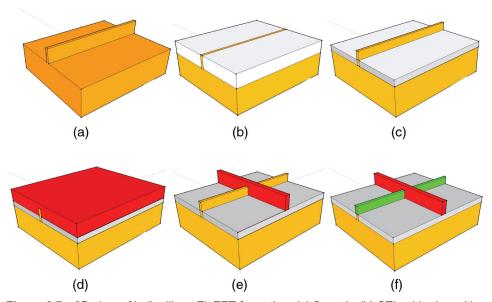

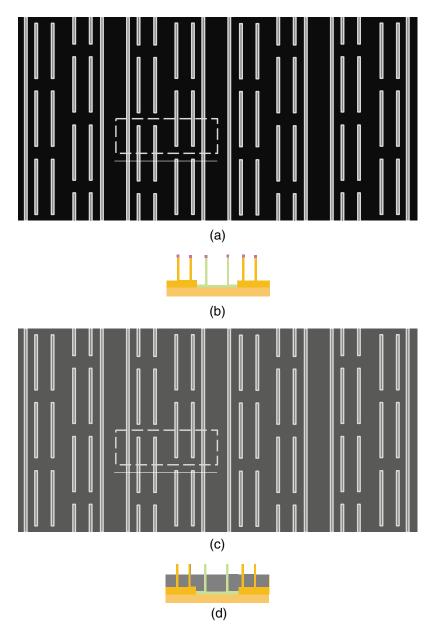

The AA pattern can also be formed with self-aligned double patterning (SADP), which uses spacers on the sidewalls of the mandrel, to double the pitch of the original patterning of the dummy layer. Figure 1.16(a) shows the mask of the mandrel pattern. Figure 1.16(b) illustrates the mandrel formed by etching the dummy layer with the Fig. 1.16(a) pattern. Figure 1.16(c) shows the mandrel with a sidewall spacer, and Fig. 1.16(d) illustrates the spacer pattern after the mandrel is removed, which doubles the pitch density of the mandrel pattern. The cut mask and the final AA pattern are illustrated in Figs. 1.16(e) and 1.16(f), respectively.

The AA SADP process starts with pad oxidation, a nitride hard mask, and dummy-mandrel film deposition. The mandrel patterns are formed after patterning and dummy film etch, as shown in Fig. 1.16(b). After photoresist (PR) strip and clean, a conformal film is deposited on the wafer surface, and a vertical etch back is performed to remove the film from the top of the dummy pattern and the bottom of the gap between the dummy patterns to form spacers on the sidewall of the mandrel, as shown in Fig. 1.16(c). After a highly selective etch process that removes the mandrel, the spacer pattern on top of the nitride hard mask, as shown in Fig. 1.16(d), can be used to etch the SiN hard mask. The cut mask illustrated in Fig. 1.16(e) can be used to cut the line-space hard mask pattern and form the final AA pattern on the SiN hard mask. This SiN hard mask can be used to etch the pad oxide and single-crystalline silicon substrate to form the final AA pattern.

In comparison with LELE double patterning, SADP requires significantly more process steps and thus has a higher cost. However, it has better CD control and less line-edge roughness. It also significantly reduces the requirement of a second mask overlaying the first mask and thus will not

**Figure 1.16** AA pattern formation with SADP: (a) mandrel pattern mask, (b) mandrel pattern, (c) spacers formed on mandrel pattern, (d) spacer pattern after dummy-pattern removal, (e) cut mask, and (f) the final AA pattern.

have the STI oxide void issue caused by the overlay error-induced gap narrowing displayed in Fig. 1.15(b).

The patterned SiN hard mask is then used to etch trenches into silicon to form STI. After STI etch, clean, metrology, inspection, and review, a thin layer of silicon dioxide is thermally grown on the silicon surface in an oxidation furnace, and an oxide layer is deposited to fill the high-aspect-ratio (HAR) trenches. Void-free trench fill is very critical at this step because any void between AAs will cause BWL trench etch-profile issues and kill the access transistor in the array. Chemical mechanical polish (CMP) of silicon oxide is performed, and the CMP process stops on the SiN hard mask layer. Hot-phosphoric-acid wet etch is commonly used to strip the SiN hard mask, and diluted hydrofluoric acid (HF) is commonly used to strip the pad oxide.

#### Table 1.1 AA module.

Wafer clean [Fig. 1.17(a)] PR strip and clean [Fig. 1.17(d)] Pad oxidation Etch pad oxide SiN hard mask deposition Etch silicon trench Amorphous silicon hard mask deposition [Fig. 1.17(b)] Wafer clean [Fig. 1.17(e)] AA mask 1 Oxidation Etch top hard mask STI oxide CVD to fill the trench [Fig. 1.17(f)] PR strip/clean [Fig. 1.17(c)] STI oxide CMP, stop on nitride [Fig. 1.17(g)] AA mask 2 Wet strip nitride and pad oxide Etch bottom hard mask Wafer clean [Fig. 1.17(h)]

Figure 1.17 The AA process module from (a) start to (b) finish.

The AA-formation process steps are summarized in Table 1.1. Figure 1.17 illustrates the AA module process steps with LELE double-patterning techniques. The cross-section of the beginning of the wafer process and the end of the AA module are illustrated in Figs. 1.17(a) and 1.17(h), respectively.

| $T_2$ | able | 12 | Well formation. |  |

|-------|------|----|-----------------|--|

|       |      |    |                 |  |

| Sacrificial oxide growth            | PR removal and clean [Fig. 1.18(b)] |  |  |

|-------------------------------------|-------------------------------------|--|--|

| Cell p-well mask                    | Peripheral p-well mask              |  |  |

| P-well implantation                 | P-well implantation                 |  |  |

| N + S/D implantation                | NMOS VT adjust implantation         |  |  |

| PR removal and clean [Fig. 1.18(a)] | Photoresist removal and clean       |  |  |

| Peripheral n-well mask              | Sacrificial oxide removal and clean |  |  |

| N-well implantation                 | Rapid thermal anneal [Fig. 1.18(c)] |  |  |

| PMOS VT adjust implantation         |                                     |  |  |

Figure 1.18 Cross-section view of well formation.

There are two mask steps in Table 1.1 because this AA process is a LELE double-patterning process. Here, a mask step indicates a photolithography process that includes multiple steps, such as pre-bake, primer coating, wafer cooling, PR coating, soft bake, wafer cooling, alignment and exposure, post-bake, wafer-edge exposure, wafer cooling, development, hard bake, wafer cooling, metrology, and inspection. If metrology and inspection find that the process is out of specification, then the wafer can be reworked by stripping PR/clean and then going through the entire mask procedure again.

After wafer clean, a thin layer of sacrificial oxide is grown, p-well masks are applied, and high-energy ion implantations are used to form the p-well for access NMOS in array areas and both p-well and n-well in the peripheral area. Well-implantation photolithography processes are not critical mask layers; they usually have large CDs, especially for access NMOS in the array area. After photoresist ashing and clean, the wafer is annealed. The process steps are listed in Table 1.2, and cross-section views of this stage are shown in Fig. 1.18.

Figure 1.18 shows the cross-section of the BWL DRAM well and channel ion-implantation processes. Figure 1.18(a) shows the cross-section illustration after ion implantations in the array area, which form both well junction and S/D junction of the access transistor of BWL DRAM. The well junctions are formed by high-energy p-type ion implantation. The access NMOS S/D junction is formed by high-current, low-energy n-type ion implantation. Figure 1.18(b) shows the cross-section view after n-well ion implantation in the peripheral area, and Fig. 1.18(c) illustrates the cross-section view after

Figure 1.19 Buried WL mask.

p-well ion implantation. All access transistors in the array area are NMOS; therefore, the array area only has p-well. There are both n-well and p-well in the peripheral area. Because peripheral transistors are planar transistors, their S/D implantations must wait until after gate formation.

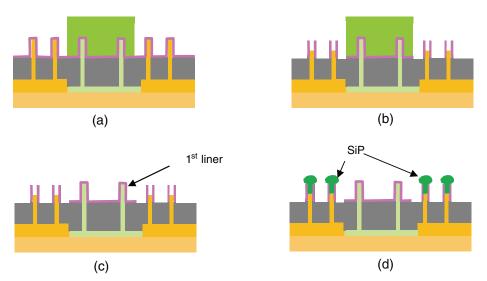

After well formation, the next step forms the access transistors. For a planar access transistor, the WL mask shown in image 3 of Fig. 1.11 is used to pattern PR, which is then used to etch a line-space pattern on a SiN hard mask, tungsten silicide, and polysilicon stack on the gate oxide. The RG transistor needs two masks, the first of which is a mask in the array area, i.e., a reversed WL mask similar to image 3 in Fig. 1.12, before the gate oxide growth and WL film stack deposition. It only etches silicon in the AA with little loss of silicon oxide in the STI area. After PR strip and wafer clean, gate oxidation, and gate/WL stack deposition, a second WL mask is used to etch line-space patterns of the gate and WL. The BWL cell transistor formation is the most unique process of this type of DRAM, compared to the other two types of access transistor formation of previous DRAM generations. The process requires the BWL mask shown in Fig. 1.19 to etch trenches on both single-crystal silicon and silicon oxide simultaneously. This etch process requires good control of the etch rate and etch-rate uniformity in both materials and good control of the silicon profiles inside trenches. The accesstransistor formation processes include

- BWL trench etch,

- clean,

- gate oxidation,

- TiN gate deposition,

- W CVD,

- W etch back,

- oxide CVD, and

- · oxide CMP.

Figure 1.20 overlaps the BWL mask with the AA pattern. Each AA has two word lines pass through it to form two cell transistors. The middle section

Figure 1.20 Overlap of BLW mask and AA patterns.

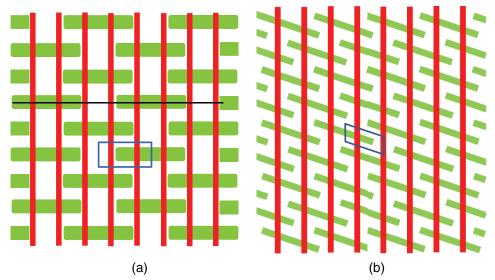

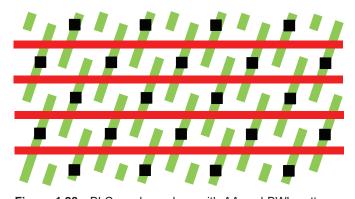

Figure 1.21 (a)  $8F^2$  DRAM layout and (b)  $6F^2$  DRAM layout.

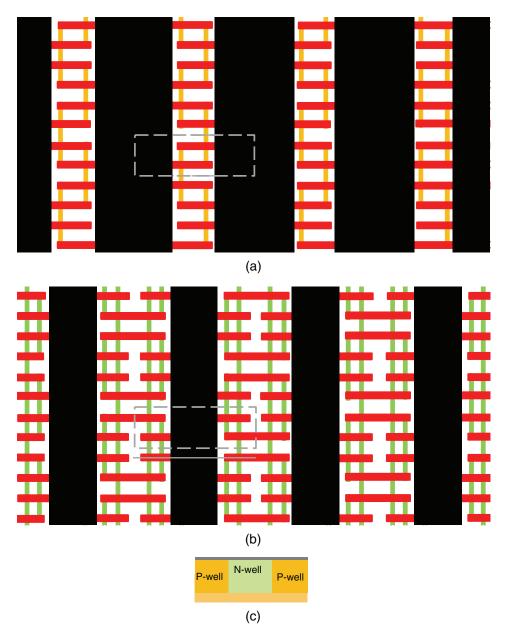

is the shared S/D, which will connect to the bit line (BL) and the sections at the two ends of the AA will connect to SN capacitors.

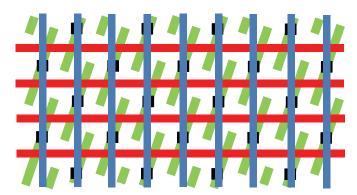

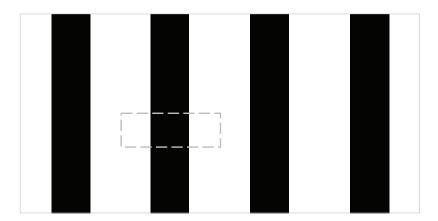

Figure 1.21(a) illustrates a DRAM layout that was widely used during planar transistor and RG transistor DRAM eras. It has unit array area of  $8F^2$ , shown as the rectangular box. Here, F is the half pitch of the densest cell pattern. Figure 1.21(b) is the same layout as Fig. 1.20 with a rotation of 90 deg. It is a DRAM layout with unit array area of  $6F^2$ , shown in the parallelogram box. This layout obviously has a higher cell density than the  $8F^2$  layout and thus has been more widely used in DRAM chip manufacturing in recent years. The cross-section of the BWL DRAM process in this section follows the dashed line in Fig. 1.21(a). Table 1.3 lists the process steps of the BWL module that forms access NMOS and WL in the array area.

| Table | e 1.3 | BW | L mod | lule. |

|-------|-------|----|-------|-------|

|-------|-------|----|-------|-------|

| Wafer clean                  | W and TiN etch back [Fig. 1.23] |

|------------------------------|---------------------------------|

| Oxidation                    | Wafer clean                     |

| Hard-mask deposition         | Oxide deposition                |

| BWL mask [Fig. 1.19]         | Oxide CMP                       |

| Etch hard mask               | Strip hard-mask                 |

| BWL trench etch              | Oxide deposition [Fig. 1.24]    |

| PR strip & clean [Fig. 1.22] | TiN gate electrode deposition   |

| Oxidation                    | W deposition                    |

|                              |                                 |

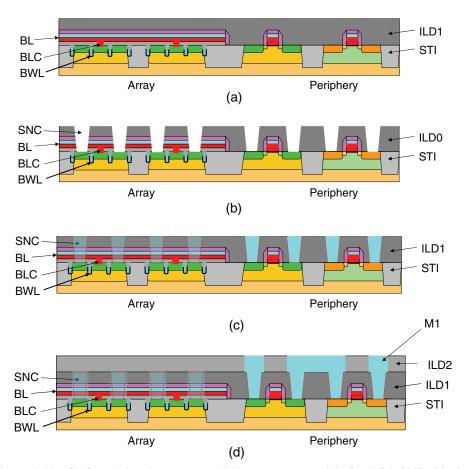

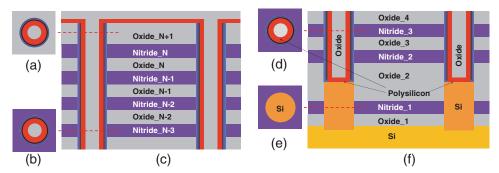

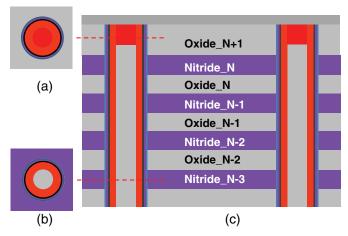

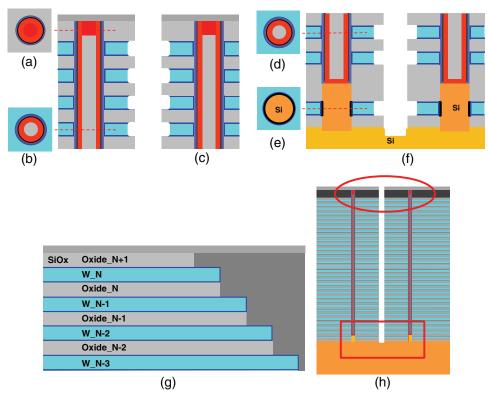

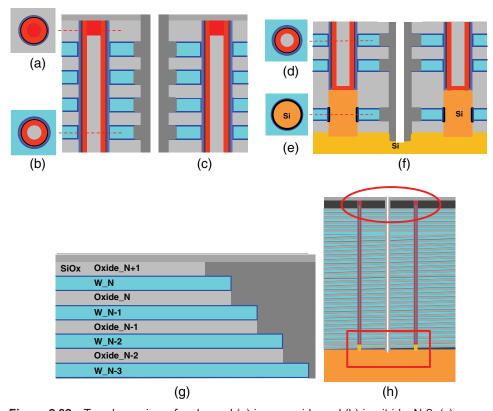

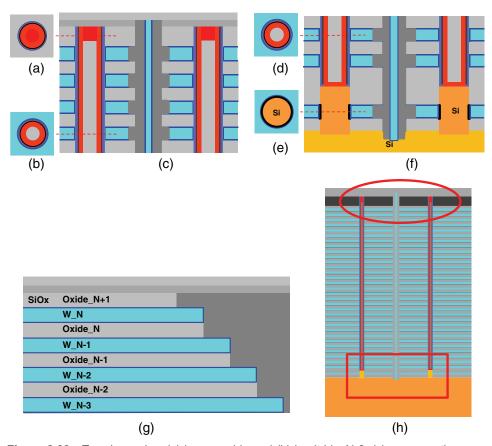

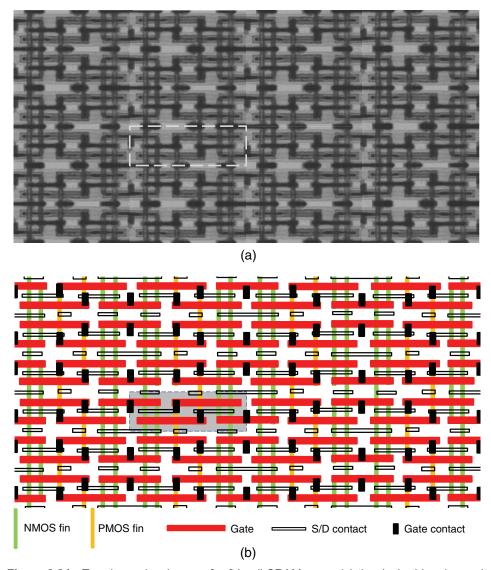

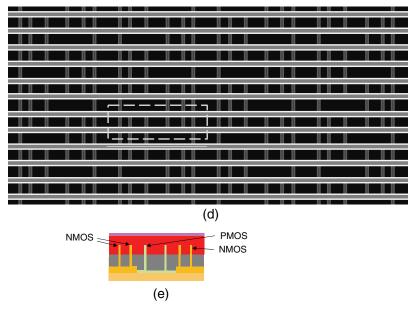

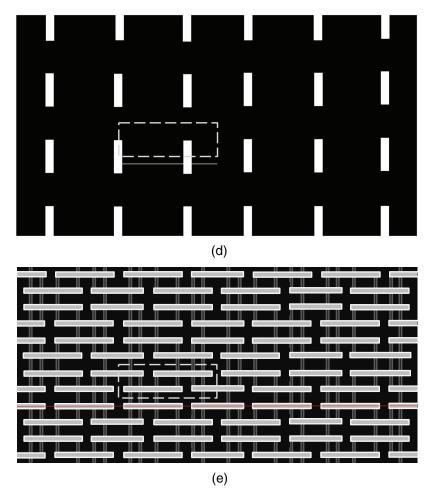

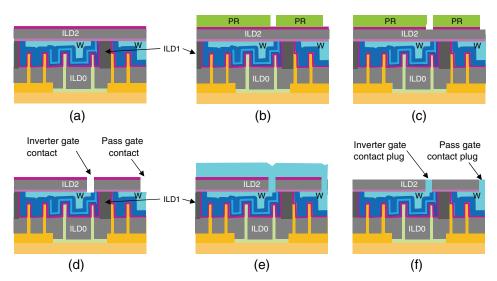

**Figure 1.22** Zoomed-in cross-section of (a) BWL etch in AA, (b) a BWL DRAM layout with BWL on top of AA layer, (c) zoomed-in BWL etch profile in STI oxide, and (d) illustration of cross-section of BWL DRAM after BWL trench etch.

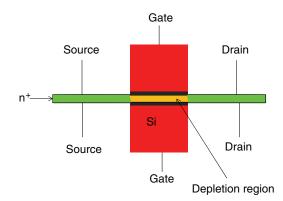

Figure 1.22(b) is a layout of BWL DRAM with BWL layer overlaps on top of the AA layer. Figure 1.22(a) is the zoomed-in detail of the dashed box in Fig. 1.22(d), which shows the BWL trench in AA silicon in the array area but not in the peripheral area. Figure 1.22(c) shows a close-up of the BWL trench-etch profile in STI silicon oxide. The etch rate in STI oxide is higher than the etch rate in AA silicon, which helps create silicon fins inside the BWL trenches, as shown in Fig. 1.7(c).

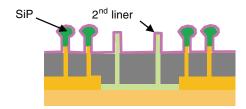

Figure 1.23(d) shows the cross-section of the BWL DRAM after TiN and W deposit into the BWL trenches, and an etch-back process removes W and TiN from the wafer surface, leaving W only inside the trenches from the WL.

**Figure 1.23** (a) Zoomed-in cross-section of a (a) BWL cell transistor, (b) BWL DRAM layout with BWL overlaps the AA, (c) zoomed-in BWL profile in the STI oxide, and (d) illustration of cross-section BWL DRAM after W and TiN etch back.

Figure 1.23(a) shows the detail of the cross-section of the cell transistor, indicated in the dashed box in Fig. 1.23(d). Figure 1.23(b) shows the BWL DRAM layout with a BWL layer on top of the AA layer. The dashed line indicates the cross-section line in the AA silicon, and the solid line indicates the cross-section line in the STI oxide, shown in Fig. 1.23(c).

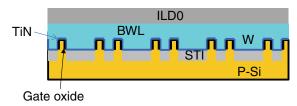

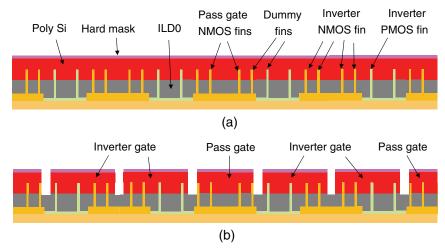

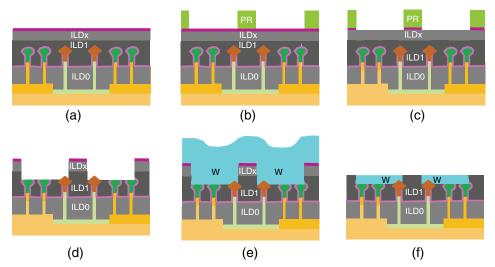

Figure 1.24(d) shows the cross-section of BWL DRAM after ILD0 deposition. Figure 1.24(a) is the zoomed-in access transistor shown in the dashed box of Fig. 1.24(d). The TiN forms the gate electrode of the DRAM access NMOS, and the W in the trenches forms the WL that is buried underneath the wafer surface.

Figure 1.25 shows the cross-section along the word line, illustrated in Fig. 1.24(b). By allowing a higher oxide etch rate in STI than the silicon etch rate in the AA during BWL trench etch, a device structure is created that the TiN gate wraps around the silicon channel with gate oxide in between along three sides, which forms a device similar to a tri-gate FinFET for the access transistor. This process can further reduce the off-state leakage current of the access transistor while increasing the drive current in its on-state.

**Figure 1.24** (a) Zoomed-in cross-section of cell transistor after ILD0, (b) a BWL DRAM layout with BWL on top of the AA, (c) zoomed-in cross-section in the STI oxide, and (d) illustration of cross-section BWL DRAM after W and TiN etch back.

Figure 1.25 Cross-section along the word line of BWL DRAM.

**Figure 1.26** (a) Cross-section along the word line of DRAM with a RG cell transistor and (b) DRAM with planar-cell-transistor DRAM.

Figure 1.26(a) is a cross-section along the WL of a DRAM with RG access transistor, and Fig. 1.26(b) shows the same kind of cross-section of a DRAM with a planar cell transistor. These two types of transistors have the same gate width at the same feature size, whereas the BWL cell transistor has

Figure 1.27 Bit-line contact mask.

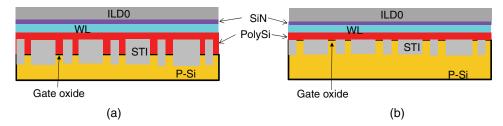

the longest gate width because of its tri-gate structure. The gate electrodes of planar and RG cell transistors are polysilicon, and the WL stacks comprise a SiN hard mask, tungsten silicide, and polysilicon.

After cell transistor formation, a non-critical mask with a large CD is used to remove oxide in the peripheral area. After wafer clean, thermal oxidation and remote plasma nitridation are performed to form gate dielectric (nitridized silicon oxide, or SiON) with an enhanced k value ( $\sim$ 5) for the peripheral CMOS devices. A heavily n-type-doped polysilicon is then deposited. A poly-dope mask that exposes the peripheral PMOS is applied. An extremely-high-dosage p-type ion implantation is performed to counter-dope peripheral PMOS polysilicon and convert it from heavily n-type to heavily p-type, which is needed for PMOS threshold-voltage control. After photoresist strip and clean, a mask is applied, and an etch process removes polysilicon in the array area. Photoresist removal and clean prepares the wafer for the bit-line contact (BLC) mask, shown in Fig. 1.27.

Figure 1.27 shows the BLC mask, which forms a contact between the BL and the S/D of the DRAM access NMOS. Figure 1.28 overlaps the BLC

Figure 1.28 BLC mask overlaps with AA and BWL patterns.

**Table 1.4** BLC module.

Wafer clean Array area mask Peripheral mask Etch polysilicon Etch oxide PR strip/clean [Fig. 1.29(c)] PR strip/clean [Fig. 1.29(a)] BLC mask [Fig. 1.27] Etch oxide Gate oxidation and nitridation Polysilicon deposition [Fig. 1.29(b)] PR strip clean [Fig. 1.29(d)] Wafer clean Polysilicon deposition TiN and W deposition PMOS poly-dope mask PMOS poly implantation SiN deposition [Fig. 1.29(e)] PR strip/clean

contact mask on the AA and BWL patterns. Note that BLC always connects the S/D in the middle section of the three sections of the AA pattern. The BLC mask has the lowest hole pattern density compared to other hole pattern masks in the DRAM array area. Because the oxide film covering the AA is very thin (usually < 30 nm) and contact hole aspect ratio is very low ( $\sim 1:2$ ), the BLC etch process is not as much a challenge as other HAR contact-hole etch processes.

There is an alternative method to pattern BLC in a BWL DRAM array area. After polysilicon deposition and poly-dope implantation, the BLC mask is applied on top of the polysilicon in the array area, and BLC holes are etched through the polysilicon and silicon oxide. After wafer clean and native oxide removal, TiN/W/SiN stack is deposited, and the stack is patterned into BL and peripheral gate patterns with a BL mask. <sup>10</sup> The BLC process steps are listed in Table 1.4.

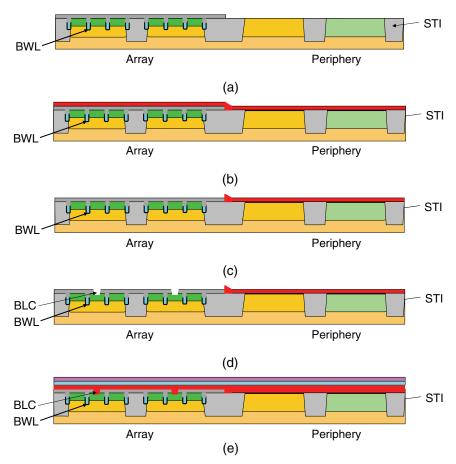

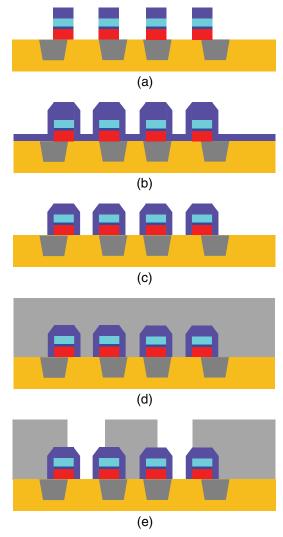

Figure 1.29 shows the BLC process module. Because the film stack that forms the BL in the array area is also used to form a gate stack in the peripheral CMOS, there are several process steps of film deposition and removal in the array area and peripheral area. Figure 1.29(a) shows the cross-section after peripheral oxide removal; Fig. 1.29(b) shows the cross-section after peripheral gate oxidation and polysilicon deposition; Fig. 1.29(c) shows the removal of polysilicon in the array area; Fig. 1.29(d) illustrates the cross-section of BWL DRAM after BLC etch, PR strip, and clean; and Fig. 1.29(e) shows the cross-section of the BLC holes that are filled with polysilicon and covered by TiN, W, and SiN.

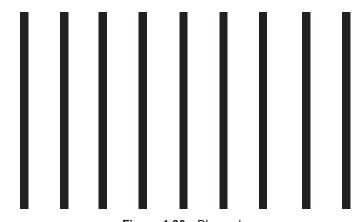

After BLC formation and BL film-stack deposition, the next process is the formation of the BL and peripheral transistors. Figure 1.30 shows the BL mask, and in Fig. 1.31 the BL mask is overlapped with BLC, BWL, and AA patterns. In this BWL DRAM layout, the BL is perpendicular to the WL, and it aligns with the BLC on the middle section of the AA between two WLs. In BWL DRAM, the BL in the array area and gate in the periphery share the same film stack. It usually consists of several layers, such as polysilicon, TiN, W, or tungsten silicide (WSi<sub>x</sub>) and SiN. Polysilicon is the gate electrode of the

**Figure 1.29** BLC processes: (a) remove oxide in the periphery, (b) grow gate oxide and deposit polysilicon, (c) remove polysilicon in the array area, (d) etch oxide and PR strip/clean, and (e) polysilicon, TiN, W, and SiN deposition.

Figure 1.30 BL mask.

Figure 1.31 BL mask overlaps with AA, BWL, and BLC patterns.

MOSFETs in the peripheral area that forms circuits such as address decoders, sense amplifiers, and multiplexers. TiN serves barrier layer and glue layer for W or  $WSi_x$ . Either W or  $WSi_x$  is the conducting layer used to reduce the resistance of the BLs and local interconnects of the peripheral circuits. The SiN layer is usually used as a HM layer for patterning the BL and gates of the peripheral transistors.

One of significant challenges of BL patterning is overlay. Because the W or WSi<sub>x</sub> layer is opaque to the light, it is very hard to optically measure the overlay between the PR BL pattern on the top hard mark above the W layer and the BLC pattern underneath W. After BL pattern etch, photoresist strip, and clean, the BL-to-BLC overlay can be measured by after-clean inspection (ACI). A re-oxidation process is usually used to repair etch-induced gate oxide damage and help to reduce gate leakage. There are then multiple masks in the peripheral area before the next mask in the array area. There are two masks for S/D extension (SDE) ion implantations of peripheral NMOS and PMOS. A conformal dielectric (usually SiN) CVD and a dielectric vertical etch back form spacers on the sidewall of the gates in the periphery and BLs in the array area.

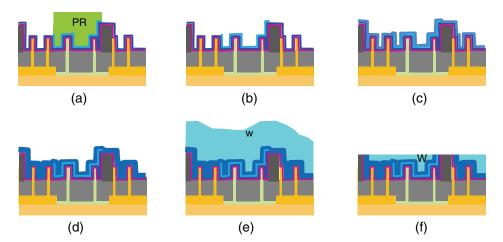

The sidewall spacers and the SiN on top of the BL stack help to prevent the storage node contact (SNC) plugs shorting to the BL. They have been widely used to form SNC similar to self-aligned contact (SAC) in earlier-generation DRAM devices. Figure 1.32 illustrates the process to form a spacer on a sidewall of the BL and how it helps to form the SAC. Figure 1.32(a) shows the BL stacks, and Fig. 1.32(b) illustrates the conformal dielectric film (usually LPCVD silicon nitride) deposition. Figure 1.32(c) shows the nitride etch-back process that forms the sidewall spacer. Figure 1.32(d) shows the ILD oxide deposition and CMP; and Fig. 1.32(e) demonstrates the contact etch that is self-aligned between the sidewall spacer due to the ILD etch process, which is highly selective to oxide and etches very little on nitride.

After spacer formation, another two masks are used for high-current ion implantation to form the heavily doped S/D of the peripheral NMOS and PMOS. The peripheral devices are formed after rapid thermal anneal (RTA)

Figure 1.32 (a)–(c) Sidewall spacer formation, and (d)–(e) self-aligned contact formation.

activates the dopants. Table 1.5 lists the process steps of the cell BL and peripheral transistor formations, and Fig. 1.33 illustrates some of the steps.

After the BL and peripheral devices are built, the next mask layer in the array area is the SNC, which creates the contact plugs between the storage capacitors and the AA. At first, ILD1 oxide is deposited. The ILD1 film needs to fill the gap between the BL without voids or buried keyholes. Otherwise, after SNC etch, the SNC holes could be connected by the keyholes underneath the ILD1, and after TiN/W CVD, SNC plugs can be shorted by the metal deposited in the keyholes. After ILD1 deposition and CMP, an etch stop layer is deposited, and the SNC mask illustrated in Fig. 1.34 is applied. For a 2x-nm

**Table 1.5** BL and peripheral transistor module.

Wafer clean PR strip/clean [Fig. 1.33(b)] BL mask [Fig. 1.30] Spacer dielectric film deposition BL and peripheral gate etch Spacer film etch back [Fig. 1.33(c)] Peripheral NMOS SD mask PR strip/clean/ACI [Fig. 1.33(a)] Peripheral NMOS SD implantation Re-oxidation Peripheral NMOS SDE mask PR strip/clean Peripheral NMOS SDE implantation Peripheral PMOS SD mask Peripheral PMOS SD implantation PR strip/clean Peripheral PMOS SDE mask PR strip/clean [Fig. 1.33(d)] Peripheral PMOS SDE implantation RTA

**Figure 1.33** Selected process steps of BL and peripheral transistor formation.

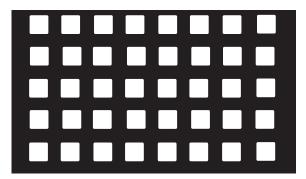

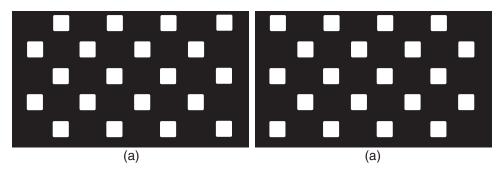

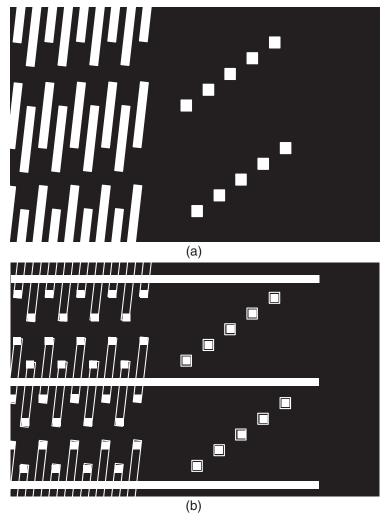

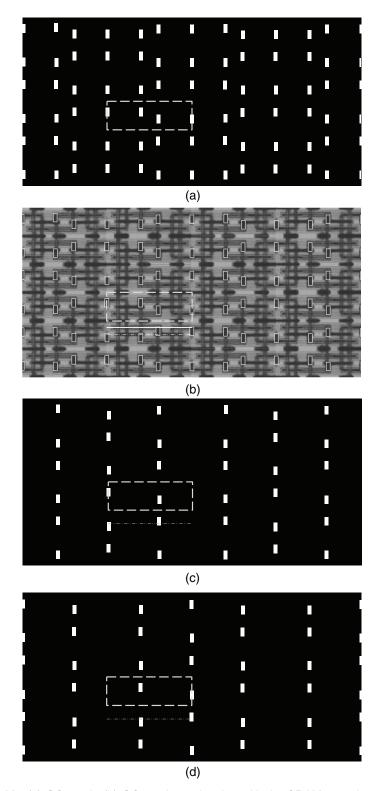

node, the pattern density is too high for single-photolithography patterning; two masks, each with a hole pitch relaxed by a factor of  $\sqrt{2}$  [as shown in Figs. 1.35(a) and 1.35(b)], are needed to perform LELE double patterning to form the SNC array.

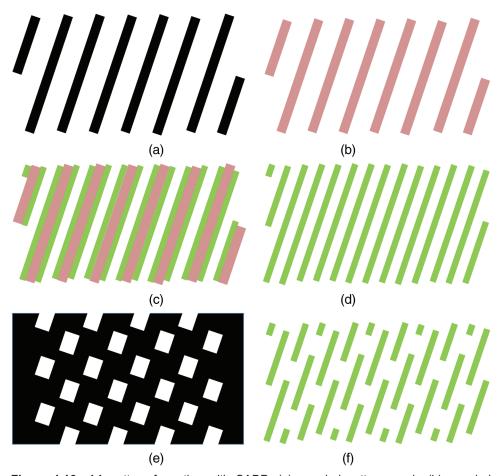

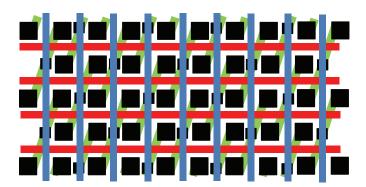

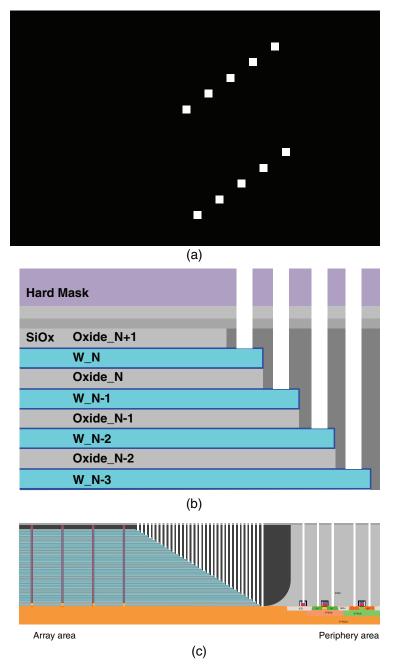

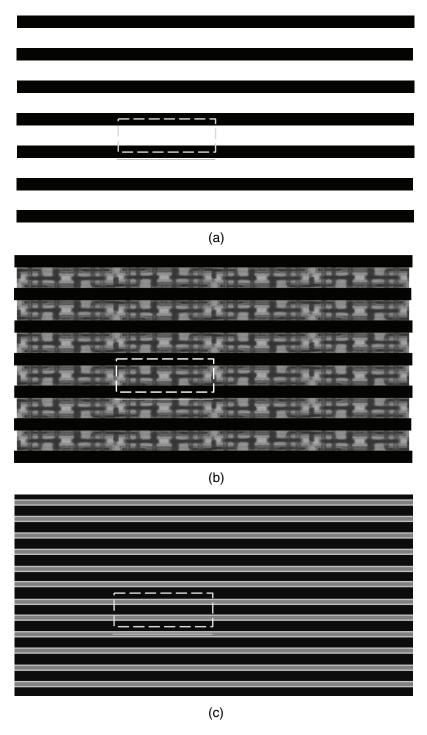

An alternative double-patterning technique that can form this kind of array hole pattern uses two masks, as shown in Fig. 1.36. In this case, two hard mask (HM) layers are needed. The first mask shown in Fig. 1.36(a) is used to pattern the top HM layer. The etch process forms the line-space pattern in the top HM layer that stops at the bottom HM, as shown in

Figure 1.34 SNC mask.

Figure 1.35 Two masks that relax the SNC pitch in Fig. 1.34.

Figure 1.36 Two masks that can be used to form the SNC pattern shown in Fig. 1.22.

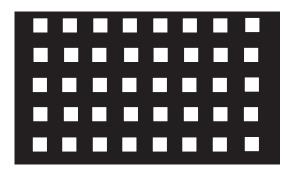

Fig. 1.37(a). After photoresist strip, clean, and another PR coating and baking, the second mask shown in Fig. 1.36(b) is applied. The second etch process is highly selective to primarily etch the bottom HM while etching very little of the top HM and the ILD1 layer; thus the bottom HM is only removed at the cross-points of the two masks to expose the ILD1 layer underneath, as shown in Fig. 1.37(b). The combined HM patterns can then be used to form the SNC hole pattern, illustrated in Fig. 1.37(c). Due to the corner-rounding effect, the final hole shape is more round than square, as shown in the

**Figure 1.37** (a) Patterning of the top HM layer with the mask shown in Fig. 1.24(a). (b) Patterning the bottom HM with the mask shown in Fig. 1.24(b). (c) The combined HM is used to etch the array hole pattern.

Figure 1.38 Overlapping the SNC mask with BL, BLC, BWL, and AA patterns.

Fig. 1.37(c). One of the advantages of the two-line-space mask for the SNC hole pattern is that for the first mask [Fig. 1.36(a)] only the y-direction overlay control is critical; for the second mask [Fig. 1.36(b)], only the x-direction overlay control is critical. In contrast, both of the masks shown in Fig. 1.35 need good overlay control in the x and y directions.

Figure 1.38 shows the overlapping of a SNC mask with BL, BLC, BWL, and AA patterns. The SNC holes go through the gaps between BLs and connect the two ends of the AA patterns. Dielectric spacers and cap layers on the BL allow the BLC hole to be etched in a self-aligned fashion. A thin, conformal SiN film is deposited (usually after BLC etch and clean), and an etch process removes the SiN film from the bottom of the SNC holes and wafer surface. This process is very similar to the sidewall-spacer-formation process, and the SiN film on the sidewall of the SNC hole can provide extra protection to prevent SNC contact plugs from shorting to the BL.

For some devices the same two masks can be used to form contact holes in the peripheral area. After Ti, TiN, and W deposition and CMP, the SNC module in the array area is finished. Another dielectric layer, ILD2, is deposited, and the metal 1 (M1) mask is needed to form the first

**Figure 1.39** SNC, peripheral contact, and M1 process steps: (a) after ILD2 CMP, (b) after ID2 etch and clean, (c) after SNC W/TiN/Ti CMP, and (d) after M1 W/TiN/Ti CMP.

**Table 1.6** SNC, peripheral contact, and M1 process steps.

|                           | -                                     |

|---------------------------|---------------------------------------|

| ILD1 deposition           | Wafer clean [Fig. 1.39(b)]            |

| LD1 CMP [Fig. 1.39(a)]    | Ti/TiN/W deposition                   |

| HM deposition             | W/TiN/Ti CMP [Fig. 1.39(c)]           |

| SNC mask 1 [Fig. 1.35(a)] | Etch stop layer deposition            |

| Etch HM                   | ILD2 deposition                       |

| PR strip/clean            | M1 mask                               |

| SNC mask 2 [Fig. 1.35(b)] | Etch ILD2                             |

| Etch HM                   | PR strip/clean                        |

| PR strip/clean            | Ti/TiN/W deposition                   |

| Etch ILD1                 | W/TiN/Ti CMP [Fig. 1.39(d)]           |

| Etch HM<br>PR strip/clean | PR strip/clean<br>Ti/TiN/W deposition |

metal-interconnect layer in the peripheral area. After etch, PR strip/clean, and Ti/TiN/W deposition and CMP, the wafer is ready for the next process module. Table 1.6 lists the process steps of SNC, peripheral contact, and M1, which are also illustrated in Fig. 1.39.

Figure 1.40 SN mask.

Figure 1.41 Two masks that relax the SN pitch in Fig. 1.40.

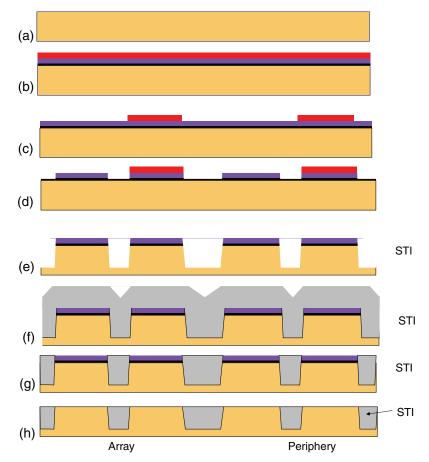

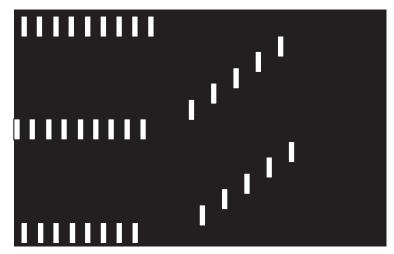

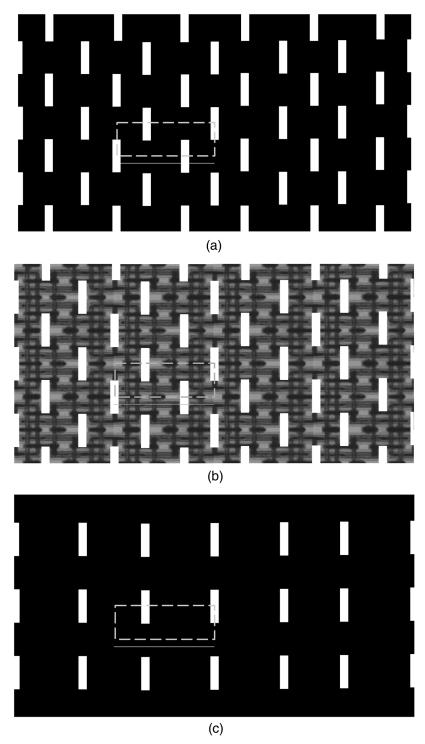

The next step deposits an etch stop layer (usually silicon nitride), a thick dielectric layer, ~1.5–2.0-µm silicon oxide, and a cap layer (SiN). A SN mask (Fig. 1.40), which is almost identical to the SNC mask in the array area, is applied. For the SNC layer, contact hole etch, metal deposition, and metal CMP are performed in both the array area and peripheral area. For the SN layer, all of the processes are performed only in the array area. Because of the high pattern density in a 2x-nm node, two masks are used to relax the resolution requirement and help pattern the dense SN holes, as illustrated in Fig. 1.41. The two-line-space pattern masks similar to that shown in Fig. 1.36 can also be used to form this SN pattern. In Fig. 1.42, the SN mask is overlapped with SNC, BL, BLC, BWL, and AA. The SN mask is aligned with the SNC mask to allow SN holes to land on the SNC plugs.

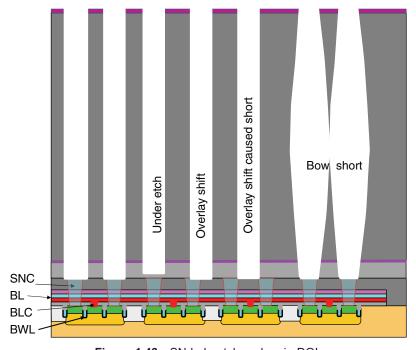

SN hole etch is one of the most challenging etch processes in IC manufacturing. The pattern density is high, the CD is small, the hole is very deep, and the aspect ratio is very high ( $\sim$ 50:1, possibly up to  $\sim$ 100:1). There are serval defects of interest (DOIs) in this etch process that could affect the product yield, such as

- under-etch,

- bottom residue,

- overlay shift that could cause high contact resistance or even a short between the neighboring SN capacitors via the SNC plugs, and

- a bow-shaped etch profile that can cause a short between the neighboring SN capacitors in the middle of the cylinders, as shown in Fig. 1.43. The SN-hole aspect ratio in the figure is  $\sim$ 10:1, but it is much higher in real devices.

After SN hole etch and clean, a thin TiN layer (~10 nm) is deposited, which serves as the electrode of the SN capacitor that connects to the array transistor. A photoresist layer is applied to the wafer surface to fill the SN

Figure 1.42 Overlapping SN mask with SNC, BL, BLC, BWL, and AA patterns.

Figure 1.43 SN hole etch and main DOI.

Figure 1.44 (a) SiN slot mask and (b) slot mask overlaps with previous layers.

holes, with spin coating and hard bake. A photoresist etch back is performed to expose the TiN on the top surface of the wafer. An etch process is used to remove the TiN on the wafer surface while TiN on the sidewall of the SN hole is protected by the photoresist. A mask [shown in Fig. 1.44(a)] that allows the removal of SiN from all peripheral areas and part of the array area, called slots, is applied. Figure 1.44(b) shows the SiN slot mask in array area overlapping with SN, SNC, BL, BLC, BWL, and AA layers. The top nitride layer is used to hold the tall TiN cylinders after removing the thick oxide that surrounds the TiN cylinders and prevents the cylinders from collapsing.

After SiN slot etch, hydrofluoric acid (HF) is used to remove the thick ILD silicon oxide to expose the TiN cylinder through the opening in the peripheral area and through the slots etched on the SiN in the array area. The SiN cap layer functions like the plastic ring holder of a six-pack of cans, preventing the TiN from falling down. Without the top nitride layer, the tall TiN cylinders are likely to collapse and short to each other, especially with the surface tension of liquids used in wet etch and clean. After wafer cleaning of conformal, high-k dielectric layers, such as zirconium oxide (ZrO), an aluminum oxide (AlO) stack with a total thickness <10 nm is deposited on both the inside and outside wall of the TiN cylinder. Another thin TiN layer, which is the electrode that connects to the ground (<10 nm), is deposited with full coverage of both the inside and outside of the cylinder to form the SN capacitor. Without an ILD oxide recess, the capacitor can only form inside the SN hole with electrode area  $\sim \pi \times CD \times h$ . Here, CD is the SN hole CD, and h is the SN hole depth. By recessing the ILD oxide and exposing the outside of the TiN cylinder, the area of the SN capacitor is doubled, which allows scaling down the SN cylinder CD by a factor of 2 without increasing the depth of the SN hole. After conformal deposition of the ground electrode (usually TiN), a conducting layer with good gap-fill capability (in many cases, SiGe) is deposited to fill the remaining SN holes and the gaps between

Table 1.7 SN module.

| Wafer clean                      | TiN deposition                                      |

|----------------------------------|-----------------------------------------------------|

| Each stop layer (ESL) deposition | PR coating                                          |

| ILD deposition                   | RP etch back                                        |

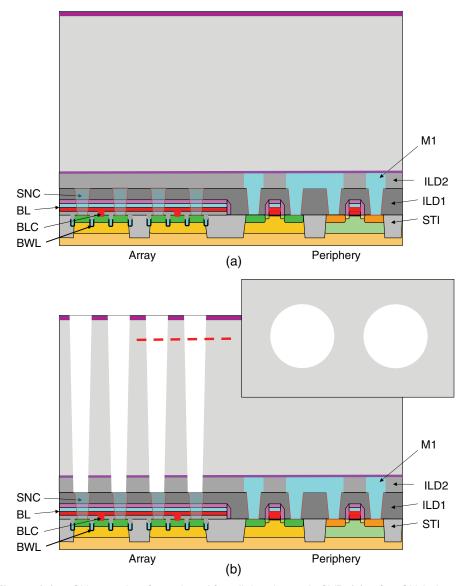

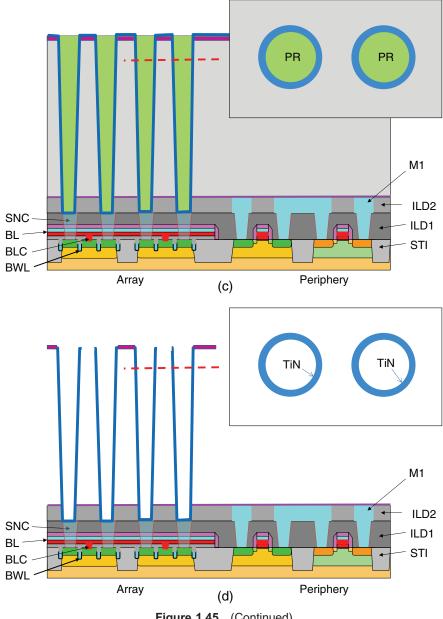

| SiN deposition [Fig. 1.45(a)]    | TiN etch [Fig. 1.45(c)]                             |

| SN mask 1 [Fig. 1.41(a)]         | SiN slot mask [Fig. 1.44(a)]                        |

| Etch nitride                     | Nitride etch                                        |

| PR strip/clean                   | PR strip/clean                                      |

| SN mask 2 [Fig. 1.41(b)]         | ILD removal [Fig. 1.45(d)]                          |

| Etch nitride                     | Wafer clean                                         |

| PR strip/clean                   | High-k film deposition                              |

| Etch oxide [Fig. 1.45(b)]        | TiN and conducting filler deposition [Fig. 1.45(e)] |

cylinders, which finishes the SN module. Table 1.7 lists the process steps of the recessed-stack cylinder capacitor.

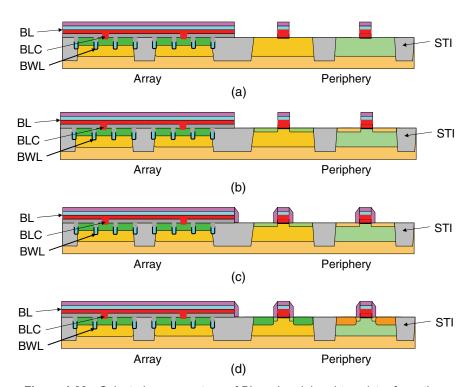

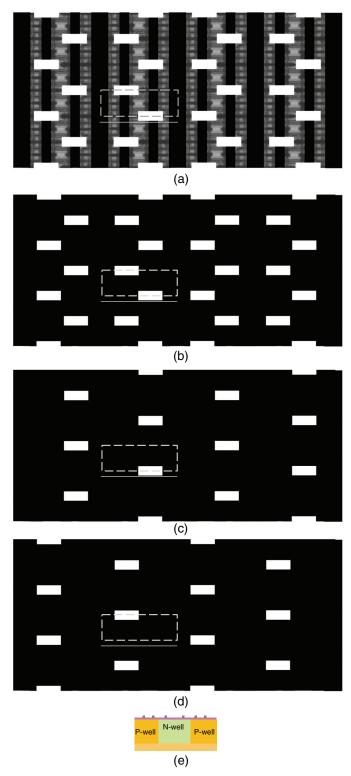

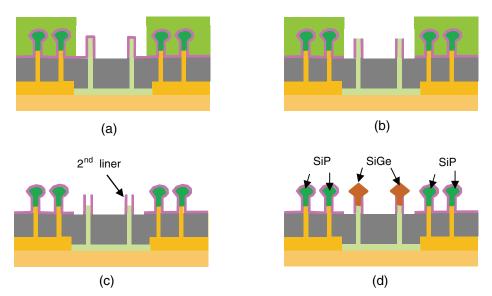

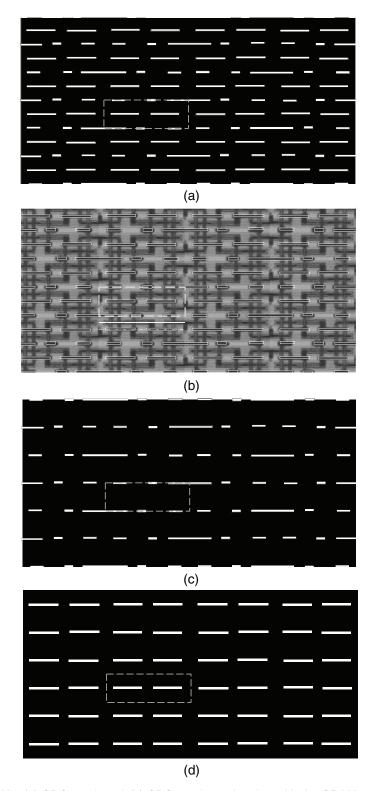

Figure 1.45(a) shows the cross-section of the BWL DRAM after SN dielectric-layer (etch stop nitride, thick oxide, and nitride cap layer) deposition. Figure 1.45(b) shows the cross-section after SN hole etch, PR strip, and clean. The insert shows the top-down cross-section view of two SN holes in oxide. Figure 1.45(c) illustrates the cross-section after the top TiN is removed. The PR in the SN holes protects the TiN film on the sidewall. The inserted graph shows the hole filled with PR that protects TiN. Figure 1.45(d) shows the cross-section after the thick ILD oxide is removed; the HAR TiN cylinders stands on SNC plugs, holding on the SiN cap layer at the top and the ESL/ILD2 layers at the bottom. The insert shows the TiN cylinders stand on the wafer surface, empty both inside and outside. Some DRAM manufacturers use two top SiN layers—one on the surface and another one ~150 nm below the surface—to hold the thin and tall TiN cylinders. Figure 1.45(e) shows the cross-section after deposition of a high-k dielectric layer, TiN, and a conducting filler. The commonly used DRAM SN high-k dielectric is a zirconium oxide-aluminum oxide-zirconium oxide (ZrO<sub>2</sub>/ Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, or ZAZ) stack deposited by atomic-layer-deposition (ALD) processes. The TiN is used as the ground electrode of the SN capacitor, and a SiGe alloy is commonly used to fill the remaining SN holes and gaps between the SN cylinders.

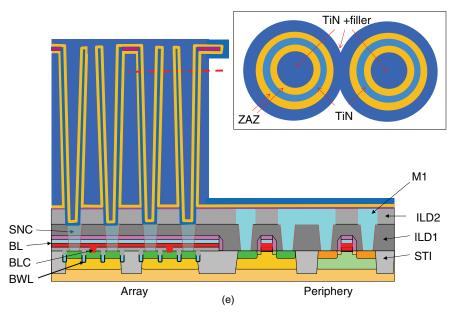

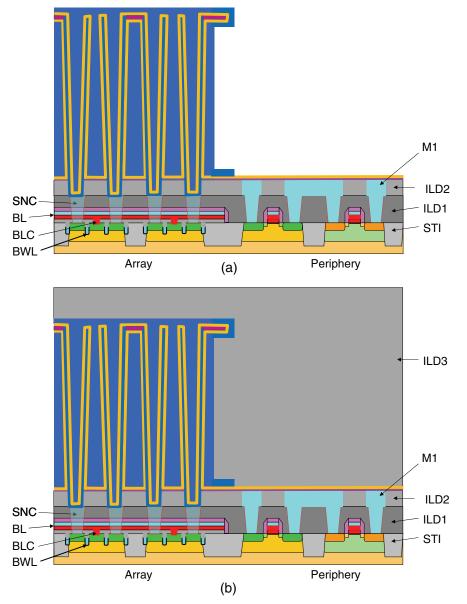

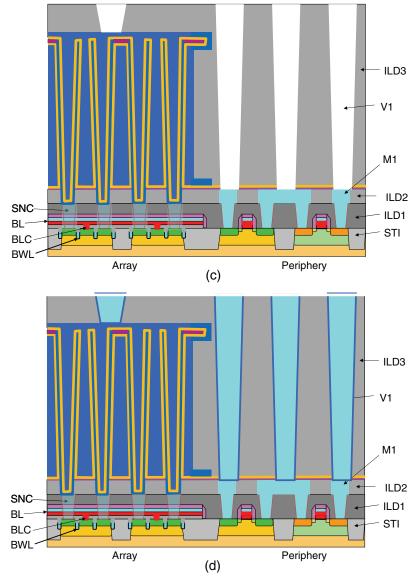

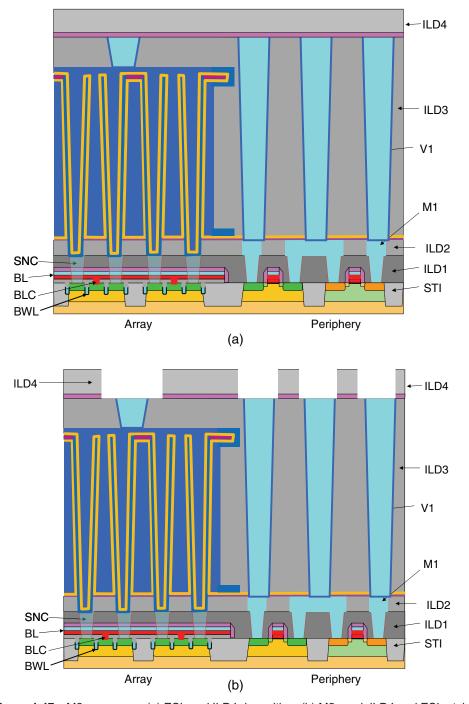

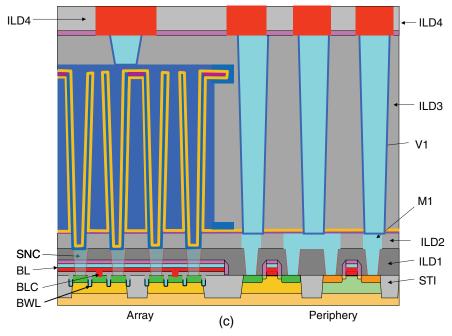

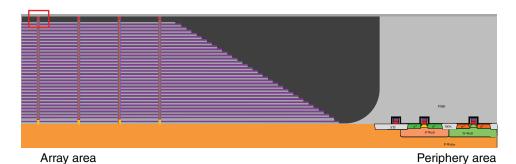

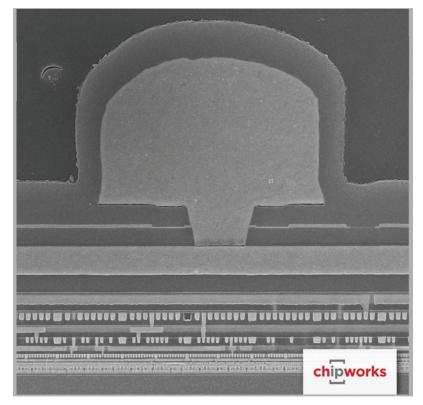

Thus ends the front-end-of-line (FEoL) processes of the advanced BWL DRAM manufacturing process. Back-end-of-line processes occur primarily in the peripheral area, starting with a mask layer that protects the array area and etches away the metal layers in peripheral areas [Fig. 1.46(a)]. After PR strip and clean, a thick ILD3 (usually silicon oxide) is deposited, and oxide CMP planarizes the ILD3, as shown in Fig. 1.46(b). The via 1 (V1) mask is used to etch via holes through the thick oxide layer to land on M1. Although these via holes are very deep (2–3  $\mu$ m)—even deeper than SN holes—their CDs are usually larger than the CD of the SN hole, and their pitches are also much

**Figure 1.45** SN capacitor formation. After dielectric stack CVD (a); after SN hole etch, insert is top-down view of SN holes (b); after surface TiN removal (c); after ILD oxide wet etch (d); and after high-k dielectric and ground electrode deposition.

larger than that of the SN hole. V1 hole patterning has significantly relaxed control of the CD, overlay, and etch profile than that of SN hole patterning. After V1 etch and PR strip/clean, as shown in Fig. 1.46(c), Ti/TiN/W are deposited into the V1 holes, and a CMP process removes W/TiN/Ti from the wafer surface, leaving the conducting plug inside the ILD3, as shown in Fig. 1.46(d).

Figure 1.45 (Continued)

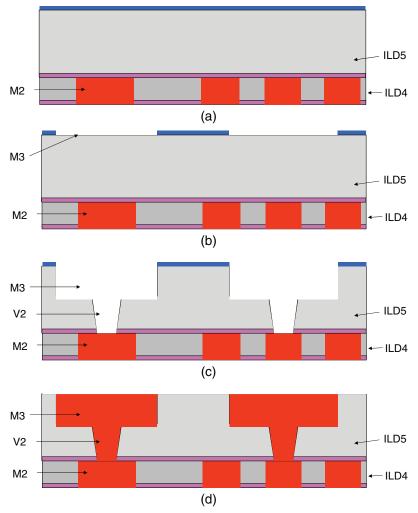

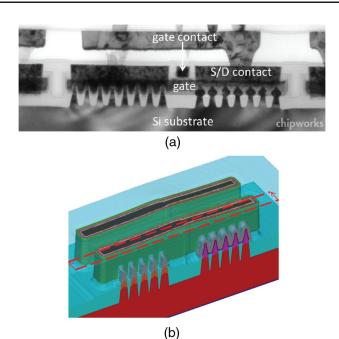

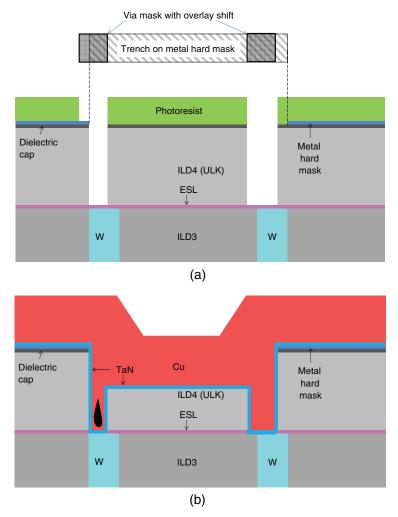

V1 formation is followed by metal 2 (M2), a single damascene copper (Cu) metallization process. M2 process steps include stop-layer etch and ILD4 oxide deposition [as shown in Fig. 1.47(a)], M2 mask, M2 etch [as shown in Fig. 1.47(b)], barrier and copper-seed layer deposition, copper electrochemical plating, copper anneal, and copper CMP (CuCMP) [as shown in

Figure 1.45 (Continued)

Fig. 1.47(c)]. For copper metallization, tantalum (Ta) or tantalum nitride (TaN) is commonly used for the barrier layer, and the seed layer is copper. Both layers are usually deposited by a physical-vapor-deposition (PVD) process. Bulk Cu plating usually uses an electrochemical process, with a wafer as the cathode and a pure-Cu plate as the anode. Copper ions from the sulfate (CuSO<sub>4</sub>) in sulfuric acid will deposit on the wafer surface that is negatively biased. Additives such as an accelerator, suppressor, and leveler are added to the plating solution to accelerate Cu plating at the bottom of the hole or trench, suppress the corner deposition, and make the Cu surface flat, respectively. Table 1.8 lists the process steps of V1-M2.

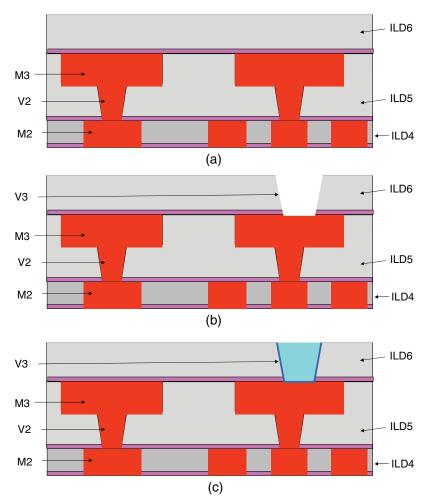

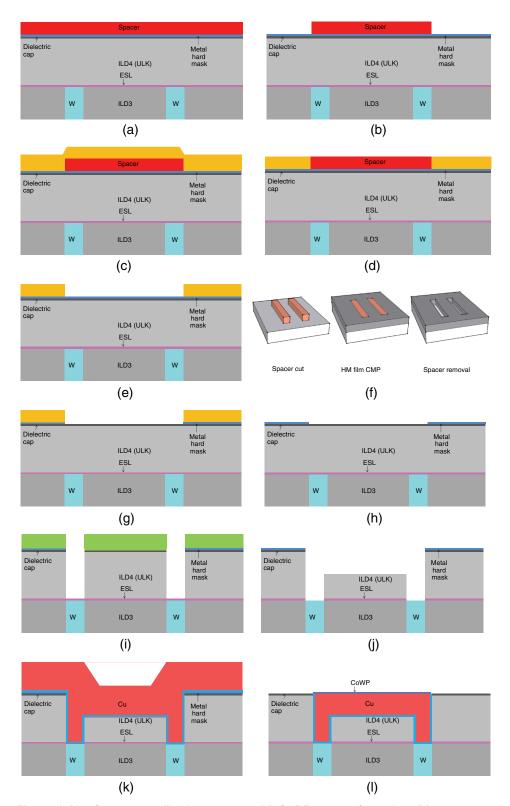

After M2 CuCMP, a dual-damascene Cu metallization process is used to form V2 and M3. It starts with ESL, ILD5, dielectric cap, and metal HM deposition; a M3 mask is used to etch the TiN HM. After PR strip/clean, a V2 mask is used to etch dielectric layers and form the V2 holes and stop in ESL. After PR strip/clean, dielectric etch forms the M3 trench and allows the V2 to break though the ESL. Another clean process follows, and then the metal barrier and seed layer are deposited, and finally the bulk copper is plated, annealed, and polished. The Ta or TaN barrier and TiN HM mask are also removed during CuCMP. After wafer clean, a cap layer deposition finishes the V2-M3 module, as shown in Fig. 1.48; the process steps are listed in Table 1.9.

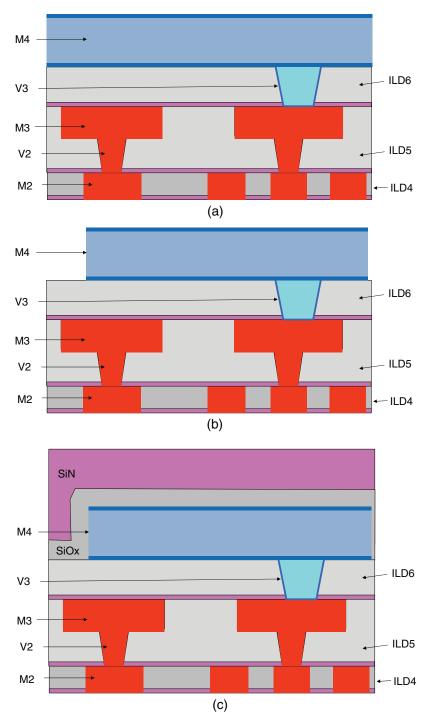

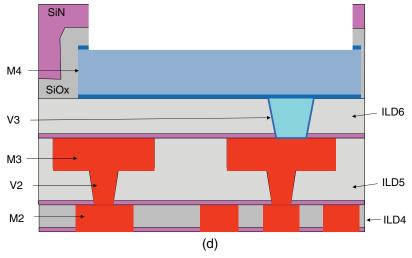

The V3 process starts with ESL and ILD6 deposition, as shown in Fig. 1.49(a); after the V3 mask is used to etch via holes, the PR is stripped and

**Figure 1.46** V1 process steps (a) after peripheral metal etch and clean, (b) after ILD3 CMP, (c) after V1 etch and PR strip/clean, and (d) after V1 WCMP.

wafer cleaned, as illustrated in Fig. 1.49(b). Then the Ti/TiN/W stack is deposited and the CMP process removes all metal layers on the wafer surface for W plugs that contact M4 to M3 (Fig. 1.49).

The last interconnect layer of this BWL DRAM manufacturing process is the metal 4 (M4) layer. It starts with metal stack PVD, which deposits Ti/Al-Cu/TiN, as shown in Figure 1.50(a). Here Ti is used to reduce contact

Figure 1.46 (Continued)

resistance between metal stack and W plugs. Al-Cu is an aluminum alloy with  $\sim 0.5\%$  copper to increase resistance of electromigration and improve chip reliability. The top TiN is used as an ARC to reduce the standing wave effect during M4 patterning. The M4 mask is used to pattern and etch the M4 metal stack, which forms the last layer of interconnects and bond pads. After PR strip and clean [Fig. 1.50(b)], the passivation dielectric layers (usually silicon oxide and then silicon nitride) are deposited, as shown in

**Figure 1.47** M2 processes: (a) ESL and ILD4 deposition, (b) M2 mask ILD4 and ESL etch, and (c) M2 CuCMP.

Figure 1.47 (Continued)

#### Table 1.8 V1 and M2 process steps.

| Peripheral area mask                       | W/TiN/Ti CMP [Fig. 1.46(d)]       |

|--------------------------------------------|-----------------------------------|

| Etch SiGe/TiN/ZAZ                          | ESL deposition                    |

| Photoresist strip and clean [Fig. 1.46(a)] | ILD4 deposition [Fig. 1.47(a)]    |

| ILD3 deposition                            | M2 mask                           |

| ILD3 CMP [Fig. 1.46(b)]                    | M2 etch                           |

| V1 mask                                    | PR strip/clean [Fig. 1.47(b)]     |

| V1 etch [Fig. 1.46(c)]                     | Barrier and seed-layer deposition |

| PR strip and clean                         | Bulk copper plating               |

| Ti/TiN deposition                          | Cu anneal                         |

| W deposition                               | CuCMP [Fig. 1.47(c)]              |

|                                            |                                   |

**Table 1.9** V2 and M3 process steps.

| ESL, ILD5, and dielectric cap deposition | ILD 5 etch                        |

|------------------------------------------|-----------------------------------|

| Metal HM deposition [Fig. 1.48(a)]       | ESL removal [Fig. 1.48(c)]        |

| M3 mask                                  | Clean                             |

| HM etch [Fig. 1.48(b)]                   | Barrier and seed-layer deposition |

| PR strip and clean                       | Bulk copper plating               |

| V2 mask                                  | Cu anneal                         |

| Dielectric cap and ILD5 etch             | CuCMP [Fig. 1.48(d)]              |

| PR strip and clean                       |                                   |

**Figure 1.48** V2-M3 processes: (a) ESL, ILD4, and metal HM deposition, (b) M3 mask HM etch, (c) V2 ILD and ESL etch, and (d) M3 CuCMP.

Fig. 1.50(c); the last mask, a bond pad mask, is used to pattern and etch the passivation dielectric stack to expose the bond pads for test probing and wire bonding. After PR strip and clean, as shown in Fig. 1.50(d), the wafer is ready for the wafer-acceptance test (WAT). The wafer can be shipped for packaging if it passes the WAT. The process steps of V3-M4 and passivation are listed in Table 1.10.

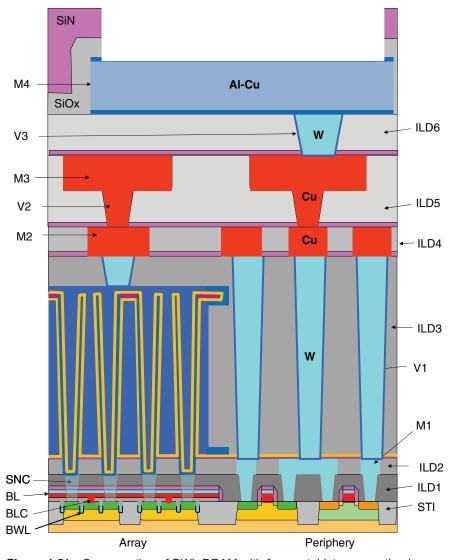

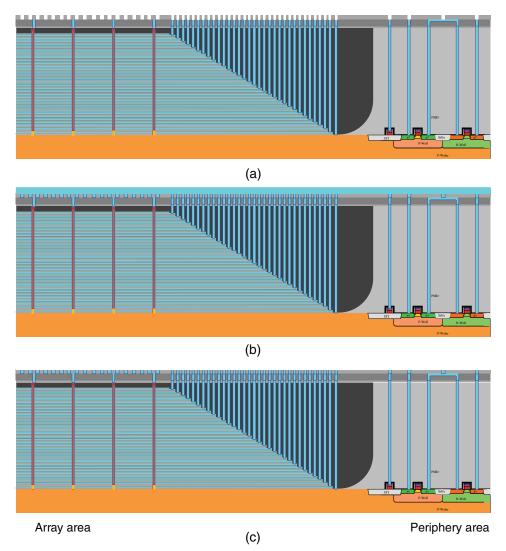

Figure 1.51 illustrates the cross-section of BWL DRAM with both the array area and peripheral area. It has four metal layers: M1 is W, M2 and M3 are Cu, and M4 is an Al-Cu alloy. The wafer has finished processing, and it is ready for electrical test. The WAT will determine the yield data of

**Figure 1.49** Cross-section of via 3 process steps: (a) ESL and ILD6 deposition, (b) V3 etch and PR strip/clean, and (c) V3 WCMP.

the wafer process; the yield is the key for the success of the wafer fab, which is especially important for DRAM fabs because DRAM is very cost-sensitive.

# 1.3 Brief Summary of DRAM

This chapter described an advanced-technology node DRAM manufacturing processes with a BWL, recessed cylindrical capacitor, and  $6F^2$  layout. Future scaling of the DRAM has many challenges, such as capacitor formation, a new device structure, new layout, and maybe new patterning processes with EUV.

**Figure 1.50** Cross-section of V3-M4 and passivation processes: (a) after M4 Ti/l-Cu/TiN PVD, (b) after M4 etch and PR strip and clean, (c) after passivation oxide and nitride CVD, and (d) after bond pad etch and PR strip and clean.

Figure 1.50 (Continued)

As addressed earlier, the capacitor is the most challenging part of the DRAM scaling. When the DRAM feature size scales down deep into a 1x-nm node, the CD and pitch of the SN cylinder holes could become too small to allow a recessed cylinder to form a double-sided capacitor; the capacitor must return to the single-side cylinder without recess, similar to the one shown in Fig. 1.8, with a much higher aspect ratio. Because the aspect ratio of the recessed cylinder capacitor is already  $\sim$ 50:1, the aspect ratio of a cylinder capacitor with a smaller CD and without recess could easily go higher than 200:1 if the same high-k dielectric (ZAZ) is still used. To control the aspect ratio within 100:1, a new capacitor dielectric with a k value significantly higher than ZAZ ( $k\sim$ 20) is needed. One such candidate is strontium titanate (SrTiO<sub>3</sub> or STO, k=146 in bulk material) using ALD to achieve excellent step coverage ( $\sim$ 95%), high thickness uniformity, and good stoichiometry. 12

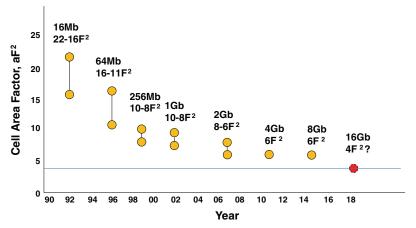

Figure 1.52 illustrates the DRAM array-area factor improvement in recent years. The smallest achievable unit array area for a planar device is  $4F^2$ ,

Table 1.10 V3-M4 and passivation process steps.

| ESL and ILD6 deposition [Fig. 1.49(a)] | M4 mask                                                 |

|----------------------------------------|---------------------------------------------------------|

| V3 mask                                | Etch TiN/Al-Cu/Ti stack                                 |

| ILD6 and ESL etch                      | PR strip/clean [Fig. 1.50(b)]                           |

| PR strip and clean [Fig. 1.49(b)]      | Passivation oxide and nitride deposition [Fig. 1.50(c)] |

| 5Ti/TiN/W deposition                   | Bond pad mask                                           |

| W/TiN/Ti CMP [Fig. 1.49(c)]            | Etch nitride and oxide                                  |

| Wafer clean                            | PR strip and clean [Fig. 1.50(d)]                       |

| Ti/Al-Cu/TiN deposition [Fig. 1.50(a)] |                                                         |

Figure 1.51 Cross-section of BWL DRAM with four metal interconnection layers.

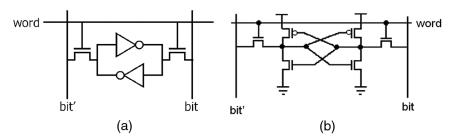

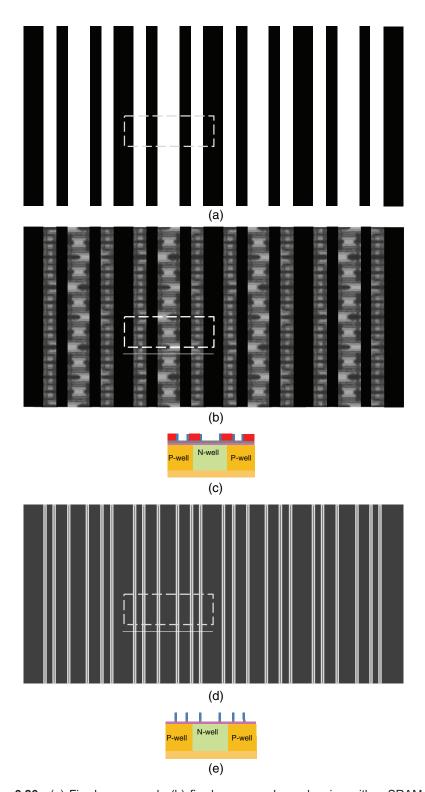

which has been used in planar NAND flash cell design. Theoretically, DRAM can also achieve a unit array area of  $4F^2$  with a vertical cell transistor and buried bit-line design, as shown in Fig. 1.53. Figure 1.53(a) shows the  $4F^2$  DRAM cell layout. It can be seen from Fig. 1.53(b) that the device architecture is quite different from the previous generation. The BL is buried, and the cell transistor is a vertical gate-all-around fully depleted MOSFET. This type of DRAM has not yet been used in DRAM chip production.

Figure 1.52 DRAM array-area factor scaling, based on Ref. C.

**Figure 1.53** (a) Layout of a  $4F^2$  DRAM, and (b) 3D illustration of  $4F^2$  DRAM.

#### 1.4 Review Questions

- 1. How many devices are in a DRAM unit cell? What types of devices?

- 2. List at least three types of DRAM cell transistors.

- 3. What are the advantages of a 3D capacitor compared to a 2D planar capacitor?

- 4. Explain how can BWL DRAM reduce three photolithography masks from RG DRAM while forming the cell transistor/WL, contacts, and SN capacitor?

- 5. What is the benefit of recessing a SN cylinder?

- 6. Describe the needs of high-k dielectric in DRAM manufacturing.

- 7. Explain why a SN capacitor is the most challenging part of DRAM scaling.

- 8. Describe the benefits and challenges of scaling a DRAM cell from  $8F^2$  to  $6F^2$  and then  $4F^2$ .

# Chapter 2 3D-NAND Flash and Its Manufacturing Process

After reading this chapter, you should be able to

- Draw and describe a NAND flash memory cell;

- Give the minimum unit-cell size of planar NAND flash in relationship to the technology node;

- Explain the advantages of 3D-NAND flash compared to planar NAND flash; and

- List at least two processes in the 3D-NAND manufacturing process that need HAR etch.

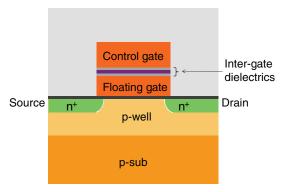

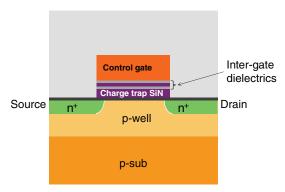

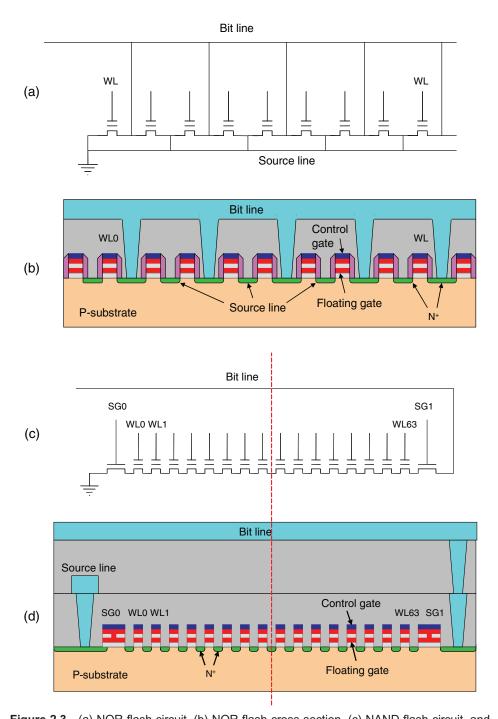

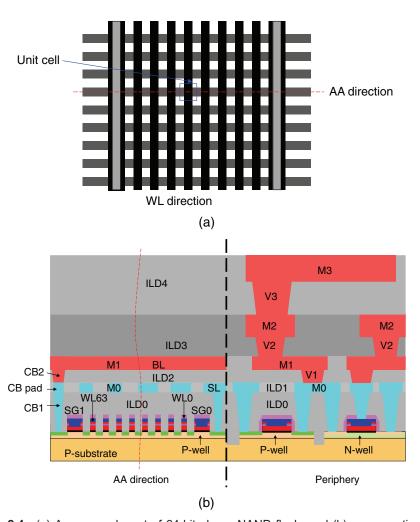

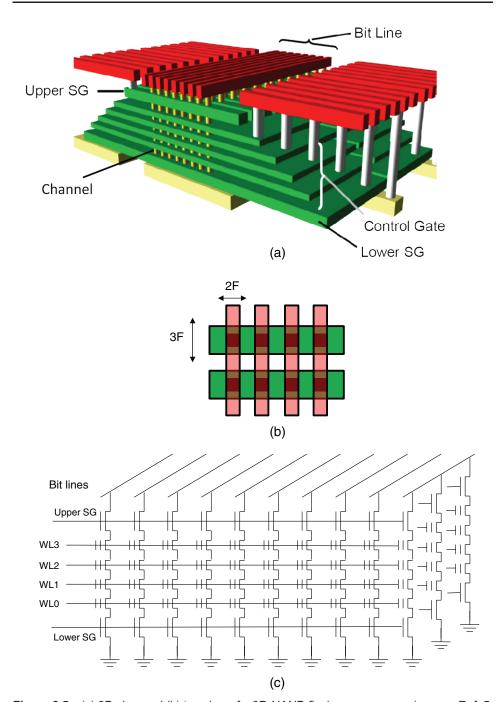

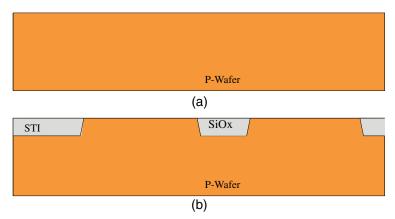

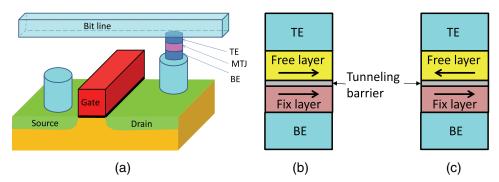

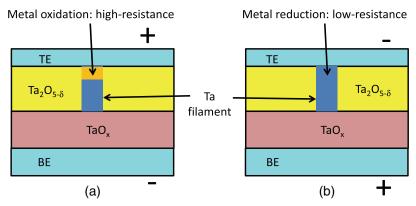

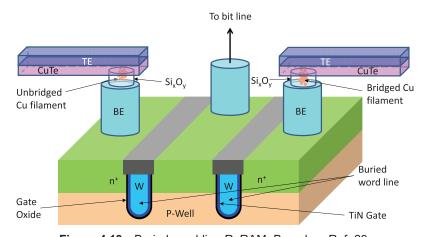

#### 2.1 Introduction