# Copper Interconnect Technology

#### **Tutorial Texts Series**

- Copper Interconnect Technology, Christoph Steinbrüchel and Barry L. Chin, Vol. TT46

- Optical Design for Visual Systems, Bruce H. Walker, Vol. TT45

- Fundamentals of Contamination Control, Alan C. Tribble, Vol. TT44

- Evolutionary Computation: Principles and Practice for Signal Processing, David Fogel, Vol. TT43

- · Infrared Optics and Zoom Lenses, Allen Mann, Vol. TT42

- Introduction to Adaptive Optics, Robert K. Tyson, Vol. TT41

- Fractal and Wavelet Image Compression Techniques, Stephen Welstead, Vol. TT40

- · Analysis of Sampled Imaging Systems, R. H. Vollmerhausen and R. G. Driggers, Vol. TT39

- Tissue Optics: Light Scattering Methods and Instruments for Medical Diagnosis, Valery Tuchin, Vol. TT38

- Fundamentos de Electro-Óptica para Ingenieros, Glenn D. Boreman, translated by Javier Alda, Vol. TT37

- Infrared Design Examples, William L. Wolfe, Vol. TT36

- · Sensor and Data Fusion Concepts and Applications, Second Edition, L. A. Klein, Vol. TT35

- Practical Applications of Infrared Thermal Sensing and Imaging Equipment, Second Edition, Herbert Kaplan, Vol. TT34

- Fundamentals of Machine Vision, Harley R. Myler, Vol. TT33

- · Design and Mounting of Prisms and Small Mirrors in Optical Instruments, Paul R. Yoder, Jr., Vol. TT32

- · Basic Electro-Optics for Electrical Engineers, Glenn D. Boreman, Vol. TT31

- · Optical Engineering Fundamentals, Bruce H. Walker, Vol. TT30

- · Introduction to Radiometry, William L. Wolfe, Vol. TT29

- · Lithography Process Control, Harry J. Levinson, Vol. TT28

- An Introduction to Interpretation of Graphic Images, Sergey Ablameyko, Vol. TT27

- Thermal Infrared Characterization of Ground Targets and Backgrounds, P. Jacobs, Vol. TT26

- Introduction to Imaging Spectrometers, William L. Wolfe, Vol. TT25

- Introduction to Infrared System Design, William L. Wolfe, Vol. TT24

- Introduction to Computer-based Imaging Systems, D. Sinha, E. R. Dougherty, Vol. TT23

- Optical Communication Receiver Design, Stephen B. Alexander, Vol. TT22

- Mounting Lenses in Optical Instruments, Paul R. Yoder, Jr., Vol. TT21

- Optical Design Fundamentals for Infrared Systems, Max J. Riedl, Vol. TT20

- An Introduction to Real-Time Imaging, Edward R. Dougherty, Phillip A. Laplante, Vol. TT19

- Introduction to Wavefront Sensors, Joseph M. Geary, Vol. TT18

- Integration of Lasers and Fiber Optics into Robotic Systems, J. A. Marszalec, E. A. Marszalec, Vol. TT17

- An Introduction to Nonlinear Image Processing, E. R. Dougherty, J. Astola, Vol. TT16

- · Introduction to Optical Testing, Joseph M. Geary, Vol. TT15

- Image Formation in Low-Voltage Scanning Electron Microscopy, L. Reimer, Vol. TT12

- · Diazonaphthoquinone-based Resists, Ralph Dammel, Vol. TT11

- Infrared Window and Dome Materials, Daniel C. Harris, Vol. TT10

- · An Introduction to Morphological Image Processing, Edward R. Dougherty, Vol. TT9

- An Introduction to Optics in Computers, Henri H. Arsenault, Yunlong Sheng, Vol. TT8

- Digital Image Compression Techniques, Majid Rabbani, Paul W. Jones, Vol. TT7

- Aberration Theory Made Simple, Virendra N. Mahajan, Vol. TT6

- Single-Frequency Semiconductor Lasers, Jens Buus, Vol. TT5

- An Introduction to Biological and Artificial Neural Networks for Pattern Recognition, Steven K. Rogers, Matthew Kabrisky, Vol. TT4

- · Laser Beam Propagation in the Atmosphere, Hugo Weichel, Vol. TT3

- Infrared Fiber Optics, Paul Klocek, George H. Sigel, Jr., Vol. TT2

- Spectrally Selective Surfaces for Heating and Cooling Applications, C. G. Granqvist, Vol. TT1

# Copper Interconnect Technology

## Christoph Steinbrüchel Barry L. Chin

Tutorial Texts in Optical Engineering Volume TT46

Arthur R. Weeks, Jr., Series Editor Invivo Research Inc. and University of Central Florida

#### SPIE PRESS

A Publication of SPIE—The International Society for Optical Engineering Bellingham, Washington USA

#### Library of Congress Cataloging-in-Publication Data

Steinbrüchel, Christoph

Copper interconnect technology / Christophe Steinbrüchel and Barry L. Chin p. cm – (Tutorial texts in optical engineering; v. TT46)

Includes bibliographical references and index.

ISBN 0-8194-3897-9 (softcover)

1. Electronic packaging. 2. Semiconductors–Junctions. 3. Microelectronic packaging. 4. Copper. I. Chin, Barry. II. Title. III. Series.

TK7870.15 .S74 2001 621.381'046-dc21

00-045049 CIP

#### Published by

SPIE—The International Society for Optical Engineering

P.O. Box 10

Bellingham, Washington 98227-0010

Phone: 360/676-3290 Fax: 360/647-1445 Email: books@spie.org WWW: www:spie.org

Copyright © 2001 The Society of Photo-Optical Instrumentation Engineers

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means without written permission of the publisher.

PDF ISBN: 9781510608030

Printed in the United States of America.

## Introduction to the Series

The Tutorial Texts series was initiated in 1989 as a way to make the material presented in SPIE short courses available to those who couldn't attend and to provide a reference book for those who could. Typically, short course notes are developed with the thought in mind that supporting material will be presented verbally to complement the notes, which are generally written in summary form, highlight key technical topics, and are not intended as stand-alone documents. Additionally, the figures, tables, and other graphically formatted information included with the notes require further explanation given in the instructor's lecture. As stand-alone documents, short course notes do not generally serve the student or reader well.

Many of the Tutorial Texts have thus started as short course notes subsequently expanded into books. The goal of the series is to provide readers with books that cover focused technical interest areas in a tutorial fashion. What separates the books in this series from other technical monographs and textbooks is the way in which the material is presented. Keeping in mind the tutorial nature of the series, many of the topics presented in these texts are followed by detailed examples that further explain the concepts presented. Many pictures and illustrations are included with each text, and where appropriate tabular reference data are also included.

To date, the texts published in this series have encompassed a wide range of topics, from geometrical optics to optical detectors to image processing. Each proposal is evaluated to determine the relevance of the proposed topic. This initial reviewing process has been very helpful to authors in identifying, early in the writing process, the need for additional material or other changes in approach that serve to strengthen the text. Once a manuscript is completed, it is peer reviewed to ensure that chapters communicate accurately the essential ingredients of the processes and technologies under discussion.

During the past nine years, my predecessor, Donald C. O'Shea, has done an excellent job in building the Tutorial Texts series, which now numbers nearly forty books. It has expanded to include not only texts developed by short course instructors but also those written by other topic experts. It is my goal to maintain the style and quality of books in the series, and to further expand the topic areas to include emerging as well as mature subjects in optics, photonics, and imaging.

Arthur R. Weeks, Jr. Invivo Research Inc. and University of Central Florida

## **CONTENTS**

| 1. | Intro             | oduction                                                          | 1  |

|----|-------------------|-------------------------------------------------------------------|----|

|    |                   | Acknowledgments                                                   | 3  |

| 2. |                   | rconnect Issues                                                   | 5  |

|    | 2.1               | Overview                                                          | 5  |

|    |                   | Materials requirements                                            | 10 |

|    |                   | Materials options                                                 | 13 |

|    | 2.4               | Multilevel interconnect fabrication                               | 14 |

| 3. | Cop               | per Deposition                                                    | 19 |

|    | 3.1               | Overview                                                          | 19 |

|    | 3.2               | Chemical deposition methods for copper                            | 19 |

|    |                   | 3.2.1 Chemical vapor deposition (CVD)                             | 20 |

|    |                   | 3.2.2 Electrochemical plating (ECP)                               | 24 |

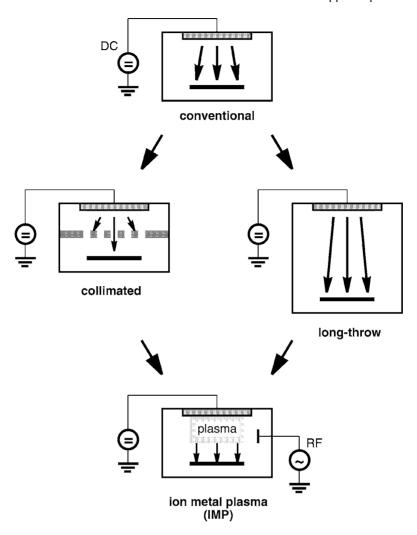

|    | 3.3               | Physical deposition methods for copper                            | 28 |

|    |                   | 3.3.1 Collimated and long-throw sputter deposition                | 29 |

|    |                   | 3.3.2 Ionized physical vapor deposition (IPVD)                    | 31 |

| 4. | Copper Patterning |                                                                   |    |

|    | 4.1               | Overview                                                          | 35 |

|    | 4.2               | Subtractive copper patterning                                     | 35 |

|    |                   | 4.2.1 Reactive ion etching of copper                              | 36 |

|    |                   | 4.2.2 Etching of copper in high-density plasmas (MIE, ECR, ICP) . | 38 |

|    |                   | 4.2.3 Radiation-enhanced RIE of copper                            | 40 |

|    | 4.3               | Additive copper patterning by chemical-mechanical polishing (CMP) | 41 |

| 5. | Inte              | rlayer Dielectrics                                                | 47 |

|    | 5.1               | Silicate-based ILDs                                               | 49 |

|    |                   | 5.1.1 Undoped Si oxides                                           | 49 |

|    |                   | 5.1.2 Doped Si oxides                                             | 51 |

|    | 5.2               | Organic polymer-based ILDs                                        | 58 |

|    |                   | 5.2.1 Non-fluorinated organic polymers                            | 58 |

|    |                   | 5.2.2 Fluorinated organic polymers                                | 60 |

|    | 5.3               | Patterning of ILDs                                                | 63 |

|    |                   | 5.3.1 Overview                                                    | 63 |

|    |                   | 5.3.2 Patterning of silicate-based II Ds                          | 64 |

#### viii Contents 5.3.4 Etching dual-damascene structures into the ILD . . . . . . . 5.3.6 Planarization of low-k ILDs by CMP . . . . . . . . . . . . . . 6.3

7.3

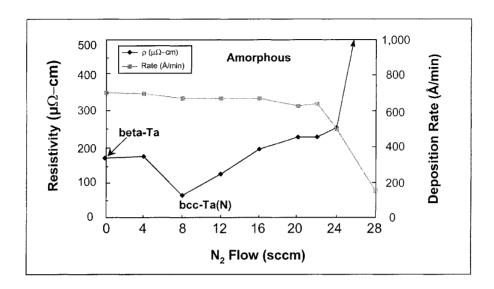

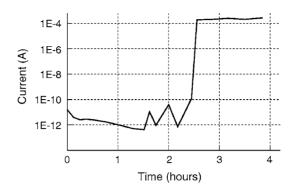

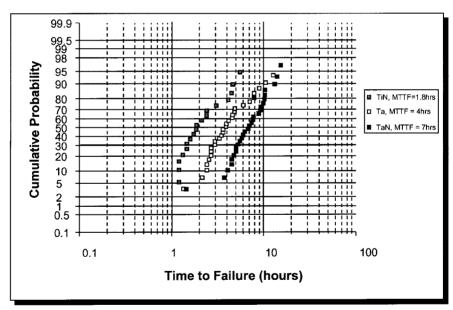

Barrier layers

7.5 Future directions

### INTRODUCTION

The semiconductor industry is continuing its quest to create ever more powerful CPU and memory chips. These efforts are focused principally in two areas. On one hand, the speed of individual devices is increased through the continual reduction of the minimum size of device features. Along with this goes a corresponding increase in device density on the chip. On the other hand, in order to take advantage of increased device speeds, one needs to connect individual devices into circuits using increasingly complex interconnect schemes. These now involve multilayer structures made up of several levels of metal wiring separated by an interlayer dielectric (ILD). Efforts in both of these areas are supported by more and more sophisticated device and circuit design.

The exact nature of the trade-off between individual device and interconnect performance depends on details of the circuit architecture. However, it is now generally recognized that the overall circuit performance is going to be dominated by the efficiency with which devices are connected rather than by the speed of the individual devices. From the materials point of view, a better interconnect efficiency may be achieved with various new materials combinations for the metal and the interlayer dielectric (ILD). It is now becoming apparent that a major component of improved interconnect performance will consist in replacing aluminum, the previous metal of choice, with copper.

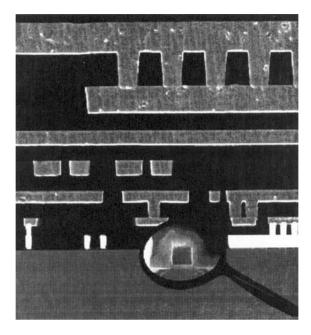

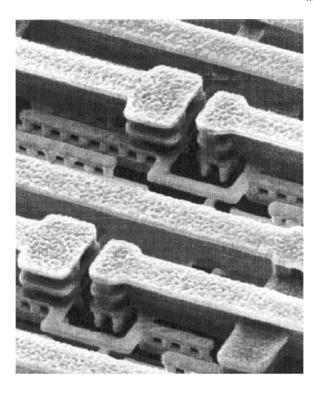

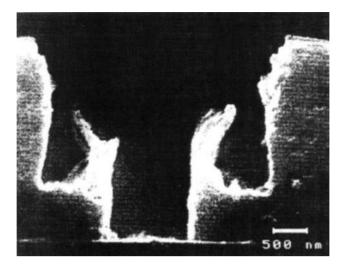

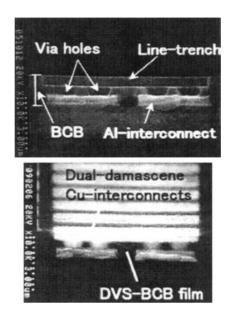

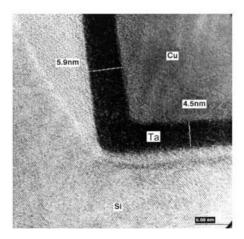

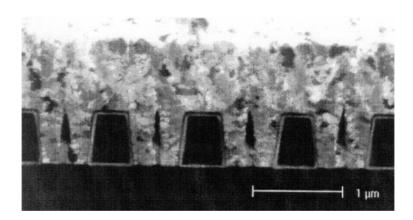

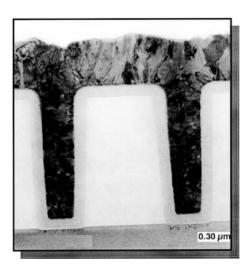

Several companies announced recently that they have been successful in fabricating ultralarge-scale integrated (ULSI) circuits using Cu.<sup>2–5</sup> IBM<sup>2</sup> was first to publish pictures showing interconnect structures with six levels of Cu metal (M1-M6, see Figs. 1 and 2). Some of the features of the announced Cu processes are given below. The IBM process has been described in detail in Ref. [3].

IBM:<sup>4a</sup>

CMOS process (Cu with SiO<sub>2</sub>); M1 contacted pitch 0.63  $\mu$ m, M2-M6 contacted pitch 0.91  $\mu$ m, local tungsten interconnects, gate length 0.20  $\mu$ m, SRAM cell size 6.8  $\mu$ m<sup>2</sup>.

Motorola:5

CMOS process (Cu with SiO<sub>2</sub>); M1 pitch 0.63  $\mu$ m, M6 pitch 1.62  $\mu$ m, gate length 0.15  $\mu$ m, SRAM cell size 7.6  $\mu$ m<sup>2</sup>.

Texas Instruments:<sup>6</sup>

Interconnect tests structures with 0.3 µm Cu lines embedded in xerogel, capped with silicon nitride and silicon oxide.

Figure 1 Scanning electron micrograph of IBM six-level Cu interconnect structure: cross section.

Very recently, IBM reported on two technologies involving Cu and an ILD with lower dielectric constant than silicon dioxide. In the first paper, the integration of fluorine-doped oxide with Cu for the 0.18-µm node has been described. In the second paper, the application of Cu and an organic material as the ILD for the 0.13-µm technology node has been demonstrated. (For further details see Sec. 7.)

The purpose of this book is to present a tutorial overview of the issues involved in implementing the use of copper in future interconnect technologies. We will attempt to give the reader an appreciation of the range of problems involved and the avenues along which solutions to these problems are being sought. With this focus in mind, we will not try to deal exhaustively with all the technical issues in every area covered. This would be beyond the scope of this book. Rather, we will provide representative examples of the most important technical approaches being pursued and references to more in-depth information elsewhere. In order to put our arguments in perspective, it will be worth taking note of Ref. [7], which contains an extensive discussion of previous, aluminum-based interconnect technologies as well as early work in copper technology.

The organization of the book is as follows: We start with a brief description of the status, major issues, and materials options for interconnect technologies. Next, we illustrate in general terms different approaches to the fabrication of mul-

Figure 2 Scanning electron micrograph of IBM six-level Cu interconnect structure: perspective view.

tilayer interconnect structures, with particular emphasis on how to create patterned multilayers. This includes a comparison of subtractive patterning, as used with Al metallization, and damascene patterning, as used with Cu metallization. We then give a general discussion of Cu deposition and patterning, interlayer dielectrics, Cu diffusion barriers and passivation, and Cu/barrier/ILD issues, with a focus on scientific fundamentals, potential process alternatives, and future options. We conclude with a detailed description of the preferred approaches and technological practices being implemented at this time.

#### **ACKNOWLEDGMENTS**

Barry L. Chin would like to acknowledge the support from the Applied Materials executive management and the contributions of the various organizations within Applied Materials who produced the data on copper metallization referenced in this book: Copper Barrier/Seed, Electroplating, and the SEM/TEM Analytical groups.

## INTERCONNECT ISSUES

#### 2.1 OVERVIEW

Several factors contribute to the performance of a particular interconnect scheme, including its architecture and the properties of the materials involved. A basic figure of merit to such a scheme is its RC delay, which represents a measure of the time delay for signal propagation. R denotes the resistance of an interconnect metal line, and C denotes the effective capacitance between the line and its surroundings.

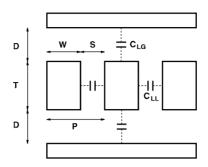

The estimated effect of various geometrical and materials parameters on the RC delay can be obtained by considering the test structure of Fig. 3, which is similar to the one used in Refs. [8] and [9]. The test structure employs a set of metal lines between two grounded metal planes, all embedded in the interlayer dielectric medium. Let us assume that the metal line width is W, the metal line thickness is T, the spacing between two lines is S, the metal line pitch is P (with P = W + S), and the thickness of the ILD between the top of the metal lines and the grounded planes is D. Also, let L = length of a metal line and  $\rho = \text{metal}$  resistivity. We will use the pitch P and the metal thickness T as basic parameters, so that we can set W = aP and D = bT where a and b are constants appropriate for the given geometry.

The resistance R of a metal line is then given by

$$R = \rho L/WT = \rho L/aPT. \tag{1}$$

If the ILD has an isotropic relative dielectric constant k and one neglects edge contributions from the metal lines as well as coupling of the metal line sidewalls to the ground planes, then one has

$$C_{LG} = k\varepsilon_0 W L/D = k\varepsilon_0 a P L/bT, \tag{2}$$

and

$$C_{LL} = k\varepsilon_0 T L/S = k\varepsilon_0 T L/(P - W) = k\varepsilon_0 T L/(1 - a)P,$$

(3)

where  $\varepsilon_o$  is the permittivity of free space. In Eqs. (2) and (3),  $C_{LG}$  represents the "vertical" capacitance between a metal line and a ground plane above (or below),

Figure 3 Simplified RC delay test structure.

and  $C_{LL}$  represents the "horizontal" capacitance between two neighboring lines. For the total capacitance C of a metal line relative to its surroundings one can write

$$C = 2(C_{LG} + C_{LL}) = 2k\varepsilon_o L[aP/bT + T/(1-a)P]. \tag{4}$$

For the RC time delay constant, it follows that

$$RC = 2R(C_{LG} + C_{LL}), \tag{5}$$

or, combining Eqs. (1), (4) and (5),

$$RC = 2\rho k \varepsilon_0 L^2 [1/bT^2 + 1/a(1-a)P^2].$$

(6)

Equivalently one can write

$$RC = 2\rho k \varepsilon_o (L^2/P^2) [P^2/bT^2 + 1/a(1-a)]. \tag{7}$$

The right-hand side of Eq. (6) has a natural interpretation, in that the factors  $2\rho k\varepsilon_o$  and  $L^2(1/bT^2+1/a(1-a)P^2)$  represent the materials and architecture contributions to the interconnect time delay.

Equation (7) can be examined from a slightly different point of view if one defines the aspect ratio A of the metal lines as the ratio of line thickness to line width, A = T/W, or equivalently A = T/aP. In terms of A, Eq. (7) can be expressed as

$$RC = 2\rho k \varepsilon_o (L^2/P^2) (1/a^2 b A^2 + 1/a(1-a)).$$

(8)

Keep in mind that the term  $1/a^2bA^2$  in Eq. (8) represents the "vertical" and the term 1/a(1-a) the "horizontal" contribution to the total capacitance.

We conclude from Eqs. (7) and (8) that for fixed line length L and fixed aspect ratio A, the RC delay increases quadratically with decreasing feature size (decreasing pitch P). In addition, Eqs. (7) and (8) imply that for  $A \ll 1$  the interlayer ("vertical") capacitance is more important to the RC delay than the intralayer ("horizontal") capacitance, whereas the opposite is true for  $A \gg 1$ . Also note that for the simplest geometry where a = 0.5 and b = 1 (D = T), Eq. (8) reduces to

$$RC = 8\rho k \varepsilon_o (L^2/P^2) (1/A^2 + 1).$$

(9)

Using the assumptions above, one can generalize Eqs. (7) and (8) to the case where the ILD is not isotropic. If the ILD has a "vertical" (between-layer) dielectric constant  $k_{LG}$  and a "horizontal" (between-lines) dielectric constant  $k_{LL}$ , then one obtains

$$RC = 2\rho \varepsilon_0 (L^2/P^2) [k_{LG}/a^2bA^2 + k_{LL}/a(1-a)].$$

(10)

Again, for the simplest geometry where a=0.5 and b=1 (D=T), Eq. (10) reduces to

$$RC = 8\rho\varepsilon_o(L^2/P^2)(k_{LG}/A^2 + k_{LL}). \tag{11}$$

For a semi-quantitative comparison, consider Eq. (11) with some Cu and Al interconnect structures. Let L, W, P, and D be fixed (W=0.5P, a=0.5). Let  $T_{\rm Cu}=D$  ( $b_{\rm Cu}=1$ ), and let both metal lines have the same resistance, which requires that  $T_{\rm Al}=1.3T_{\rm Cu}$  ( $\rho_{\rm Al}=1.3\rho_{\rm Cu}$ ,  $b_{\rm Al}=1/1.3$ ). In other words, the geometries are the same except that the aspect ratio of the Al lines is 1.3 times the aspect ratio of the Cu lines. From Eq. (10) it follows that the expressions ( $k_{LG}/A_{\rm Cu}^2+k_{LL}$ ) for Cu and ( $k_{LG}/A_{\rm Cu}^2+1.3k_{LL}$ ) for Al represent figures of merit, being proportional to the respective RC delays.

Numerical examples are listed below for  $A_{\text{Cu}} = 2$  and  $A_{\text{Cu}} = 2.6$ . With Cu, an isotropic ILD is assumed, whereas with Al the spaces between lines are assumed to be filled with a material of lower  $k_{LL}$ .

Cu:

$$k_{LG} = k_{LL} = 4.3$$

$k_{LG}/A_{Cu}^2 + k_{LL} = 5.4$

$3.9$   $4.9$

$2.7$   $3.4$

$2.0$   $2.5$

Al:  $k_{LG} = 4.3, k_{LL} = 2.7$   $k_{LG}/A_{Cu}^2 + 1.3k_{LL} = 4.6$

$2.0$   $3.7$

$1.3$   $2.8$

$k_{LG} = 3.9, k_{LL} = 1.2$   $2.5$

The numbers for  $k_{LG}$  and  $k_{LL}$  are representative of normal oxide (4.3), F-doped oxide (3.9), a current low-k polymer (2.7), a lower-k future polymer or porous material (2.0), and a highly porous, or air-gap, material (1.3, 1.2). From these results one may conclude, for example, that Al with intralayer airgaps could be almost equivalent to Cu with an isotropic, teflon-like ILD. It should be pointed out, however, that the numerical comparison depends on the details of the ILD structure. If the entire geometry were the same for both Cu and Al (i.e., equal aspect ratios), the figure of merit for Al would also be represented by  $k_{LG}/A_{Cu}^2 + k_{LL}$ , which would give slightly larger numerical values for Al.

The results above illustrate how important  $k_{LL}$  is, especially for high-aspect ratio structures, and that a high aspect ratio mitigates the influence of  $k_{LG}$ . In addition, note that the contribution proportional to 1/a(1-a) in Eqs. (8) and (10), due to the intralayer capacitance, is minimized when a=0.5, that is when the metal line width W is equal one half of the pitch P.

In interpreting Eqs. (7) to (11) it is important to keep in mind that as devices and their interconnect dimensions are reduced in size, the ratio L/P does not stay constant but rather increases, because the metal line lengths L tend to scale less strongly than the metal pitch  $P.^{9-11}$  That is, even as devices keep shrinking, they still contain some rather long lines. <sup>242,243</sup> For example, for a 4M-gate circuit block with 7 metal levels and using 260 nm design rules, several hundred metal line segments longer than 1 mm were found. <sup>243</sup> Modeling the wiring distribution in the Intel Pentium Klamath design shows that most wires are 1–10  $\mu$ m long, yet there is also a not insignificant number of wires (of the order of 0.1%) as long as 1–10 mm. <sup>12</sup> At the same time, the aspect ratio A tends to increase because R needs to be kept as low as possible in order for electrical power dissipation to be minimized (see Fig. 1). When applied to Eqs. (7) to (11), these geometrical constraints lead to two conclusions: For a given set of interconnect materials (that is, for fixed  $\rho$  and k), as device dimensions are reduced,

- (1) the RC delay will increase;

- (2) the overall capacitance will be dominated by the intralayer capacitance, which will also give rise to increased line-to-line crosstalk.

As far as the relative importance of intrinsic and interconnect delays is concerned, it should be pointed out that the exact feature size at which the interconnect RC delay equals and then surpasses the intrinsic transistor delay depends on details of the circuit design. Moreover, the total overall time delay  $t_{int}$  is composed of four components and can be approximated by<sup>243</sup>

$$t_{int} = R_0 C + 0.4 [(RC)^{1.6} + (tof)^{1.6}]^{1/1.6} + 0.7 RC_{in},$$

(12)

where  $R_0$  is the output resistance of the driver device, tof the time of flight of the electromagnetic wave in the interconnect, and  $C_{in}$  the input capacitance of the device in the next gate. These four terms contribute differently to the overall delay depending on gate length and width, interconnect line length L, and other geometrical parameters.  $^{1,3,10,11,243}$  In one case, the effect of various approaches to relaxing design rules in upper interconnect metal levels has been investigated.  $^{243}$  Note that the upper levels of metallization are used for power distribution where electromigration is a major concern. However, all these results point to a minimum feature size of the order of 0.5  $\mu$ m at which the interconnect RC delay starts to become more significant than the intrinsic transistor delay.  $^{1,8-11}$  The consequences of interconnect length, scaling, and material properties on crosstalk between distributed RC lines have also been discussed.  $^{244}$

Equations (7) to (11) provide some general insight as to how the interconnect RC delay can be minimized. With respect to circuit architecture one can conclude that as the minimum feature size and thus the pitch P in the lower interconnect metal levels decrease, the line length L should be reduced as much as possible. This may ultimately require using block designs or repeaters. Conversely, for lines with large L the pitch P should be large. This means that long interconnect lines should only be used in the upper interconnect metal layers where there is room for increased pitch. Therefore, an interconnect scheme will involve a hierarchy of scales, with the smallest lines in the first metal layer and progressively fatter and longer lines in the upper layers. This type of approach also helps to improve other aspects of chip performance, such as coupled-noise induced delays and clock skew.<sup>3</sup>

On the interconnect materials side, it is evident that one should use the metal with the lowest possible resistivity  $\rho$  and the ILD with the lowest possible dielectric constant k. With regard to the metal, this means using copper. With regard to the ILD, it will be especially helpful to selectively reduce the  $k_{LL}$  between the metal lines. Some of the benefits of this latter approach have already been demonstrated.

It is also worth pointing out that the decrease in minimum feature size is predicted to be accompanied by an increase in the complexity of the interconnect structure itself, in particular by a rapid increase in the number of metal layers necessary to achieve clock frequency targets. ^13 As the minimum feature size reaches the  $0.1~\mu m$  range, this number may, in fact, become prohibitive from the point of view of being manufacturable, unless new designs involving smaller circuit blocks will be implemented. ^13

#### 2.2 MATERIALS REQUIREMENTS

Since we will focus on materials issues related to optimizing interconnections, let us note that in the traditional interconnect technologies the metal of choice has been Al and the ILD has been  $SiO_2$ .<sup>8</sup> This materials system has some unique advantages compared to potential replacements, as we shall see in detail below, and it has also evolved into mature fabrication technology. As a point of reference for materials parameters, let us keep in mind that  $\rho = 2.7 \,\mu\Omega$  cm for pure Al and k = 4.2 for the type of  $SiO_2$  typically used as an ILD. However, Al is often alloyed with Si and/or Cu for reasons of stability with respect to the interaction with Si and for improved electromigration resistance. With the introduction of salicided junctions, the need for Si addition to Al has been removed. Also, in Al technology contact to the underlying layer is usually made through vias filled with W plugs, which eliminates the need for Si alloying. Furthermore, in many applications a thin, higher resistivity layer is used as a barrier between the metal and the ILD or Si. These modifications result in an increased effective resistivity  $\rho_{eff}$  for the Al interconnect lines of typically about 3.3  $\mu\Omega$  cm.<sup>12</sup>

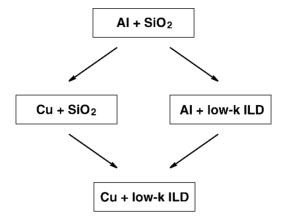

We will deal with various materials requirements for the metal and the ILD in detail shortly, but at this point it is apparent already that for the metal, the only possible options in replacing Al are Cu, Ag, and Au, and the only practical option really is Cu. Not only do costs, manufacturability, and device reliability favor Cu, but in terms of improved resistivity the additional gain in going from Cu ( $\rho_{bulk} = 1.7 \mu\Omega$  cm) to either Ag ( $\rho_{bulk} = 1.6 \mu\Omega$  cm) or Au ( $\rho_{bulk} = 1.5 \mu\Omega$  cm) would be quite minimal. Hence there are in principle two ways by which to migrate from the traditional Al/SiO<sub>2</sub> interconnect technology to an ultimate solution involving Cu/low-*k* ILD, depending on whether the metal or the ILD is replaced first (Fig. 4).

In contrast to the situation with the metals, the choices for the best ILD are much more open, and it is unclear at this point whether there will be a single winner in the end. Therefore, using a conservative but realistic  $\rho_{eff}$  for Cu of 2.6  $\mu\Omega$  cm<sup>12</sup> and k=1 for air as the ideal ILD, the RC delay could be improved by a factor of at best about 5.3 relative to Al/SiO<sub>2</sub>. A more realistic estimate is probably a factor of about 2.8, corresponding to an ILD with k around 2, or a little lower than 2.

The particular requirements for Cu to replace Al fall into three categories: control of the microstructure, patterning for creating fine lines, and control of the metal/ILD interface. First, the microstructure of Cu determines its resistivity and resistance to electromigration and is a function of the deposition method, the deposition conditions, and the nature and topography of the substrate. The deposition methods being investigated primarily are physical vapor deposition (PVD), chemical vapor deposition (CVD), and electrochemical plating (ECP). Second, the optimal patterning method for Cu appears to be the damascene (inlaid) technique, whereby the desired patterns are actually formed in the ILD and then filled with

Figure 4 Materials options for migration from Al/SiO<sub>2</sub> to Cu/low-k interconnect technology.

the metal. The third important issue is the stability of the Cu/ILD interface. This is exemplified on the one hand by the rather weak adhesion of Cu to most ILD materials and the strong tendency of Cu to diffuse into and through the ILD, and on the other hand by the rapid oxidation of Cu in an oxidizing environment. (Thus Cu cannot be used without diffusion barriers and passivation layers.) All these issues have a significant bearing on the overall integration of Cu into a manufacturing process and eventually on the long-term reliability of Cu devices.

With regard to several of the issues just mentioned, it turns out that Al has significant advantages over Cu, 7 not the least of which is that Al technology has matured over a long period of time, and extensive experience has been accumulated with the material in the semiconductor industry. Let us note first that the deposition of Al is fairly straightforward, involving the PVD process of sputter deposition, often in combination with elevated substrate temperature. Neither the deposition method nor the temperature generally pose a problem since the ILD has been SiO<sub>2</sub> and the aspect ratios of features in the ILD that need to be filled with Al have been fairly small. However, with Cu the low-k ILD of the future may be a polymer, i.e., a material with much lower thermal stability than SiO<sub>2</sub>. This will necessitate processing with a much lower thermal budget than before. Furthermore, physical deposition methods will most likely be inadequate to fill features with the more aggressive aspect ratios that will be required in future technologies.<sup>1</sup> Second, the fine-line patterning of Al is done by reactive ion etching in a chlorinebased plasma, i.e., by a subtractive method in which those parts of a blanket Al film which are not part of the desired wiring pattern are directly and selectively removed. It is much more difficult to apply the same type of process to the patterning of Cu for reasons that we will discuss further below. Third, Al reacts with

SiO<sub>2</sub> to form a strong interface, and the native oxide layer on Al also provides self-passivation with respect to further reaction. The only clear advantage Cu has over Al at the outset, except for its lower resistivity, is that it is much more stable toward electromigration<sup>14,15</sup> and stress migration failure.<sup>3</sup> In addition, it should be mentioned that electrochemical plating, the currently favored method for Cu deposition, allows for much lower processing temperatures, thus enabling the use of ILDs with lower temperature stability than SiO<sub>2</sub>.

As we noted above, the options are more varied when it comes to the choice of an ILD, but so are the materials requirements placed on an ILD.<sup>1,8,10</sup> It may in fact turn out that several options will be implemented along the two paths illustrated in Fig. 4. A few examples of work reported along these lines include the use of Cu with a silica-based low-*k* ILD,<sup>16</sup> Cu in combination with a low-*k* polymer,<sup>17</sup> and Al with various low-*k* ILDs.<sup>10,18,19</sup> More details will be discussed below in Chapter 5 on interlayer dielectrics.

Some of the generic issues to be resolved in connection with the introduction of new ILD's are the following:

- electrical: low k overall, controlled anisotropy in k, low dissipation and leakage, high dielectric strength;

- *chemical*: chemical resistance, ability to be patterned, low moisture absorption, no metal corrosion;

- *mechanical*: adhesion (ILD-Cu, ILD-ILD), low stress, high strength (polishability);

- *thermal*: stability up to required temperature, low coefficient of thermal expansion (CTE), low thermal shrinkage, high thermal conductivity.

In terms of specific ILD materials characteristics, the following are desired, in the order of their importance:<sup>8</sup>

- (1) Low k (< 3);

- (2) Thermal stability: glass transition temperature  $T_{\rm g} > 400^{\circ}{\rm C}; < 1\%$  weight loss at  $T < 425^{\circ}{\rm C}$  in N<sub>2</sub>;

- (3) Moisture absorption: < 2% at 100% humidity;

- (4) Adhesion, ILD-metal and ILD-ILD: pass Scotch tape test; no peel after cycling to 450°C;

- (5) CTE:  $< 50 \text{ ppm/}^{\circ}\text{C} \text{ at } 200^{\circ}\text{C};$

- (6) Chemical resistance: ILD inert towards, acids, bases, and photoresist strippers;

- (7) Patterning: adequate selectivity for ILD/metal and metal/ILD in plasma etch, processable in damascene technology.

The above is only a partial list, and additional desired characteristics have been identified.<sup>8</sup>

#### 2.3 MATERIALS OPTIONS

On the basis of the arguments made above, interconnect materials options can be summarized briefly as follows: As far as the *metal* is concerned, Cu will clearly be the material of choice for future interconnect technologies. The open questions relate more to the optimal implementation of various aspects of the processing of Cu. On the other hand, it is not clear at this point which material will be used as an adhesion/diffusion barrier layer between Cu and a future low-*k* ILD, although it is evident that a barrier will be necessary. The specific choice of barrier material may well depend on the properties of the particular ILD that the barrier is intended to be combined with.

The candidates for future low-k ILDs fall into two classes of materials. The first one is comprised of a set of inorganic, *silica-based oxides*:

- doped SiO<sub>2</sub> (F-doped, with composition SiO<sub>x</sub>F<sub>y</sub> and abbreviated as FSG for fluorosilicate glass; or C-doped).

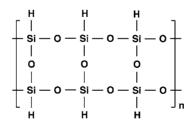

- hydrogen silsesquioxane (composition HSiO<sub>3/2</sub>, abbreviated as HSQ). Related

materials with composition RSiO<sub>3/2</sub>, where R is a side group other than H, are

also under investigation.

- xerogels (porous SiO<sub>2</sub>).

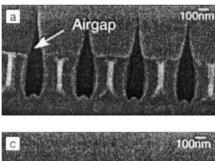

- air gap structures (metal wiring where the spaces between metal lines are only partially filled with SiO<sub>2</sub>, and thus contain voids).

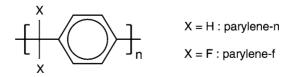

The second class of prospective ILD's involves a variety of *organic polymers*, for example:

- non-fluorinated (benzocyclobutene, parylene-n, FLARE2.0, SiLK, Black Diamond, Coral, various polyimides, etc.).

- fluorinated (perfluorinated cyclobutene, parylene-f, FLARE1.0, teflon, fluorinated amorphous carbon, etc.).

In Chapters 3 to 6, we will discuss in detail issues pertinent to the deposition and patterning of Cu films, the formation and characterization of various ILD materials, and the integration of barrier materials with Cu and ILDs.

#### 2.4 MULTILEVEL INTERCONNECT FABRICATION

In order to put the materials issues of Cu interconnect technology in perspective, it is useful to consider, in brief general terms, how multilevel interconnect structures can be fabricated. (Additional details will be provided below in the chapters on Cu and ILD processing.) Two complementary approaches can be distinguished. They have in common that they start from the same initial structure (in the figures below a Si wafer with active devices on it and covered by the first ILD layer), and they arrive at the same final wiring pattern, but in doing so they proceed differently.

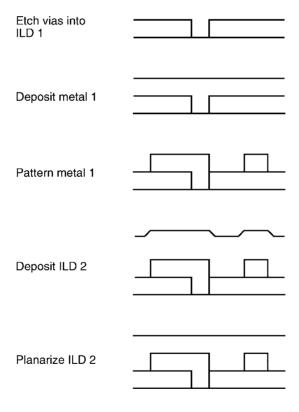

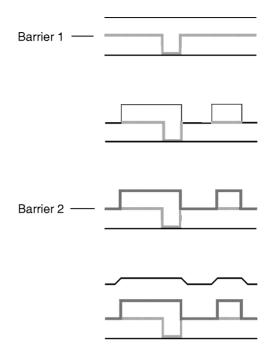

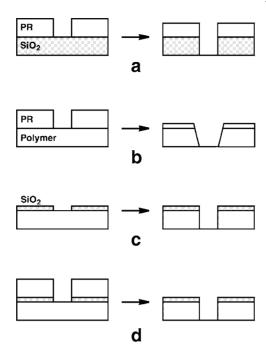

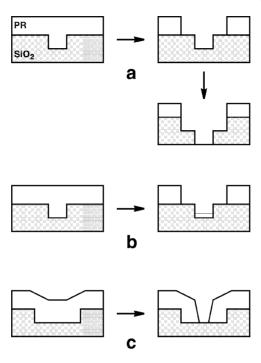

The traditional approach (used with Al/SiO<sub>2</sub>) is illustrated in Fig. 5. The metal is patterned directly by dry etching and the ILD deposited on top of the metal is planarized. For every new interconnect layer, the steps shown in Fig. 5 are repeated.

**Figure 5** Schematic process of interconnect fabrication: traditional approach using subtractive metal patterning. The steps shown resemble a process employing Al plugs in the vias, as used in earlier microelectronics technology. Present Al technology uses W plugs, which are formed by blanket CVD of W, followed by removal of the extra W in the field regions by chemical-mechanical polishing.

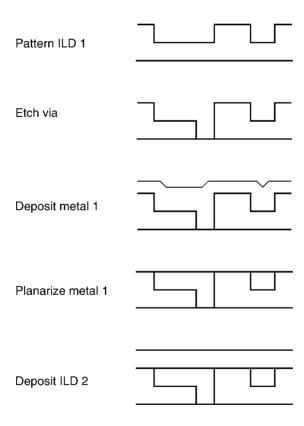

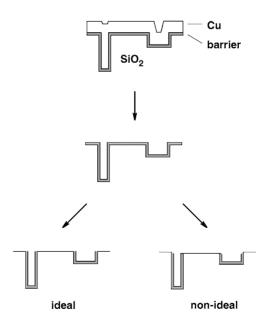

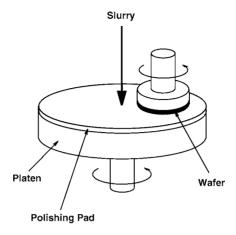

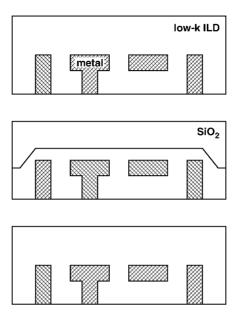

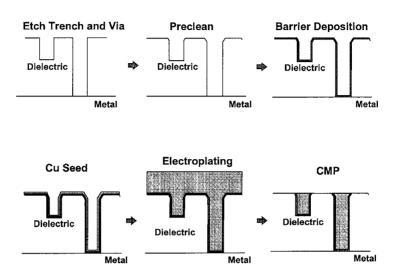

The damascene approach (used with  $Cu/SiO_2$  and most likely with Cu and low-k ILDs) is illustrated in Fig. 6. The entire wiring pattern is formed as an inlaid template in the ILD by dry etching. This pattern is then filled with metal, and finally the metal is planarized and the extra metal on top of the ILD is removed.

Note that in Figs. 5 and 6 all processing steps are not shown. Several lithography steps necessary to define the patterns in the metal and the ILD are missing, for example the steps for the definition of the via (contact hole) in the top panel of Fig. 5. Also note that both schemes require two dry, plasma etch steps to transfer the lithographically defined patterns into the underlying layer. In the traditional approach, these two steps are a dielectric etch and a metal etch. Both steps end on top of the layer underlying the material being etched, which facilitates etch end point detection. The dielectric etch of the ILD defines the vias, through which contact is made to the underlying layer, and the metal etch defines the wiring pattern connecting the vias. Together they serve to make up the structure of one interconnect

Figure 6 Schematic process of interconnect fabrication: damascene approach using inlaid, planarized metal.

level. In the damascene approach, the two etch steps are both in the ILD. One of them defines the vias and the other the actual wiring as an inlaid pattern in the ILD connecting the vias. Consequently, one of these etch steps must end in the middle of the ILD. This presents additional difficulties in terms of etch end point detection because the end point does not occur when the material has been cleared but rather when the proper etch depth has been reached. Therefore, the etch depth must be controlled precisely. In practice, this is often achieved using an intermediate etch stop such as SiN. However, the damascene approach does have one crucial advantage over the traditional approach; with damascene one can get around having to do a metal plasma etch step. In fact, the point that it is much more difficult to etch Cu than Al has turned out to be the major stumbling block in applying the traditional approach to Cu technology and has been the main driving force in the development of the damascene approach for Cu interconnect technology.

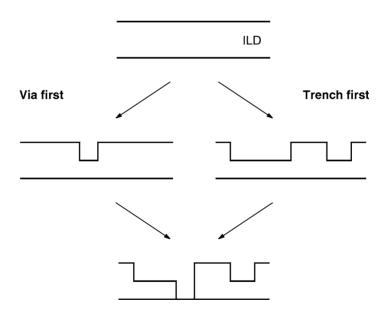

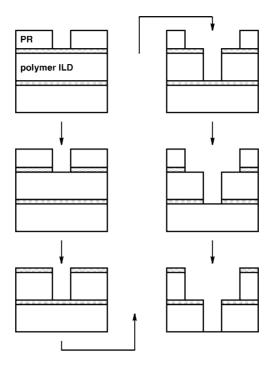

Three additional issues are worth pointing out in connection with the damascene approach. First, since two ILD patterning steps are required, the question is in which order to proceed. That is, should the vias or the trenches be formed first (Fig. 7)? If the vias are first, they could be formed halfway through the ILD, as shown in Fig. 7, or they could be formed completely down to the metal below. Each of these ways has advantages and disadvantages. Without going into details here, let us just mention that when the vias are formed first, the photoresist for

Figure 7 Damascene patterning: Via first, or trench first?

defining the second patterning step will fill the via hole and therefore be quite nonuniform in thickness across the wafer. Consequently, it will be difficult to expose the photoresist such that it clears everywhere properly. With the trenches formed first, the lithography for defining the vias must be done on an extra-thick layer of photoresist on top of a non-planar substrate. This makes it more difficult to maintain critical dimensions in that second step, which is precisely the one involving the features (vias) with the smallest dimensions (see also Sec. 5.4.3).

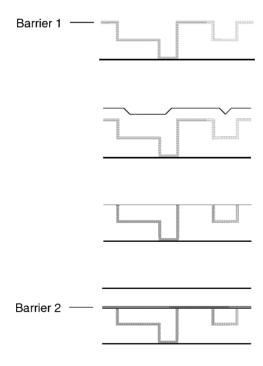

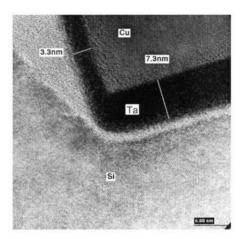

Second, the graphs in Figs. 5 and 6 give a simplified picture of the structure of real multilevel interconnects. With Cu there will have to be a barrier layer between the Cu and any ILD in contact with the Cu (Fig. 8), since Cu is a fast diffuser in practically all ILD materials investigated to date. In the planarization step, the metal is removed by chemical-mechanical polishing (CMP). In the final stage of this processing step, the Cu and the barrier layer 1 must be removed uniformly, even though these are materials with rather different chemical and mechanical properties, and the Cu surfaces must be left planar regardless of their size and pattern density. Before the next ILD layer is deposited, the barrier layer 2 has to be put down so that the top exposed Cu surfaces are also protected (Fig. 8). Moreover,

**Figure 8** Damascene patterning and Cu planarization by chemical-mechanical polishing, showing top and bottom barriers barriers.

Figure 9 Barriers in subtractive metal patterning.

it should be noted that in the first metal layer, the vias are generally filled with W so that Cu is not in direct contact with the active devices.

Two barrier layers would also be necessary for Cu interconnect structures formed by the traditional approach (Fig. 9). In that case, the metal etch also has to remove the barrier 1 material between the metal lines. In both approaches, barrier 1 ends up covering just the lower portion of the metal pattern and thus can be an electrical conductor, whereas barrier 2 must be an insulator in order to maintain electrical isolation between metal lines (Figs. 8 and 9).

Third, when forming the vias in an ILD layer, it is important that the metal surface area at the bottom of the via can be cleaned properly so that eventually good electrical contact can be achieved between the upper and lower metal levels. Initially this requires that all vias are cleared in the course of the etching and no ILD is left in any of them. In order to insure complete via clearing everywhere, a certain amount of overetch is generally applied. This, in turn, tends to deposit polymeric residue, possibly containing metal, at the bottoms of some of the vias. Removal of this residue in cleaning the vias is often not a trivial task.

### COPPER DEPOSITION

#### 3.1 OVERVIEW

For the deposition and processing of copper films one may distinguish the following general requirements:

- (1) It must be possible to deposit high-purity films for the lowest possible resistivity  $\rho$ . In addition, it will be desirable to be able to control the texture of the Cu films, since this is a determining factor for the electromigration resistance of the material.

- (2) The deposition method chosen must allow for high deposition rates for adequate throughput.

- (3) A chemical-mechanical polishing technique has to be developed that makes it feasible to planarize Cu and its associated barrier layer.

- (4) Given that Cu will be used in conjunction with the damascene method for patterning, the deposition method must be able to completely fill trenches and vias with high aspect ratios.

- (5) Since the use of Cu necessitates a diffusion barrier, it will be desirable to perform the metal/barrier depositions in an integrated cluster tool, so that the sample does not have to be exposed to the atmosphere between the two depositions.

- (6) It must be possible to maintain a low-cost, high-reliability process for low cost of ownership.

In the next two sections we will describe various chemical and physical methods for the deposition of Cu. This will be followed by a section on approaches to the patterning of Cu, both subtractive and damascene.

#### 3.2 CHEMICAL DEPOSITION METHODS FOR COPPER

This section deals with the two major chemical methods for depositing Cu films. These are chemical vapor deposition (CVD) and electrochemical plating (ECP). (For information on electroless plating, a third chemical method, the reader is referred to Ref. [19]. This method appears to be of less practical importance at the present time.) Since the CVD method generally involves organometallic precursor species, it is sometimes referred to as MOCVD. We use the term "chemical

method" in the sense that chemical reactions of molecular precursor species containing Cu atoms are an essential part of the deposition process.

#### 3.2.1 Chemical vapor deposition (CVD)

The principle underlying any CVD method is the heterogeneous decomposition of a gaseous precursor, such that the desired atomic species are deposited on the substrate and the by-products remaining from the precursor molecules are carried away in the gas phase. The Cu films so formed must, of course, satisfy the requirements outlined above. This points immediately to two main issues in Cu CVD: (1) the availability of suitable precursor species, which means precursor species with adequate volatility, and (2) the purity (hence the electrical resistivity) of the deposited films, which may be limited by incorporation of by-products from the deposition reaction. In addition, the temperature required for Cu CVD may restrict the type of ILD that can be used in conjunction with the CVD process. On the other hand, one can anticipate that Cu CVD will give excellent results in regard to via filling, since it tends to form highly conformal deposits, as is common for CVD methods in the surface-reaction controlled regime.

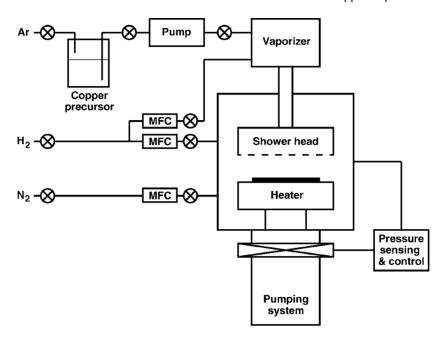

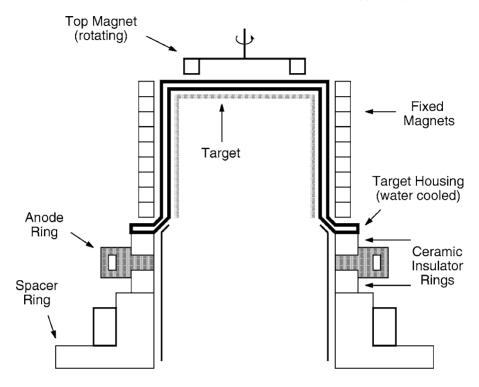

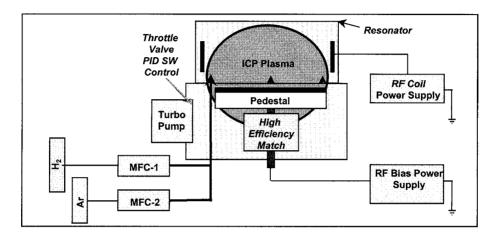

A typical set-up for Cu CVD is displayed schematically in Fig. 10.<sup>21</sup> The reactor of Fig. 10 shows the usual gas introduction and pumping facilities. The Cucontaining species from the liquid precursor are carried into the chamber with the help of a carrier gas. The showerhead serves to direct a uniform flux of reactants over the wafer surface. Hydrogen represents an additional gas that may be made to react with the copper precursor to facilitate the deposition process. The reactor in Fig. 10 is a cold-wall reactor, in that only the substrate is heated. Alternatively, in a hot-wall reactor the entire chamber is heated. The major drawback of a hot-wall reactor is that unwanted Cu deposition may occur on the chamber walls.

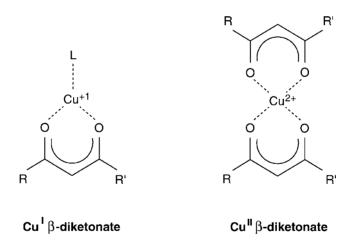

In general, precursors are metallorganic Cu compounds, the most favored being ligand-stabilized Cu<sup>I</sup> and Cu<sup>II</sup>  $\beta$ -diketonates. Cu<sup>I</sup> compounds are usually liquid and Cu<sup>II</sup> solid at room temperature. The vapor pressures of both these types of compounds are such that adequate volatility can be achieved at reasonable temperatures. Solid precursors present somewhat more difficulties in maintaining controlled evaporation and consistent delivery to the substrate. Therefore, dissolution of the solid precursor in a solvent, followed by transport of the solvent into the reactor, has also been explored. Generalized examples of Cu<sup>II</sup> and Cu<sup>II</sup>  $\beta$ -diketonate precursors are shown in Fig. 11.

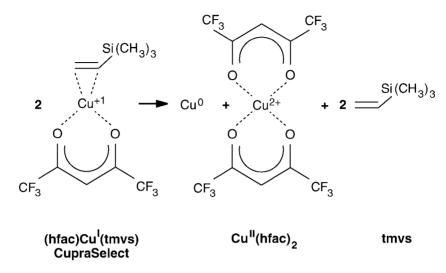

The most common class of compounds involves  $R = R' = CF_3$ . In this case the diketonate is abbreviated as hfac (hexafluoroacetylacetonate), and the precursors are called  $Cu^{II}(hfac)_2$  and  $(hfac)Cu^I(L)$ . A commercially available variety is CupraSelect,<sup>22</sup> which can be represented as  $(hfac)Cu^I(tmvs)$  where tmvs stands for trimethylvinylsilane (Fig. 12). It is worth noting that the volatility of these

Figure 10 Cu chemical vapor deposition (CVD): schematic experimental setup.

Figure 11 Examples of Cu<sup>II</sup> and Cu<sup>II</sup> precursors for Cu CVD.

compounds can be varied systematically by changing the size and the nature of the ligands R, R', and L. The temperature stability also depends on the nature of the ligands. The suitability of many different compounds, obtained by substituting different ligands, has been investigated as precursors for Cu deposition.  $^{23-27}$

Figure 12 (hfac)Cu(tmvs) precursor and corresponding disproportionation reaction for CVD of Cu.

The two types of precursors produce Cu films through two different types of reactions. Deposition from Cu<sup>I</sup> compounds occurs by a surface disproportionation reaction:

$$2(\text{hfac})\text{Cu}^{\text{I}}(\text{L}) \rightarrow \text{Cu}^{0}(\text{s}) + \text{Cu}^{\text{II}}(\text{hfac})_{2} + 2\text{L}. \tag{13}$$

Note that one of the reaction products is a volatile Cu<sup>II</sup> precursor, which implies that the yield of the reaction in Eq. (13) can be at best 50%. It has been argued recently that loss of the ligand L occurs to a significant extent in the gas phase and that the active precursor is really (hfac)Cu<sup>I</sup>. <sup>28</sup> Deposition from Cu<sup>II</sup> compounds involves reduction by hydrogen:

$$Cu^{II}(hfac)_2 + H_2 \rightarrow Cu^0(s) + (COR)CH(COR'). \tag{14}$$

Various approaches have been explored to make the reactions described in Eqs. (13) and (14) more reliable and efficient, e.g., using chemical additives or a plasma enhancement. In the deposition from (hfac)Cu<sup>I</sup>(tmvs), the dissolution of the precursor in (tmvs), followed by direct liquid injection into the reaction chamber, mitigates premature disproportionation in the delivery system and gives a more stable delivery rate to the reactor.<sup>22,29</sup> Moreover, the addition of Hhfac ligand vapor into the reactor during deposition increases the deposition rate and improves film uniformity and smoothness.<sup>22,29</sup> The addition of water, either directly<sup>30,31</sup> or in the form of Hhfac-dihydride (Hhfac:2H<sub>2</sub>O) also tends to increase the deposition

rate. Blends of CupraSelect with tmvs and Hhfac:2H<sub>2</sub>O are available commercially (e.g., 2504, with 2.5% tmvs and 0.4% Hhfac:2H<sub>2</sub>O).

Introducing excitation of the reactants by a plasma has also been examined. The primary benefit of this process in the Cu<sup>II</sup> reaction [Eq. (14)] is to provide a supply of free H atoms, and thus to increase the deposition rate, <sup>21,32</sup> since the thermal dissociation of H<sub>2</sub> at typical Cu deposition conditions is small and the reaction of H<sub>2</sub> with Cu<sup>II</sup>(hfac)<sub>2</sub> is rather slow.<sup>33</sup> H atoms may also aid the Cu<sup>II</sup> reaction [Eq. (13)] by yielding additional Cu from the secondary reaction of H with the primary reaction product Cu<sup>II</sup>(hfac)<sub>2</sub>. A potential side effect of too high a level of plasma excitation is the generation of fragments of the metallorganic precursor species, which may lead to the incorporation of undesirable impurities into the Cu film.<sup>21</sup>

For blanket Cu CVD films, fairly high deposition rates of the order of several hundred nm/min have been achieved. Because of the chemical nature of the process, precursor molecules impinge onto the substrate from all different directions. Therefore, the CVD of Cu in principal can be highly conformal. This requires, however, that the sticking coefficient of the precursor is small so that the reaction does not take place preferentially at the top of a feature. Alternatively, one may say that an adsorbed precursor molecule should have a large probability for re-emission. In addition, a large surface diffusion coefficient for adsorbed precursors is desirable. Experience has shown that in order to completely fill features with aggressive aspect ratios, the experimental conditions often have to be chosen such that the overall deposition rate is reduced considerably. Yet a process deemed manufacturable, giving a deposition rate of over 200 nm/min and capable of filling 0.3- $\mu$ m vias with 2.7 aspect ratio, has been reported. Further details and results regarding feature-scale deposition will be discussed in Sec. 7.4.

In the early stages of the development of copper technology, extensive efforts were being made to devise a method for selective CVD of copper.<sup>21</sup> The goal was to deposit Cu only onto metallic surfaces, not onto SiO<sub>2</sub>, in order to be able to fill contact vias and trenches selectively and thus to reduce or even eliminate the use of chemical-mechanical polishing. For the Cu<sup>I</sup> chemistry, the disproportionation reaction [Eq. (13)] requires transfer of an electron and was thought to be facilitated by a metal surface. The Cu<sup>II</sup> reaction was believed to depend on dissociatively adsorbed hydrogen, which again would be greatly favored to occur on metals rather than on SiO<sub>2</sub>. However, with these mechanisms in mind, a major difficulty is apparent immediately; any metal contamination on the SiO<sub>2</sub> surface will contravene the selective Cu deposition. Furthermore, SiO<sub>2</sub> surfaces are typically terminated with hydroxyl groups, which are primary sites for the adsorption of Cu precursors.<sup>35</sup> These sites can be passivated, and thus Cu nucleation can be suppressed, by reaction with suitable silylating agents.<sup>31,36</sup> Presently, selective copper deposition has not seen significant application in production because

of the successful development of the cheaper alternative of copper electroplating in combination with chemical-mechanical polishing. Moreover, it appears that Cu deposition by electroplating can lead to films with larger grains, thus alleviating electromigration concerns.

#### 3.2.2 Electrochemical plating (ECP)

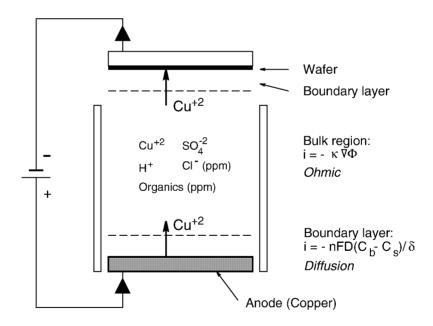

In the electrochemical plating of Cu, the reactants are provided as Cu<sup>+2</sup> ions in solution, the substrate takes the role of the cathode in an electrochemical cell, and deposition occurs by the reduction of Cu<sup>+2</sup> ions at the cathode. A corresponding oxidation reaction at the anode puts Cu<sup>+2</sup> ions in solution and balances the electric current flow driven by the external power supply. A schematic view of an ECP reaction cell is given in Fig. 13.

If the applied potential is reversed, cathode and anode are reversed, and so are the locations where Cu deposition and dissolution occur. Alternating between deposition and dissolution, a process known as pulse plating, may be useful in order to improve the filling capability of a plated film.

The most common chemistry for the Cu ECP bath is based on CuSO<sub>4</sub> in H<sub>2</sub>SO<sub>4</sub>,<sup>37,38</sup> but other acidic baths are being investigated as well.<sup>39</sup> Alkaline baths

Figure 13 Schematic of electrochemical plating (ECP) cell for Cu deposition.

are also under development.<sup>40,41</sup> In commercial processes, proprietary organic additives to the plating solution are used in order to improve the filling of features.

ECP requires a closed loop for continuous electric current. Therefore, one cannot plate directly onto an insulator, such as  $SiO_2$ . In that case, an electrically conducting contact layer must be deposited first. This may be the eventual barrier layer, although thin barriers may have too high an electrical resistance. Otherwise a thin seed layer of Cu itself may be deposited, e.g., by CVD or by PVD. This initial conducting layer not only enables the plating to begin, but it also has a strong influence on the details of how the plated film nucleates and grows.

The ECP cell can be divided into three regions: two boundary layers near the electrodes, and a bulk region in between (Fig. 13). In the boundary layers, ion transport is governed by diffusion under the influence of a concentration gradient, whereas in the bulk region transport is essentially ohmic under the influence of the electric field. Ordinarily, conversion of Cu<sup>+2</sup> ions to plated Cu atoms occurs with near 100% efficiency, so that the electric current density is a direct measure of the plating rate. Plating uniformity across a wafer is determined by ohmic effects, primarily by the current distribution.

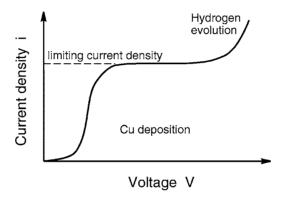

The plating current density i is a function of the applied voltage V. A typical curve is shown in Fig. 14. When  $\log(i)$  is plotted vs V, the resulting graph is referred to as a Tafel plot.<sup>42</sup> Three regions can be distinguished in the curve of Fig. 14. The region at low voltage, where i increases with V is the region used for ECP. At somewhat higher voltages, the current density reaches a limiting value, and at the highest voltages hydrogen evolution sets in. The potential, as the driving force behind the electrochemical reaction, governs the overall film deposition and morphology, and in particular determines the relative rates of film nucleation and growth.<sup>37</sup> The limiting current is a function of the mass transport in the system.

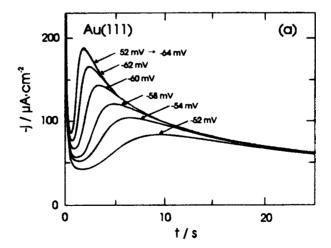

Important information regarding the nucleation and growth in ECP can be obtained from so-called chronoamperometry plots, in which a step function potential is applied to one of the electrodes and the resulting current is recorded against time. An example of such a plot is shown in Fig. 15 for the deposition of Cu onto Au(111) using a  $K_2SO_4/CuSO_4$  plating bath at a fixed pH =  $4.^{38}$  After a brief initial delay to charge the double layer, the form of the current vs. time is determined by the competition between the formation of new nuclei and the growth of nuclei already formed. In a large number of systems, the overall process is controlled by mass transfer, which creates a growing ion-depleted diffusion zone around each nucleus, thus limiting both the formation of new nuclei and the further growth of nuclei present already. Note that the current I reaches a maximum  $I_m$  at a time  $t_m$ , depending on the applied potential (Fig. 15). Similar behavior is observed for a fixed potential step and variable pH of the plating solution.<sup>38</sup>

As long as diffusion zones do not overlap, nucleation normally follows a first-order rate law:

$$N = N_0[1 - \exp(-At)], \tag{15}$$

where  $N_0$  is the number of nucleation sites and A is the nucleation rate constant. Depending on the relative importance of the two reaction steps, two special cases can be distinguished.<sup>37,43</sup>

Figure 14 Typical current vs. voltage characteristic for ECP of Cu.

**Figure 15** Typical ECP current vs. time, I(t).<sup>38</sup>

- (1) Instantaneous nucleation:  $At \gg 1$ , and thus  $N = N_0$ . Essentially all nuclei are formed at the very beginning of the process in terms of the time scale of the experiment.

- (2) Progressive nucleation:  $At \ll 1$ , and thus  $N = N_0 At \ll N_0$ . Nuclei form continuously, and the number of nuclei initially increases as a linear function of time.

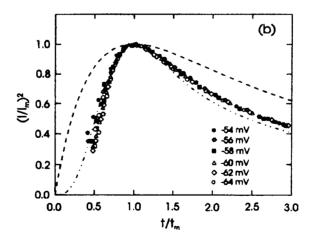

The growth phase depends on the shape of the diffusion zone and the growth morphology. The case of 3D hemispherical diffusion-controlled growth has been treated and modeled in detail. 43,44 Again, as long as the diffusion zones do not overlap, for instantaneous nucleation the current density is proportional to  $t^{1/2}$ , and for progressive nucleation the current density is proportional to  $t^{3/2}$ . Overlapping diffusion zones can be corrected for.<sup>43</sup> An example for Cu deposition on Au(111) is given in Fig. 16,<sup>38</sup> where the data from Fig. 15 for  $(I/I_m)^2$  are plotted against  $t/t_m$  and compared to model predictions. Note that in terms of these dimensionless variables, the curve for progressive nucleation and growth is more peaked than the curve for instantaneous nucleation and growth. Hence one may conclude that in the example given the prevailing mechanism for Cu deposition is progressive nucleation. On the other hand, for a fixed potential step, the mechanism changes from progressive to instantaneous nucleation as the pH of the plating solution is decreased from 4 to 2. The mechanisms for ECP of Cu in microelectronic applications have not been characterized yet in great detail. However, there is one report of Cu deposition on TiN/n-Si(100) in an H<sub>3</sub>BO<sub>3</sub>/HBF<sub>4</sub> plating bath at pH = 1.4, which follows instantaneous nucleation and growth.<sup>39</sup>

**Figure 16** Typical plot of dimensionless plating current  $(I/I_m)^2$  vs. dimensionless time  $t/t_m$ .<sup>38</sup>

In the previous arguments, issues of mass transfer limitations, nucleation, and growth were connected with Cu deposition onto an initially planar substrate. In damascene technology, however, a key problem is deposition into submicron vias and trenches, and specifically filling completely such features with metal. In that case, additional aspects of mass transfer, diffusion, and uniformity come into play due to the length scale of the features. These issues will be elaborated on in more detail in Sec. 7.4.

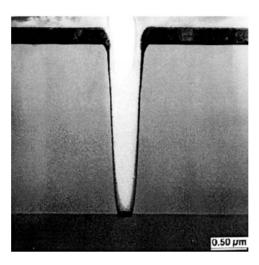

#### 3.3 PHYSICAL DEPOSITION METHODS FOR COPPER

Physical deposition methods are characterized by the property that Cu atoms themselves are the "precursor" species rather than molecules containing Cu atoms as in CVD. The traditional physical methods have been evaporation and sputter deposition (Fig. 17). Compared to CVD, a key difference is that Cu atoms, and metal atoms in general, are not really volatile. Instead, they are highly reactive and have a very high sticking coefficient on most any substrate. This points immediately to the filling of high-aspect-ratio features in the ILD as the major issue with physical deposition methods. Due to line-of-sight conditions and high atomic reactivity (i.e., essentially unity sticking coefficient), Cu atoms will tend to deposit preferentially near the top of a feature, where their flux is highest, leading to quick closure of the feature at the top and a keyhole below (Fig. 18, [54]) (see also<sup>45</sup>). Therefore, the features do not get filled completely, and the void inside the metal constitutes a reliability risk.

In sputter deposition for Al technology, this drawback can largely be overcome by increasing the substrate temperature, thus increasing the surface mobility of the deposited Al atoms. Features with modest aspect ratios can be filled using this method. But the same method cannot be carried over to the deposition of Cu, since this would require too high a substrate temperature. Another way by which the via-filling problem can be mitigated somewhat in sputter deposition is to apply re-sputtering to the substrate. When the substrate is made into the cathode and is being sputtered itself, metal is removed preferentially from the top areas of the features, where there was extra deposition, and is redistributed generally inside the feature. By alternating between sputter deposition and re-sputtering, the filling of features can be improved.

With Cu, two other approaches have been shown to be feasible (Fig. 17). These rely on the Cu atoms being highly directional, impinging on the substrate primarily along the normal direction. One type of implementation of this principle has been realized in collimated or long-throw sputter deposition. Here features are filled with metal from the bottom up, as the deposition rate on the vertical sidewalls is greatly decreased relative to the bottom, horizontal surface of a feature. The other type of implementation is represented by ionized physical vapor deposition

Figure 17 Experimental trends in physical vapor deposition (PVD) of metals.

(IPVD). This method again makes use of a form of re-sputtering, but in order to produce more conformal metal coverage and hence better via filling.

#### 3.3.1 Collimated and long-throw sputter deposition

In collimated sputter deposition, a mechanical type of grid between the sputtering target and the substrate filters out metal atoms moving in off-normal directions and lets pass through only atoms moving more or less along the substrate normal

direction. 46,47 As mentioned above, this reduces deposition onto the sidewalls of features and the formation of overhangs at the top edges of features. The problem with the method is that it also reduces the overall deposition rate considerably, thus making the process rather slow. In addition, an unavoidable side effect of the filter action is deposition of atoms onto the filter itself. Therefore the transmission of the filter, and with it the deposition rate, decreases in the course of time.

In long-throw sputter deposition, <sup>47–49</sup> the effect of directionality is achieved by placing the sputtering target at a much larger distance from the wafer than in normal sputter deposition. This reduces the spread of incident angles of the atoms by reducing the effective size of the sputtering source, but in order to work as desired, the process must be maintained at a low enough pressure so that the metal atoms do not undergo any collisions on the way from the sputtering target to the substrate. The end effect, once again, is a reduced overall deposition rate.

The results of both collimated and long-throw sputter deposition can be interpreted in common terms, in the sense that they reduce the practical effective size of the source. Simulations have exemplified the effects of the feature aspect ratio and the target aspect ratio (source-to-substrate distance/source diameter) on via filling. <sup>50</sup>

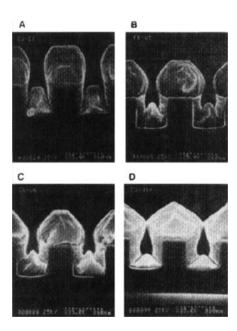

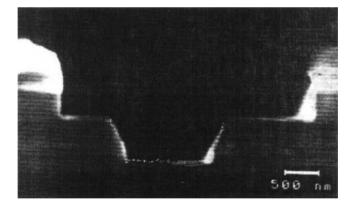

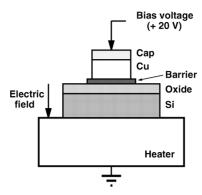

**Figure 18** Formation of keyhole in metal when deposition is not conformal.<sup>54</sup> IPVD of Cu onto patterned SiO<sub>2</sub> (magnetron sputter deposition with post-ionization: magnetron power = 300 W, RF power = 1 keV, Ar pressure = 30 mTorr, deposition time = 24 min). Sample DC bias: a) -5 V, b) -20 V, c) -30 V, d) -50 V.

## 3.3.2 Ionized physical vapor deposition (IPVD)

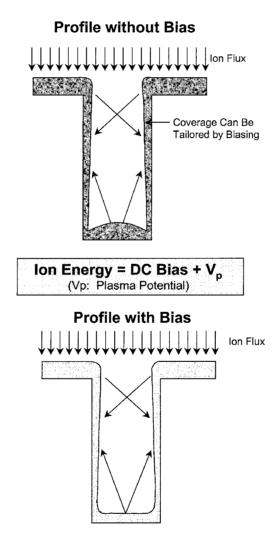

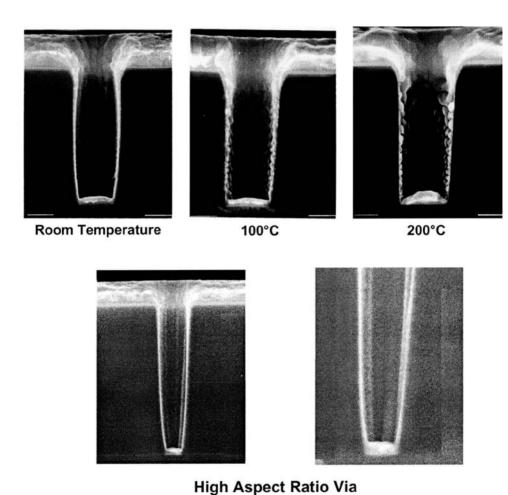

In all variations of IPVD, the depositing species are not only directional but also carry extra kinetic energy beyond the normal thermal energy. This means that the approach combines aspects of species directionality and continuous re-sputtering, with the result that metal deposition into features is much more conformal, and via filling is improved greatly. This principle is illustrated in Fig. 19.

**Figure 19** Metal deposition without and with wafer bias in ionized physical vapor deposition (IPVD).

**Figure 20** Experimental setup for magnetron sputter deposition with RF post-ionization. <sup>54</sup>

The earliest form of IPVD was termed partially ionized beam deposition (PIB). This involved thermal evaporation of metal atoms, followed by electron impact ionization of a small fraction of the evaporated species. A potential bias of the order of 1 kV was applied between the source and the substrate, serving to impart directionality as well as substantial kinetic energy to the metal ions. This extra energy—a small fraction of the metal flux arriving at the substrate, was enough to prevent preferential deposition at the top of features and to allow successful filling of fairly high-aspect-ratio vias.

More recently, post-ionization of evaporated Cu atoms was achieved using an electron cyclotron resonance (ECR) discharge.<sup>53</sup> In this case, a large fraction of evaporated atoms ended up being ionized, so that in essence a Cu vapor plasma was being maintained. The potential bias between source and substrate was of the order of 50 V. Again, the net effect of the ionized metal flux to the substrate was much better via filling compared to conventional evaporation.

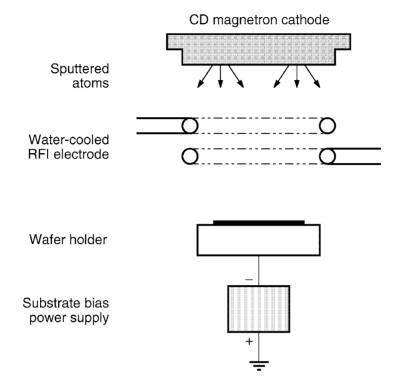

The most promising varieties of IPVD, at present, appear to be based on variations of magnetron sputter deposition which include some form of post-ionization.

**Figure 21** Experimental setup for hollow-cathode magnetron sputter deposition, redrawn schematically from [270].

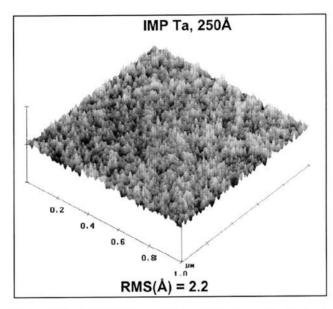

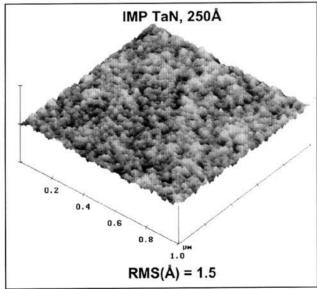

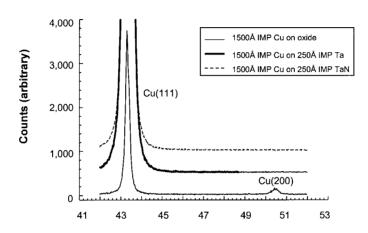

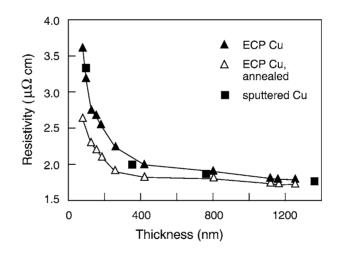

The metal flux is generated from a magnetron target, and ionization of a fraction of these metal atoms is effected either by additional rf excitation<sup>54–56,262</sup> or by a special design of the magnetron source (e.g., a hollow-cathode magnetron).<sup>57,58</sup> The former situation has also been referred to as ion metal plasma (IMP) deposition, which has been developed and commercialized for a number of different applications.<sup>263</sup> An rf ionization setup is illustrated in Fig. 20 and a hollow-cathode magnetron setup in Fig. 21.

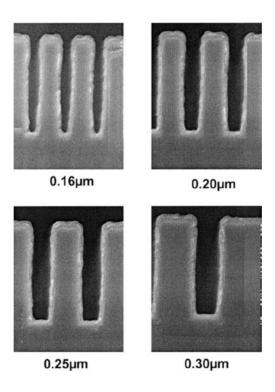

An example of results for Cu deposition with an rf ionization setup is given in Fig. 22.<sup>54</sup> Here the experimental conditions are chosen such that deposition at the bottoms of features is favored over deposition at the sidewalls. The extent to which this occurs depends on the gas pressure and the Cu ion energy at the substrate. The latter, in turn, is a function of the plasma potential and the substrate bias (see Fig. 19). Note that there is no overhang of Cu at the top, so that the features are filled very well. The main question with regard to IPVD of Cu is under what conditions and up to what aspect ratio features can be filled properly.

**Figure 22** IPVD of Cu onto patterned  $SiO_2$  (magnetron sputter deposition with post-ionization: magnetron power = 300 W, RF power = 1 keV, Ar pressure = 45 mTorr, sample DC bias = -12 V). Scanning electron micrographs show time evolution of deposited film.

IPVD under conditions favoring conformal deposition has also been used successfully to deposit thin barrier layers.<sup>57–59</sup> This may well turn out to be one of the most important application of IPVD in practice (see Chapter 7 for additional information on this point).

# COPPER PATTERNING

## 4.1 OVERVIEW

As we outlined in Sec. 3, there are two basic approaches to patterning for the purpose of creating multilevel interconnect structures. To put it in the simplest terms: The traditional, subtractive approach consists of patterning the metal by dry etching, filling the gaps in the metal pattern with ILD, and planarizing the ILD. The new damascene approach consists of patterning the ILD by dry etching, filling the features in the ILD with metal, and planarizing the metal by chemical-mechanical polishing (CMP). In this section, we will describe both approaches as they apply to Cu interconnect technology. The damascene approach is in the process of being adopted for mainstream applications with  $SiO_2$  as the ILD, but new developments continue to be made with the subtractive approach.

#### 4.2 SUBTRACTIVE COPPER PATTERNING

Here the key step is the fine-line patterning of Cu by anisotropic dry etching in a plasma, although some patterning of the ILD is involved as well. The dry etching of the Cu should be done to able to be done under conditions that are compatible with other processes and the materials present on the wafer. This presents unique difficulties with Cu, in contrast to Al. The major one of these difficulties is that common plasma chemistries yield reaction products with only marginal volatility. This fact can be appreciated by comparing the vapor pressures of potential etch products from typical halogen plasma chemistries. The following are estimates, based upon thermodynamic data, <sup>60</sup> for chlorinated products at room temperature:

| Metal    | Product                                                            | Vapor Pressure                                 |

|----------|--------------------------------------------------------------------|------------------------------------------------|

| Al<br>Cu | Al <sub>2</sub> Cl <sub>6</sub><br>Cu <sub>3</sub> Cl <sub>3</sub> | 10 <sup>-4</sup> Torr<br>10 <sup>-8</sup> Torr |

|          | CuCl                                                               | ~0                                             |

Products with other halogens tend to have lower vapor pressures yet. This implies that Cu plasma etching will require an elevated substrate temperature.

It should be noted that nonhalogen-based chemistries similar to those employed in CVD of Cu have been shown to form volatile Cu products at much

lower temperatures.<sup>61,62</sup> However, a dry etch process must not only yield volatile products at a useful rate, but it must allow, at the same time, for highly accurate pattern transfer. The non-halogen chemistries, relying on thermal processes, produce isotropic etching with rather poor pattern definition. On the other hand, sub-micron patterning requires highly anisotropic etching, which occurs only in the presence of ion bombardment of the substrate.<sup>63</sup> None of these chemistries have been implemented under those types of conditions.

The second difficulty with the subtractive patterning of Cu, which is a consequence of the high substrate temperature, relates to the masking technology used in the microlithography. Halogen plasmas present a rather aggressive environment at the substrate temperatures necessary, and normal photoresists are generally not stable enough under these conditions, so that nontraditional approaches to masking need to be sought.

Yet another issue following from the use of a halogen chemistry, and aggravated by high substrate temperature, is the potential corrosion of exposed metal by reaction by-products which were removed incompletely.

## 4.2.1 Reactive ion etching of copper

Reactive ion etching (RIE) refers to a reactor geometry in which the etching plasma is maintained as a parallel-plate, capacitively coupled rf discharge. The substrate is placed on the rf-driven electrode, which develops an induced dc bias potential and thus acts as the cathode. Hence the substrate is subject to bombardment by energetic ions from the plasma.<sup>63</sup>

It was realized early on that useful etch rates for Cu require a substrate temperature of about  $200^{\circ}\text{C}$ . At lower temperatures, no etching occurs but rather a layer of Cu-chloride grows on top of the Cu film. Schaible and Schwartz were able to obtain etch rates up to 500 nm/min in a  $\text{CCl}_4/\text{Ar}$  plasma. Ashing of photoresist exposed to the etching plasma resulted in the formation of a thick black layer on the surface of the Cu. Therefore MgO was chosen as a hard mask. Etching was highly anisotropic under these conditions. With  $\text{SiO}_2$  as a hard mask, etch by-products tended to attack the copper.

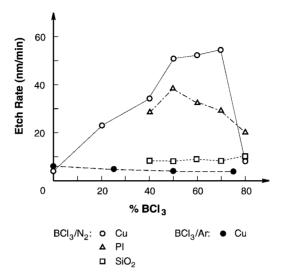

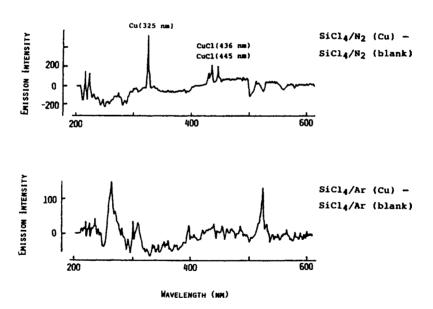

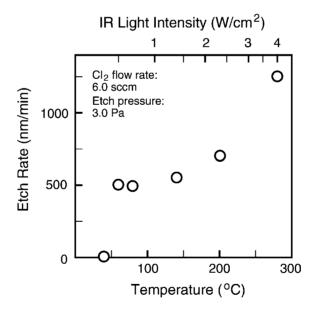

Later studies using  $BCl_3$ -based plasmas provided further details regarding the temperature dependence of the Cu etch rate and the etch mechanism in general. The etch rate increases rapidly with the temperature at around  $200^{\circ}C$  but then levels off. This indicates that at higher temperatures the etch rate is limited by the supply of reactants, presumably Cl atoms, which depends strongly on the gas composition (Fig. 23). The addition of  $N_2$  to  $BCl_3$  is particularly effective in increasing the etch rate, in contrast to the addition of Ar. Optical emission spectroscopy confirms that the role of the  $N_2$  is to enhance the production of Cl atoms in the plasma. Although the etch selectivity of Cu relative to polymers is not

**Figure 23** Etch rates in reactive ion etching (RIE) of Cu RIE vs. gas composition: pressure = 50 mTorr, DC bias = -300 V, wafer temperature = 250°C.  $^{66}$

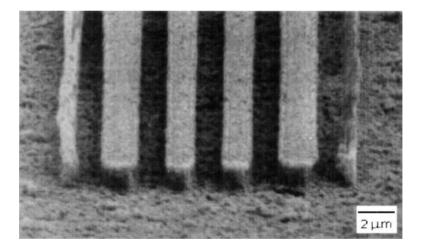

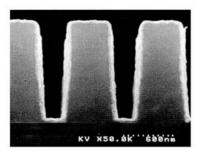

**Figure 24** Pattern definition in Cu RIE using polyimide mask: flow rate ratio  $BCl_3/N_2 = 50/50$ , p = 50 mTorr, DC bias = -300 V, wafer temperature  $= 250^{\circ}$ C. Note the two narrow lines on both sides with a width of about 0.4  $\mu$ m.

very large, sub-halfmicron anisotropic patterning can be achieved with a polymide mask that holds up well enough under exposure to the plasma at the elevated temperature (Fig. 24).

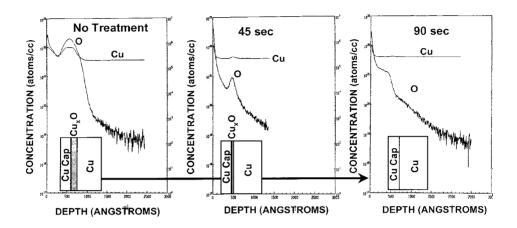

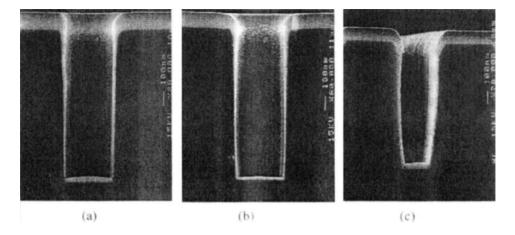

## 4.2.2 Etching of copper in high-density plasmas (MIE, ECR, ICP)

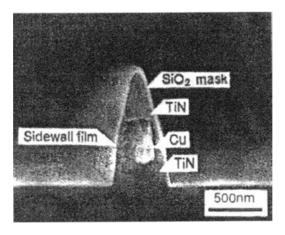

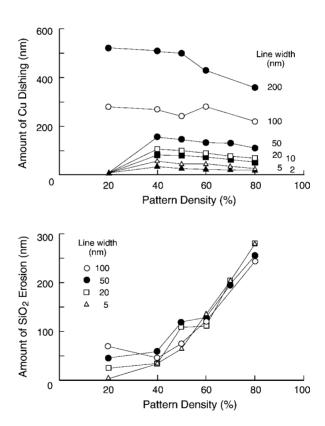

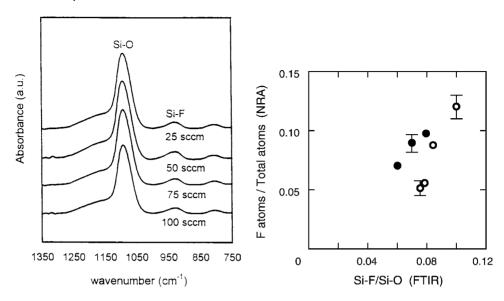

Even under optimum conditions, the etch rates attainable in RIE are rather low, typically less than 100 nm/min. Such rates are too small for economical single-wafer processing. The low etch rates can be attributed to correspondingly low plasma densities, i.e., low concentrations of ions and reactive neutral etchants. Various attempts have been made to obtain increased etch rates by using higher-density plasmas.