半导体学报2020年第6期——中文导读 [2020-06-29] |

| 综述文章 1. 半导体材料之表面能与边缘能计算综述 近年来,化合物半导体,包括III-V族和II-VI族半导体薄膜,获得了广泛的关注。然而,有限的晶体质量成为凝聚态物理研究和器件工业生产上面临的严重瓶颈。不论是薄膜还是纳米团簇半导体,系统性的调控其生长形貌,理解其在生长过程中的基本热力学和动力学性质都是提高晶体质量的关键。作为生长形貌的基本参数的表面形成能正是通向解决这些困难问题的钥匙。

对于薄膜和二维材料来说,生长过程中的平衡形貌的稳定性研究比体材料要复杂和困难很多,这是因为薄膜和纳米团簇具备复杂的表面取向,而这类表面形成能正是吉布斯在早期著作中提到所谓过剩吉布斯自由能的重要组成部分。然而,极性半导体表面和边缘形成能的研究直到二十一世纪初才初露曙光,直到近年才产生了相当精确和稳定的算法。这些算法文章散见于不同学术期刊,学术界也一直缺乏对这类算法的综合性比较和讨论。这也相当程度的抑制了对半导体材料形貌稳定性分析精度的提高,并且影响了学者对理论预测精度的信心。本文中香港中文大学朱骏宜教授等回顾了过去二十几年时间内,前人及本团队发表的一系列表面能和边缘能的算法,探讨了这些算法的得失,并对未来的发展做了一些展望。

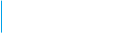

产生半导体表面的过程可以类比于用刀切开一块蛋糕。对于极性半导体来说,由于极性表面和边缘的不对称性,如图1(a)所示,尽管上下两边的形成能之和,也就是挥动这把刀所需要的总能量,很容易得到;然而,某一个单极性面的形成能却很难计算。这通常需要通过间接的模型构造和局部电子环境转化的办法来估算。

图1. (a) 示意性的切开氮化硼极性边缘;(b) 单边被氢原子钝化的准一维氮化硼带;(c) 三边被氢原子钝化的正三角形纳米氮化硼团簇。

早期的模型通常只适用于计算相对表面能或边缘能,它们以一个较易计算的对称性表面形成能作为参考点,来计算其他表面的相对形成能。然后,基于这些表面能,可以通过计算伍尔夫构型(Wulff construction),来估计晶体的平衡形貌。由于伍尔夫构型和不同表面的形成能比例有关,因此,早先的绝对表面能的系统误差在平衡形貌的估算当中会被严重放大,导致早先的平衡形貌的理论研究与实验结果严重不符。这一问题,直到近年基于表面饱和原子的赝化学势的正确算法被提出才真正获得解决。在图1中,我们以氮化硼为例,简述了一下这个算法。要获得单一极性边的形成能,需要先获得其共轭边(图1(b))的饱和元素的赝化学势。而这一化学势可以通过构造三边对称的正三角形(二维情况),如图1(c),或者是四面对称的正四面体(三维情况)来获得。这类算法大大提高了自洽性,使得平衡生长形貌的正确预测变得可能。

另外,对于复杂的三维纳米晶体,本文也做了一番综述和预测。基于现有的对半极性面和极性面估算的良好算法,结合正确的生长热力学分析,理论预测的正确性也正等待最后的临门一脚。这类基础理论方面的突破也必将会对晶体生长调控和工业制造的进步产生良好影响。

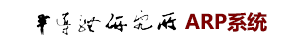

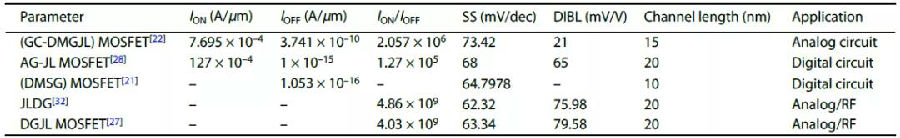

最后,尽管在不同学者的努力下,计算表面能或边缘能的模型已有很大程度的改良,准确率亦不断提高,但这些方法未必适用于较复杂的晶体结构或者复杂的生长环境,因为晶体的电子环境复杂度随着结构和生长条件的复杂度而上升。从算法来说,人为地对这些结构进行切割并计算,无可避免地创造了一些额外的系统性影响和误差,从而影响了计算的准确度。文中审视的过往研究虽不是万能模型,但仍为将来更多不同种类的半导体的表面能与边缘能计算提供了扎实的基础。从某种意义来说,对复杂系统生长的探索会是一个极具魅力和挑战性的永久课题。 A brief review of formation energies calculation of surfaces and edges in semiconductors Chuen-Keung Sin, Jingzhao Zhang, Kinfai Tse, Junyi Zhu J. Semicond. 2020, 41(6): 061101 doi: 10.1088/1674-4926/41/6/061101 2. 45 nm以下技术节点先进MOSFET的性能比较 CMOS技术因其可与集成电路集成,已经成为半导体工业中应用最广泛的技术之一。随着MOS晶体管的尺寸减小,其数量每两年就会增加一倍。但减小MOSFET的尺寸会缩短沟道长度并导致短沟道效应,同时会导致漏电流增加。为减少短沟道效应,人们采用了新的设计和技术。在放大器应用方面,双栅MOSFET的性能相对于单栅MOSFET有了改进。硅基MOSFET可以在恶劣环境下工作,已用于检测生物分子等多个领域。增加栅极数量可以增加晶体管的电流驱动能力,以GAA MOSFET为例,将其沟道的四面环绕四个栅极可以增加对器件沟道区域的栅极控制。此外,这种设计还增加了有效沟道宽度,改善了漏极电流并减少了漏电流,使短沟道效应维持在一定范围内。无结MOSFET随着导通电流的增大,其工作速度更快,功耗更低,从而可以获得良好的ION/IOFF比值。 在本文中,印度拉夫里科技大学Suman Lata Tripathi教授等分析并比较了45 nm以下技术节点下多种栅极和沟道设计的MOSFET结构,并比较了这些结构的亚阈性能参数即IOFF、亚阈斜率、DIBL值;分析了跨导、有效晶体管电容、稳定系数和临界频率等模拟/射频性能参数。另外,论文中还介绍了先进MOSFET结构在模拟/数字或IoT/生物医学等领域的应用。 表1. 不同MOSFET结构性能参数的比较  A review on performance comparison of advanced MOSFET structures below 45 nm technology node Namrata Mendiratta, Suman Lata Tripathi J. Semicond. 2020, 41(6): 061401 doi: 10.1088/1674-4926/41/6/061401 研究论文 1. 压应变AlGaN/GaN量子阱激光二极管的建模和光学响应  图1. QW能带示意图:导带(C)、重空穴带(HH)、轻空穴带(LH)和劈裂带(SO)。 Modelling and optical response of a compressive-strained AlGaN/GaN quantum well laser diode A. Menani, L. Dehimi, S. Dehimi, F. Pezzimenti J. Semicond. 2020, 41(6): 062301 doi: 10.1088/1674-4926/41/6/062301 2. 用于中波探测器的InAs/GaSbⅡ型超晶格中的应变诱导暗电流特性 II型超晶格(T2SL)材料是红外探测器的关键元素。但是基于T2SL层的探测器,生长过程中产生的应变对其性能有很大影响。为了有效控制应变效应并对应变引起的暗电流特性作出有效的分析和评价,人们已经开展了很多研究。

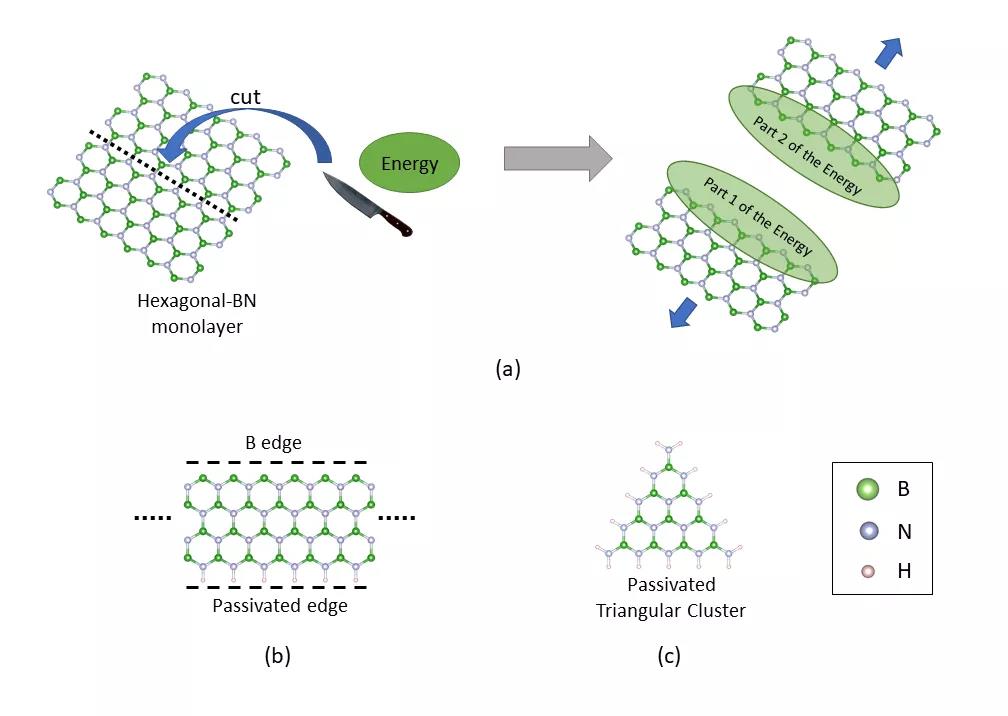

本文中,韩国忠南大学J. Nah教授等报道了InAs/GaSb T2SL中波红外光电探测器的应变诱导暗电流特性。通过高分辨X射线衍射(HRXRD)及在较高温度下(≥110 K)测得的吸收层的暗电流分析了InAs/GaSb T2SL层的整体应变,其中漏电流主要起因于吸收层中少数载流子寿命的降低。研究结果表明,当InAs/GaSb T2SL上的张应变被"类InSb"界面的压应变补偿时,少数载流子寿命增加,器件的暗电流密度减小。具体而言,张应变被补偿后的器件在120 K温度下的暗电流密度小于2×10-5 A/cm2,与没有张应变驰豫的器件相比,其暗电流密度降低了一个数量级以上。

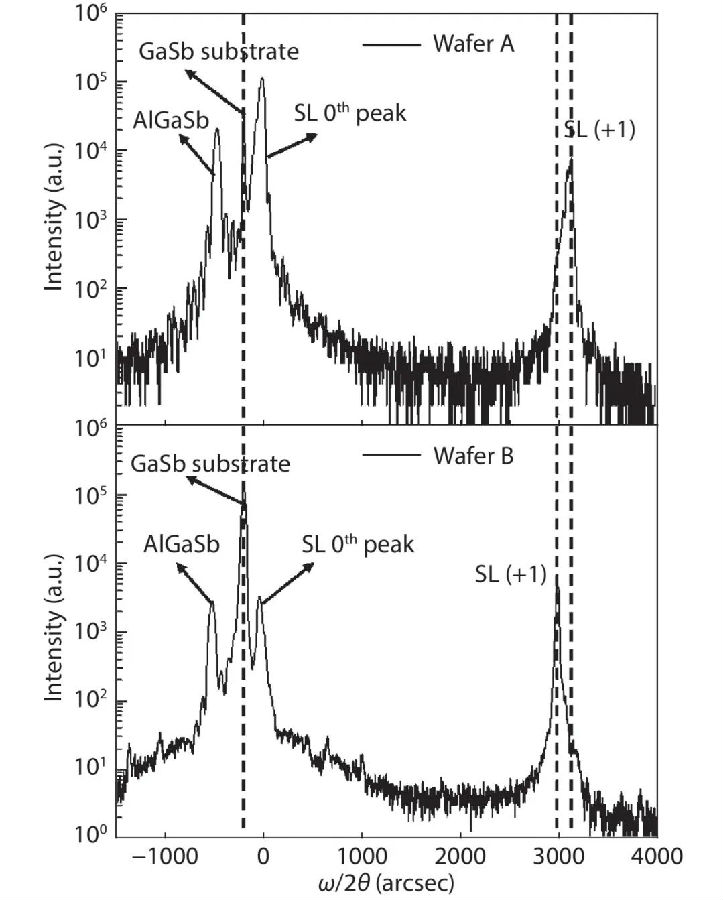

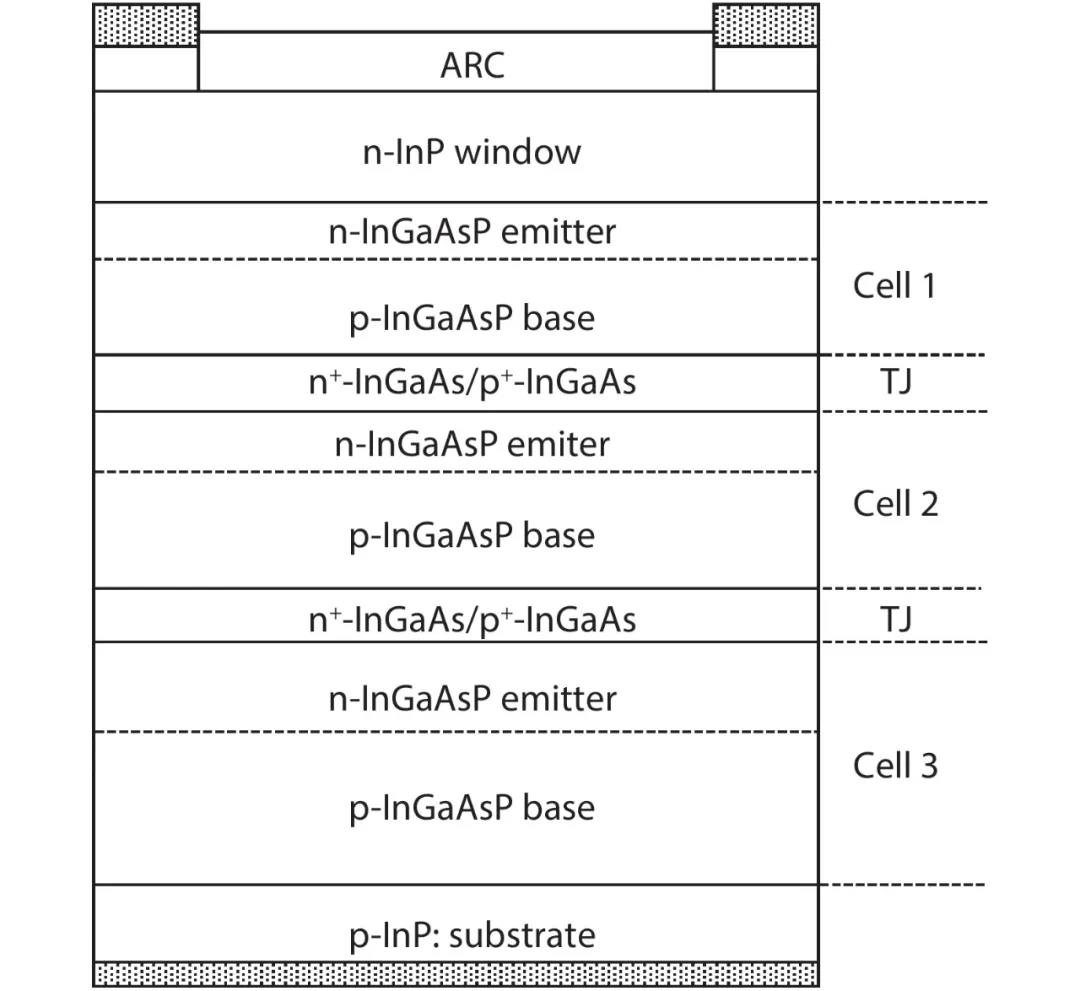

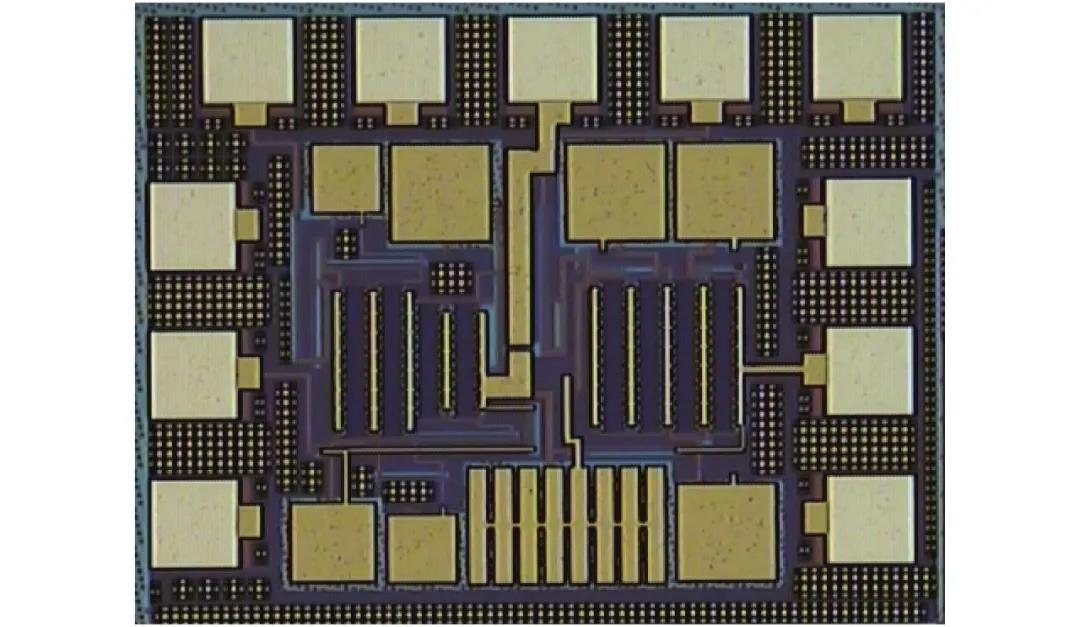

图4. InAs/GaSb T2SL和Al0.2Ga0.8Sb的高分辨率X射线扫描图。 H. J. Lee, S. Y. Ko, Y. H. Kim, J. Nah J. Semicond. 2020, 41(6): 062302 doi: 10.1088/1674-4926/41/6/062302 3. 1064nm InGaAsP多结激光功率转换器 中国科学院苏州纳米技术与纳米仿生研究所董建荣研究员等基于光伏电池器件物理,分析了多结电池的效率损失机理,设计了转换1064 nm激光能量的三结叠层InGaAsP/InP光伏电池。然后,通过材料制备和器件工艺研制了三结叠层InGaAsP/InP光伏电池。室温下的测试结果表明,三结InGaAsP电池在1.1 W/cm2 1064 nm激光照下的开路电压为2.16 V,转换效率达32.6%。  图1. 本文设计的三结InGaAsP-LPC的层结构示意图。 Jiajing Yin, Yurun Sun, Shuzhen Yu, Yongming Zhao, Rongwei Li, Jianrong Dong J. Semicond. 2020, 41(6): 062303 doi: 10.1088/1674-4926/41/6/062303 4. 一种0.1–1.5 GHz多倍频程双级四堆叠结构CMOS功率放大器 天津大学微波实验室研发团队设计并实现了一款工作在0.1–1.5 GHz 的CMOS超宽带功率放大器。近年来,由于电子装备正在向着小型化、高集成度、轻量化、多功能和低成本等方向发展,因此系统迫切需要射频收发机前端中功率放大器芯片具备宽带放大的功能。同时,高功率、宽带射频CMOS 功率放大器设计也具有较大的挑战性。首先,CMOS工艺的低击穿电压和高膝点电压等限制了功率放大器的功率输出能力;其次,宽带匹配电路本身就具有较大的设计难度。 基于上述的需求和亟待解决的问题,天津大学研发团队提出了采用双级四堆叠结构结合电阻匹配和反馈网络的设计方法,所实现的功率放大器体现了良好的宽带匹配、增益和增益平坦度等指标,并且芯片占用很小的芯片面积,大大节省了设计成本。 该设计表明了采用堆叠结构结合电阻反馈网络的方法是一种有望在很小的芯片面积内实现超宽带CMOS功率放大器的设计方案,对于拓展超宽带功放的设计思路与应用场景,具有积极的意义。  图5. 叠层PA的显微照片。 A 0.1–1.5 GHz multi-octave quadruple-stacked CMOS power amplifier Shizhe Wei, Haifeng Wu, Qian Lin, Mingzhe Zhang J. Semicond. 2020, 41(6): 062401 doi: 10.1088/1674-4926/41/6/062401 5. 一种高性能自适应连续导通谷电流模式DC–DC 降压变换器 随着社会发展和信息技术的不断进步,移动手机、便携式电脑、可穿戴设备等电子产品日益成为人们生活中的必需品。展望未来,5G商用、物联网以及人工智能等技术的大规模发展与应用,将掀起又一波的电子产品新浪潮。电源管理芯片作为集成电路的基础芯片、控制电子设备的动力源头,是电子产品所必需的。电源管理芯片通过对电池电能的调节、监测,为系统保持最佳运行状态提供能量支持。因此,其性能优劣直接对电子设备的用户体验产生明显的影响。 随着电子设备功能多样化体积小型化,对于电源管理芯片也提出了更高的要求,更高的转换效率、更宽的输出范围以及更高的转换效率是其中的重点。在电池容量不断提升的同时,提高电子设备的电源效率可以延长设备的使用时间。为了在全负载范围内都能保持高效率、低纹波,本文采用自适应导通控制方法,根据不同的负载条件选择合适的工作状态,使得开关频率在连续导通模式下相对恒定,而在非连续导通模式下,开关频率随着负载电流的减小而降低,从而保证开关电源芯片在不同的负载条件下,都能保持较高的效率。

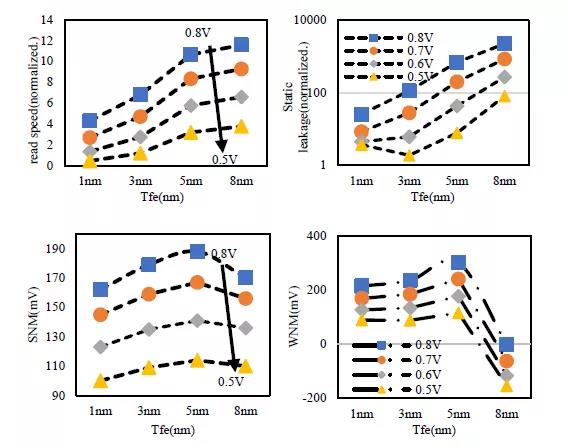

图1. 自适应导通控制电路。 在降压转换器中,相对于二极管,同步整流技术更得到市场的接纳。在同步整流技术中,采用MOS管作为同步整流管,其本身的低导通电阻特性,极大地降低了导通损耗。 西安电子科技大学微电子学院柴常春教授课题组以谷值电流模降压型DC–DC变换器为研究,介绍了降压型DC–DC的基本理论,通过对自适应导通控制电路以及零电感电流检测电路的设计,确保电路能够在CCM以及DCM之间自由切换以及实现CCM下,开关频率的恒定;通过对补偿电路的设计,确保环路的稳定,并优化电路以达到2A的带载能力;此外,对于多模式的探索,使得转换器在不同的负载条件下能够工作在最佳状态。对于开关电源的带载能力、瞬态响应、效率提高以及环路稳定性等方面的研究,具有重要的研究价值与实用价值。 A high performance adaptive on-time controlled valley-current-mode DC–DC buck converter J. Semicond. 2020, 41(6): 062402 doi: 10.1088/1674-4926/41/6/062402 6. 高速负电容FinFET SRAM位单元的变化容限 在人工智能热潮下,各种物联网技术、智能设备的应用场景日益俱增,对高速,高性能,低功耗芯片的需求也在不断增长。凭借其高速和易于使用的优势,静态随机存取存储器(SRAM)已广泛应用于片上系统(SOC)。在众多的SOC以及功能要求较高的MCU中,嵌入式SRAM在芯片面积上的占比日益增大,这导致了整个芯片的性能越来越取决于SRAM的性能。摩尔定律随着工艺节点的不断减小而走向边缘,当技术节点下降至一定的工艺节点以下,器件已无法完全按照等比例缩小的原则进行设计,相邻晶体管之间的临近效应问题也随之日益增多,从而导致超大规模集成电路的稳定性以及可靠性严重受限,工艺节点的降低,低功耗的需求,芯片集成度的提高,性能速度的提升,晶体管的设计由于以上几点准则之间的相互制衡而变得日益困难。而NC-FinFET的出现,有效的改善了目前存在的问题,它是在与FinFET相同结构的基础上在栅绝缘层覆盖铁电薄膜,可以在不改变传统晶体管中载流子传输机制的情况下实现小于60 mV/dec的SS从而达到减少漏电流,提高晶体管的on-state 电流,该特性使得NC-FinFET在SRAM上有着客观的应用前景。 对于由NC-FinFET组成的SRAM的研究甚少,对于由工艺引起的波动性研究更是稀缺,中国科学院大学钱雅倩等针对SRAM的四个特性,静态噪声容限(SNM),写余量(WM),读取速度以及漏电流四个方面,研究了在铁电厚度,Fin的数量、温度以及工艺中影响最大的沟道长度波动的情况下,以上四个参数的变化趋势。下图就是随着铁电材料的厚度的变化,各参数所受的影响。

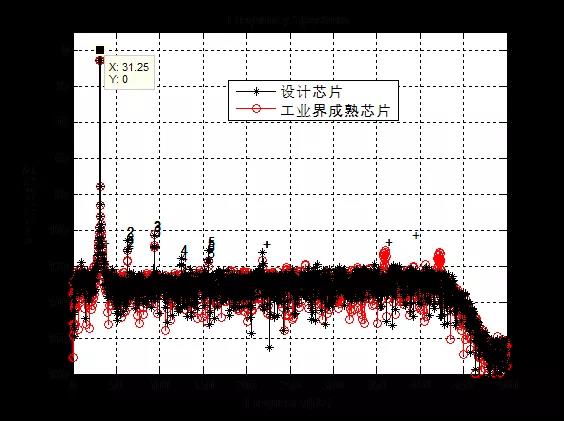

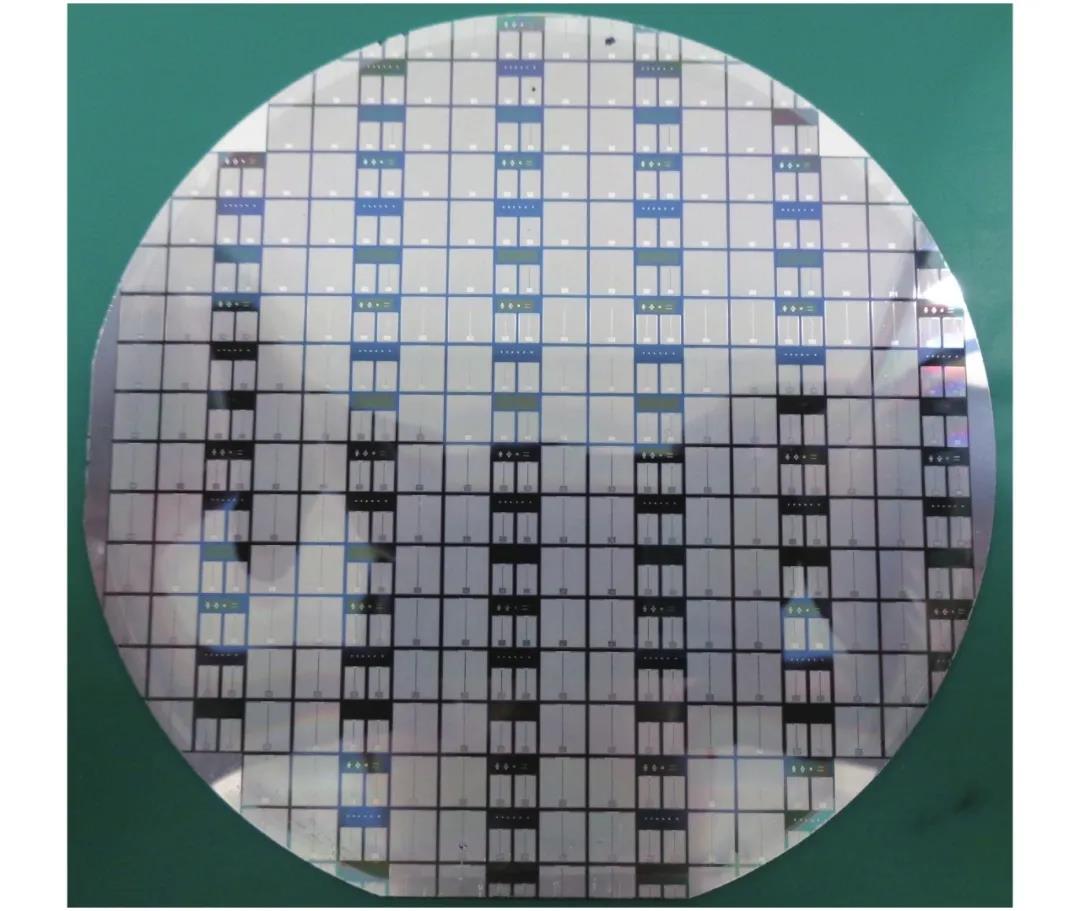

Variation tolerance for high-speed negative capacitance FinFET SRAM bit cell Yaqian Qian, Shushan Qiao, Rongqiang Yang J. Semicond. 2020, 41(6): 062403 doi: 10.1088/1674-4926/41/6/062403 7. 采用四阶单环CIFB结构的18位sigma-delta开关电容调制器 目前国际最新的sigma–delta ADC研究已经达到31-bit高精度,调制阶数采用4阶或更高的5阶结构;商业化产品基本被美国ADI,TI等公司垄断,其在结构设计和工艺制造方面有长期经验积累,代表了国际ADC,DAC设计和实现的最先进水平。对比而言,国内虽然从事sigma–delta ADC的研究有多年历史,也取得了很大的进展,但应该说还基本处于跟踪阶段,大多采用2阶或3阶调制结构,精度通常在16-bit以下,与国际先进水平存在较大的差距。作者以国家863科研项目和现有成熟的勘探仪器研究工作为背景,研究高精度高阶sigma–delta ADC,以期实现有效位高于16-bit的高阶sigma–delta ADC。 sigma–delta ADC性能进步的关键在于前端模拟调制器噪声调制性能,这一方面可以通过提高调制器的阶数达到,另一方面可以通过提高量化器的位数达到。提高调制器阶数将大大降低系统稳定性,故产生了MASH结构调制器,然而由于制造工艺的限制,MASH结构中多级之间的不匹配将造成噪声性能的降低;提高量化器位数则将同时加大调制器结构的非线性,也会大大降低噪声调制性能。故sigma–delta ADC的研究方向集中于如何设计出稳定性高的高阶调制器结构,如何在保证一定非线性的条件下增加量化器位数,以及对匹配不敏感的MASH结构调制器结构开发等方面。从目前研究来看,随着调制器阶数的增加,稳定性迅速降低,故高阶结构调制器一般只用于低动态范围的环境下,更多的是在现有的低阶结构下调整调制器的反馈结构增加噪声调制性能,其次则是对MASH结构的研究,随着集成电路工艺的发展,对于MASH结构的研究逐渐流行。 合肥高速机器视觉研究中心董宁等基于Chartered 0.35 µm CMOS工艺,成功完成一款有效位近18-bit单环4阶1位CIFB型sigma–delta模拟调制器的设计工作,芯片已成功流片,从测试结果来看,各项指标达到了设计要求。论文针对单环高阶sigma–delta调制器的设计实现进行了广泛的讨论和分析,对调制器各构成单元:运算放大器,比较器,时钟产生电路,带隙基准等设计给出了详细的电路级设计。测试结果分析表明所设计芯片达到了设计目标,其调制性能达到甚至超过了工业界成熟调制芯片。由于测试源精度的限制,目前测试所得调制器有效位为18-bit。

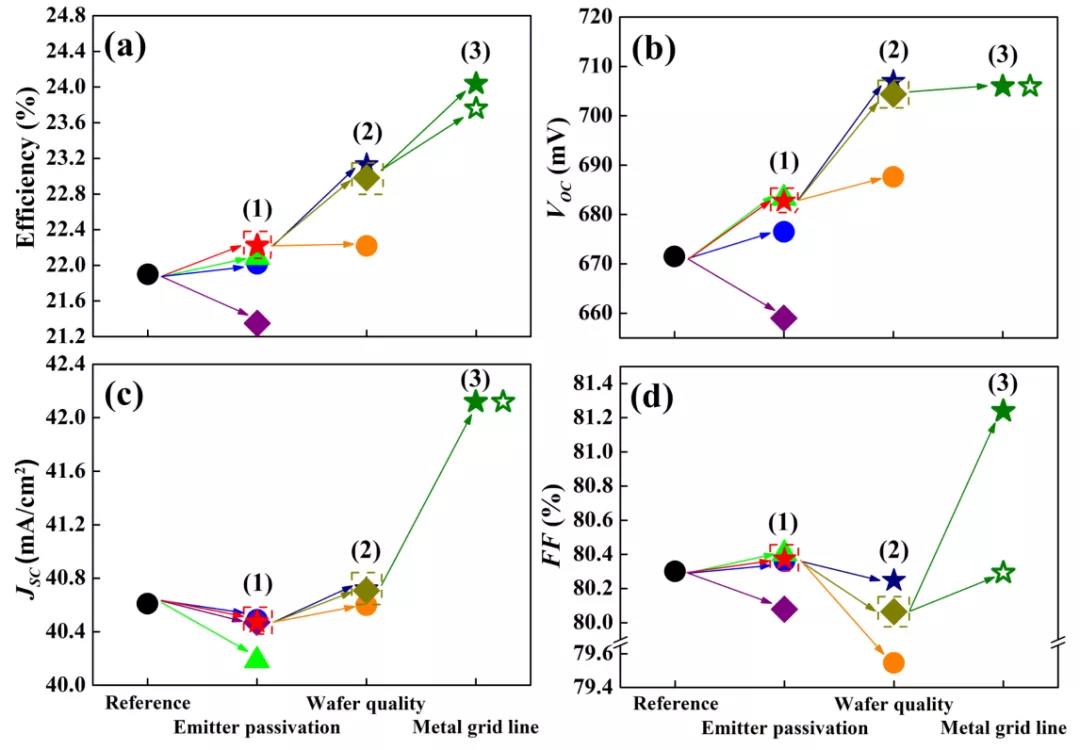

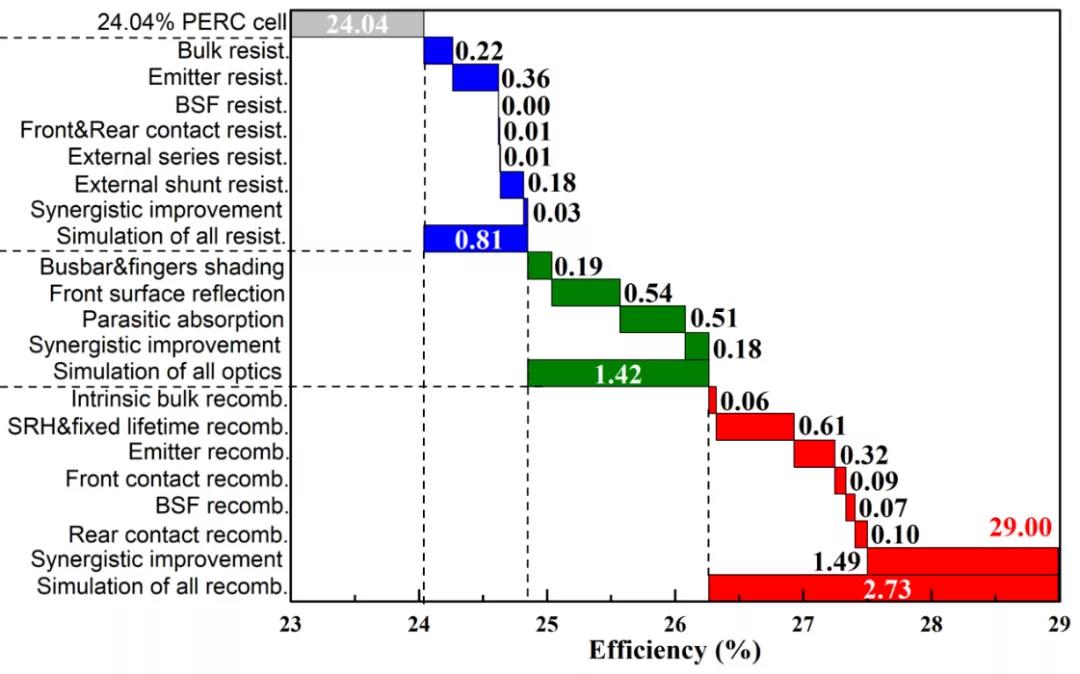

Sigma–delta ADC的研究应该是ADC领域最为活跃的一个分支,这主要归功于集成电路工艺技术的飞速发展,使得速度换精度的策略可以很好的应用,另一方面也是应无线通信,雷达应用以及数字音视频等领域的需求。sigma–delta ADC由于其高精度被广泛应用于以上各种领域中,尤其在石油,天然气资源勘探领域。 An 18-bit sigma –delta switched-capacitor modulator using 4-order single-loop CIFB architecture Guiping Cao, Ning Dong J. Semicond. 2020, 41(6): 062404 doi: 10.1088/1674-4926/41/6/062404 8. 利用准p-OTFTs对有机晶体管的数学分析  图1. 底栅底接触有机薄膜晶体管的示意图。 Mathematical analysis of organic-pass transistor using pseudo-p-OTFTs J. Semicond. 2020, 41(6): 062601 doi: 10.1088/1674-4926/41/6/062601 9. 基于效率超过24%的量产技术下带有钝化发射极和后接点配置的单晶硅太阳能电池数值研究 太阳能作为可再生能源的重要组成部分,在推动可再生能源的发展,优化能源消费结构方面扮演着重要的角色。如果能合理利用太阳能资源,可以缓解甚至解决目前全球面临的能源短缺和环境污染问题。光伏太阳电池直接将太阳能转换为电能,可以源源不断地为人类社会的生产和生活提供动力。目前已经实现产业化的太阳电池可以分为两大类,分别是晶硅太阳电池和薄膜太阳电池,其中晶硅太阳电池的市场占比达到95%。而在晶硅太阳电池中,基于p型单晶硅的钝化发射极背电池(Passivated Emitter and Rear Cell, PERC)已经成为新一代太阳电池的常规技术,并且有着很好的发展空间和发展前景。据国际光伏技术路线图 (ITRPV) 统计,2019年PERC电池的市场占有率接近40%,未来这个比重还将不断提高,到2029年将达到70%。目前PERC电池的量产效率可以达到22.3%,但为了满足日益增长的市场需求,还需进一步“提效降本”。为了进一步提高PERC电池的电性能,产业界面临着如何进一步提升表面钝化性能、如何减少光生载流子复合、如何提高光生载流子收集效率等一系列问题和挑战。 针对这些问题,中国科学院上海高等研究院李东栋研究员、鲁林峰副研究员和晋能清洁能源科技有限公司合作,从模拟仿真的角度,建立了面向产业化PERC电池的光学和电学模型,并从发射极表面钝化、硅片质量和金属化技术等三方面对未来PERC电池的技术改进路线进行了研究和分析。电池照片及其剖面结构示意图如图1所示。图2模拟总结了未来PERC电池可能的优化方向。第一步为n+发射极表面钝化层的优化,发现采用SiO2/SiNx叠层薄膜作为发射极钝化层时,PERC电池的模拟电性能最好,转换效率为22.2%,比参考PERC电池提升了0.3%,开路电压VOC为682.7 mV,短路电流JSC为40.47 mA/cm2,填充因子FF为80.37%;在此基础上,进一步对硅片特性进行优化,得到硅片电阻率和少子寿命的优化值分别为1.5 Ω·cm和2500 μs,此时电池的模拟效率为22.98%,开路电压VOC为704.4 mV,短路电流JSC为40.71 mA/cm2,填充因子FF为80.06%;最后我们对金属电极进行优化,电池正面栅线采用12BB的技术,电极制备方式为电镀Ni/Cu合金,经过模拟计算后,电池的最高效率达到24.04%,填充因子FF为81.24%,VOC为708 mV,JSC为42.17 mA/cm2。

图1. PERC太阳电池的(a)照片和(b)剖面结构示意图。

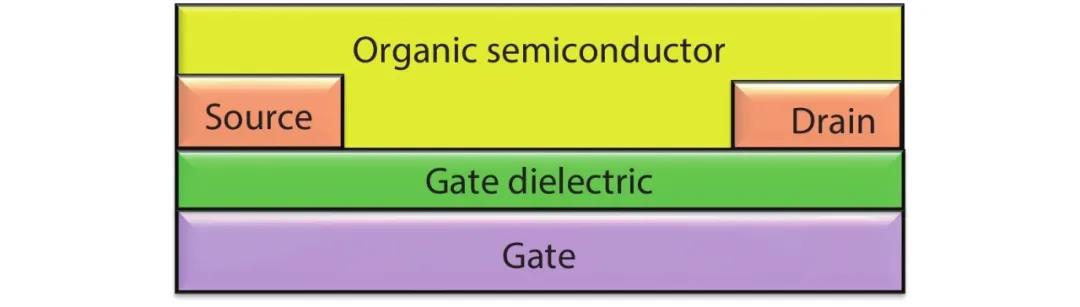

图2. 未来PERC电池可能的优化方向。  图3. 24.04%产业化PERC太阳电池的损失来源分析和29%极限效率的计算。 随着人们环保意识的增强和光伏太阳电池生产成本的不断下降,未来有望实现光伏入户,家家自给自足。作为新一代太阳电池的主流技术,PERC电池会在“提效降本”的道理上继续走下去,为实现光伏入户承担起重要的责任和作用。本论文针对产业化的PERC电池展开了系统的模拟研究,分析了未来进一步提升PERC电池性能的路径和方法,为以后产业界的工艺生产优化提供参考。 Numerical study of mono-crystalline silicon solar cells with passivated emitter and rear contact configuration for the efficiency beyond 24% based on mass production technology J. Semicond. 2020, 41(6): 062701 doi: 10.1088/1674-4926/41/6/062701 10. 低导通电阻为1.2 kV且Ron,sp为3.4 mΩ·cm^2的 4H-SiC功率MOSFET 由于碳化硅的材料物性优势,碳化硅电力电子器件的性能指标较硅电力电子器件更优,其中碳化硅MOSFET可实现低导通电阻、高速开关特性,更适合于高温、高功率的应用,产品开发更是备受关注,目前制约碳化硅MOSFET广泛应用的主要因素为器件的长期可靠性。 宽禁带半导体电力电子器件国家重点实验室长期致力于碳化硅电力电子器件的产品开发工作,目前已量产多种电压等级、电流等级的碳化硅MPS二极管,同时也在小批量生产1200V的碳化硅MOSFET产品。本文的研究不仅关注碳化硅MOSFET导通电流密度的提升,还在设计阶段注重器件内部电场强度的优化,预期获得较好的可靠性,为后续的器件设计提供了参考。开品开发完成后,碳化硅MOSFET可广泛应用于光伏、电动汽车等领域。  图6. 制造的1.2 kV/15 mΩ器件的照片。 Low on-resistance 1.2 kV 4H-SiC power MOSFET with Ron,sp of 3.4 mΩ·cm2 Qiang Liu, Qian Wang, Hao Liu, Chenxi Fei, Shiyan Li, Runhua Huang, Song Bai J. Semicond. 2020, 41(6): 062801 doi: 10.1088/1674-4926/41/6/062801 |

首 页 >> 通知公告