综述文章

1

碳化硅超级结器件制造技术综述

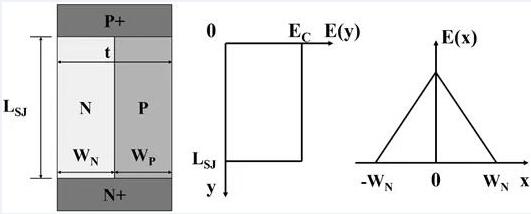

作为电力电子系统的基础,功率半导体器件决定着系统的效率、尺寸、成本等,在电能的传输与转换过程中发挥着重要的作用。为了降低系统功耗、提高能源利用效率,需要尽可能地减小器件的比导通电阻(Ron,sp)。Ron,sp主要体现在位于外延层中的器件漂移区上。同时,漂移区也用于承担器件的击穿电压(BV)。随着功率器件应用的电压等级不断提高,器件漂移区的厚度随之增加,那么器件的导通电阻也会增大。引入超级结(superjunction, SJ)结构,基于电荷补偿的基本原理,可以显著改善Ron,sp-BV关系,并且已经在硅(Si)功率器件中实现商业化应用。

图1. (a)典型的超级结结构。(b)y方向和x方向的电场分布。

碳化硅(SiC)材料的临界击穿场强约为Si的10倍。在同等击穿电压下,SiC器件需要的漂移区厚度要小于Si器件,所以SiC器件的导通电阻要小得多。另外,SiC材料还具有其它适于制备功率器件的特性,例如高热导率、高饱和漂移速度,以及能够形成二氧化硅(SiO2)作为自然氧化层等。将SJ技术引入SiC功率器件,更有利于发挥SiC材料在功率器件领域的优势。但是,由于SiC极其稳定的物理化学性质,其加工难度要远大于Si,所以SiC SJ结构的制造技术是其走向实际应用中的一个重要问题。

中国科学院半导体研究所樊中朝正高级工程师课题组对现阶段碳化硅超级结器件的制造技术及相关工艺挑战进行了综述。通过分析比较,认为沟槽刻蚀-外延回填(TFE)技术更适用于未来SiC SJ器件的工业化批量生产。另外,现阶段多以n型SiC外延层为基础,在其上开展p型离子注入或外延填槽工艺的研究。文中对基于p型SiC外延层的SiC SJ器件制造技术进行了展望,为后续的研究工作提供了一个发展方向。

A review of manufacturing technologies for silicon carbide superjunction devices

Run Tian, Chao Ma, Jingmin Wu, Zhiyu Guo, Xiang Yang, Zhongchao Fan

J. Semicond. 2021, 42(6): 061801

doi: 10.1088/1674-4926/42/6/061801

研究论文

1

量子图像传感器

图像信息占人类感知信息总量的80%以上,图像传感器芯片是整个成像系统的核心。“理想的图像传感器”应该具有无限大的分辨率、动态范围和无限高的帧频,以及尽可能小的功耗。图像传感器发展面临的技术挑战包括:像素和读出电路噪声;小尺寸像素的动态范围受到像素阱容量减少、光子衍射及像素间串扰噪声限制;分辨率提升带来的庞大数据量限制了帧频的提升等。

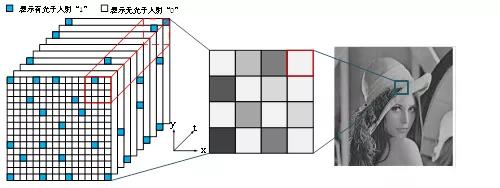

2011年,CMOS有源像素传感器的发明人、美国达特茅斯理工大学的Eric R. Fossum教授提出了量子图像传感器(Quanta Image Sensor,QIS)的概念。QIS基于单光子计数机制,采用空间过采样和时间过采样技术,可大幅提升空间分辨率、时间分辨率(帧频)和动态范围特性。QIS的提出和研究已有十年时间,其理论、像素及读出电路、图像重建算法已经有系列进展。但总体来说,QIS的发展仍然面临系列挑战,如完善的理论模型、更低噪声的像素和读出电路等。

QIS由大量的亚衍射极限像素组成,该像素被称为“jot”(希腊语中意为最小的东西),jot的输出“0”表示没有光子入射,“1”表示有光子入射。jot尺寸可突破光学镜头的衍射极限,像素阵列以高速率被扫描,帧频远大于物体的运动速率(保证每个像素帧内的平均入射光子数量少),通过对一定数目像素的多帧输出量化值进行处理,可以得到输出图像,如图1所示。

图1. 量子图像传感器示意图。

天津大学微电子学院徐江涛教授课题组以有源像素为核心,开展了QIS理论建模、特性分析和工程仿真研究。主要研究工作为:

(1)提出了一种量子图像传感器信号链模型。该模型包括光子到电子、电子到电压以及电压到数字码的完整信号转换过程,并基于概率统计学完成数学模型的推导和建立,进而得出了入射光子、光生电子和输出数字码等变量对应的信号值和噪声值的计算公式。

(2)基于上述QIS模型,推导并绘制了理想QIS和实际QIS的光响应函数及光响应曲线。进一步讨论了理想QIS的光响应特性曲线的主要特点,以及量子效率、暗电流、读出噪声对实际 QIS 光响应特性的影响。

(3)分析了理想QIS和实际QIS的光子和光生电子计数信号误差率的计算公式。分析并讨论了量子效率、暗电流、读出噪声对实际QIS的计数精度的影响,提出了扩展高精度计数曝光区间的方法。

(4)提出了一种保证QIS在有效曝光区间内的积分时间优化方法。分析了不同照度下光斑面积、光强、曝光时间之间的关系,该结果可用于指导QIS设计。

量子图像传感器的研究目前还处于起步阶段,主要研究热点包括:QIS信号传输模型及三维堆叠系统架构,极低噪声像素器件、可去除冗余数据的读出电路、高效低噪声的图像重建算法等。随着这些技术的突破,未来QIS可以在高分辨率成像、高速摄像、大动态范围成像、微光成像等领域体现优异特性,满足监控、科研、医疗、太空、增强现实、虚拟现实、三维成像等系列应用的需求。

Modeling the photon counting and photoelectron counting characteristics of quanta image sensors

Bowen Liu, Jiangtao Xu

J. Semicond. 2021, 42(6): 062301

doi: 10.1088/1674-4926/42/6/062301

2

重掺Si:一种潜在的传统等离子金属的替代品

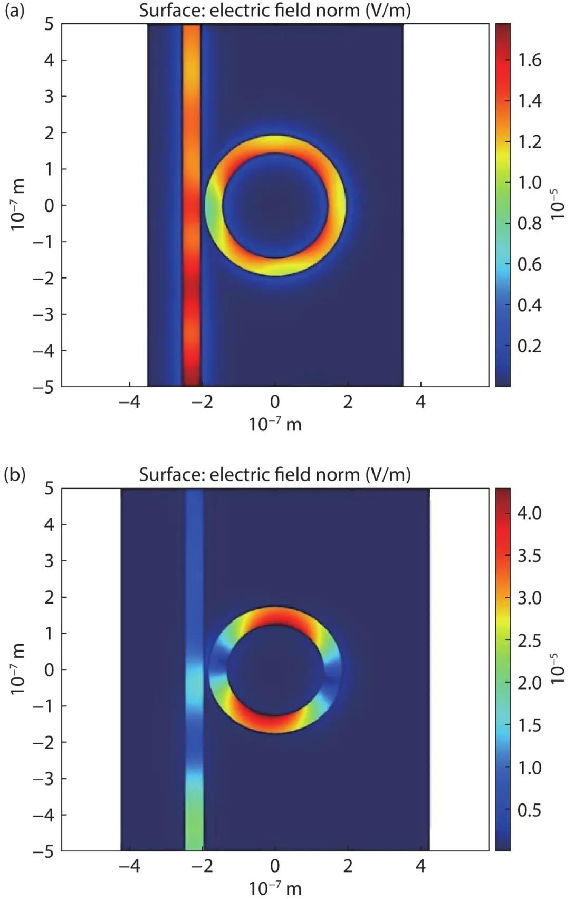

本文研究了P型重掺Si的等离子特性。尽管大多数等离子器件都是利用金属-绝缘体-金属(MIM)波导来支持表面等离激元(SPPs)的传播,但是金属材料的使用却面临诸如损耗控制、极化响应、纳米制程等方面的难题。与金属材料相比,P型重掺Si不仅显示出与金属相似的等离子特性,而且能够克服金属材料所面临的诸多难题。我们建立了重掺Si的数学模型,并在此基础上进行数值模拟,将理论上得到的相对介电常数值与实验值进行了对比。在理论模型中,我们用P型Si与空气的界面代替金属与空气的界面形成波导。观察到了与MIM波导中类似的SPPs的形成和传播。

图1. 波导模式传播图。

Heavily doped silicon: A potential replacement of conventional plasmonic metals

Md. Omar Faruque, Rabiul Al Mahmud, Rakibul Hasan Sagor

J. Semicond. 2021, 42(6): 062302

doi: 10.1088/1674-4926/42/6/062302

3

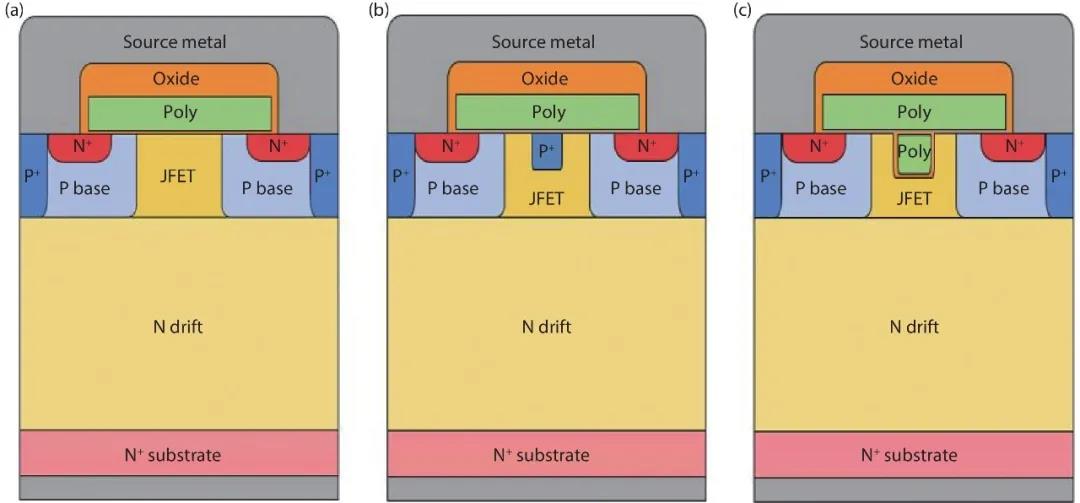

通过源接触虚设栅极来实现高频3.3 KV 4H-SiC DMOSFET

本文提出了一种具有源接触虚设栅极的4H-SiC DMOSFET器件结构(DG-MOSFET),并通过Sentaurus TCAD及PSIM模拟对该器件结构进行了分析。与PN结相比,源接触MOS结构的耗尽区更少。因此,当导通电阻(RON)的退化受到限制时,栅极和漏极之间的交叠区域将会大幅度减小。与传统的DMOSFET(C-MOSFET)器件及中心植入MOSFET(CI-MOSFET)器件相比,DG-MOSFET的高频品质因数(HF-FOM)分别提高了59.2% 和 22.2%。在双脉冲测试中,DG-MOSFET可节省的总功率损耗分别为53.4% 和5.51%。此外,在电源电路模拟中,开关电源损耗在降压式转换器中可以降低61.9% 和 12.7%,在升压式转换器中可以降低61% 和9.6%。

3.3 kV 4H-SiC DMOSFET with a source-contacted dummy gate for high-frequency applications

Kyuhyun Cha, Kwangsoo Kim

J. Semicond. 2021, 42(6): 062801

doi: 10.1088/1674-4926/42/6/062801

4

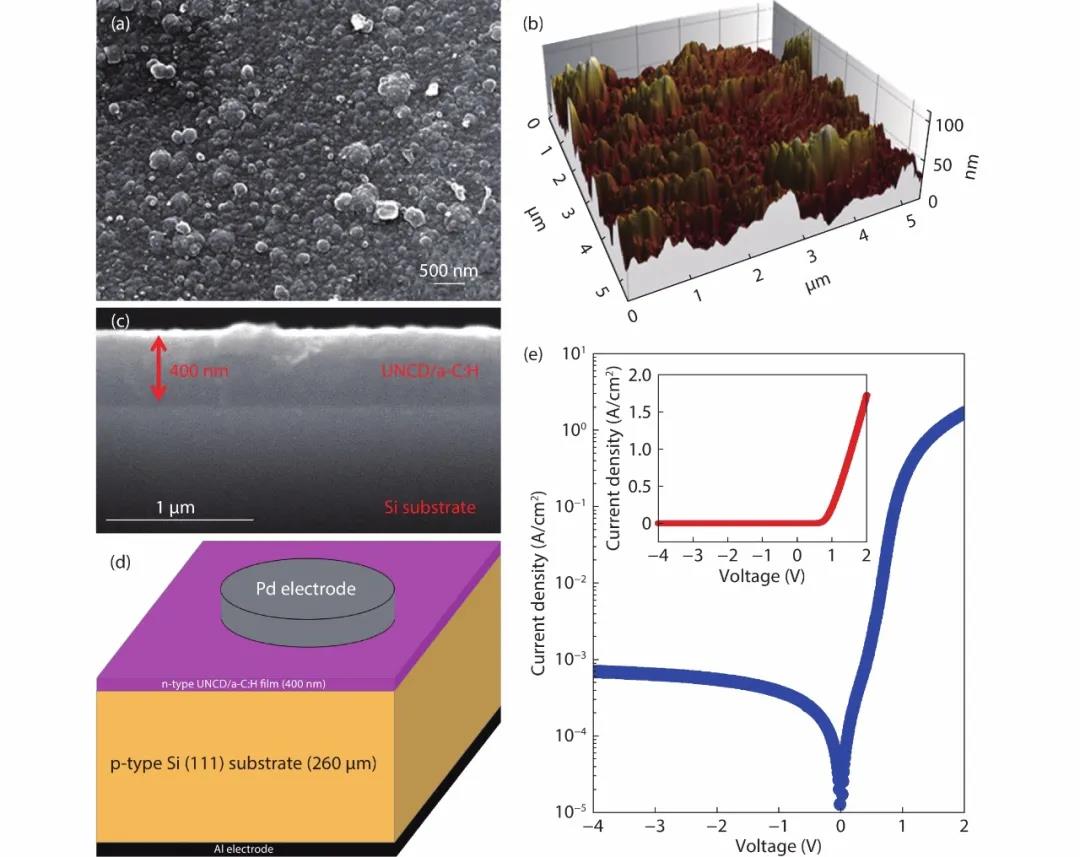

氮掺杂超纳米金刚石/氢化非晶碳复合材料薄膜中陷阱态密度分布的确定

本文从实验上研究了氮掺杂超纳米金刚石/氢化非晶碳(UNCD/a-C:H)复合材料薄膜。该薄膜是通过同轴电弧等离子沉积方法在Si衬底上生长的。通过温度依赖的电容-频率测量来表征薄膜特性,其中温度和频率的变化范围分别为300–400 K和50 kHz–2 MHz。薄膜中陷阱态密度的能量分布可以通过测得的电容-频率特性这一简单的技术手段提取出来。在测试温度区间内,陷阱随能量呈高斯分布,峰值处于2.84 × 1016–2.73 × 1017 eV–1 cm–3范围内,中心位于导带以下120–233 meV处。这些态的产生是由于大量sp2轨道杂化的C键及π键态被局域在UNCD/a-C:H薄膜的晶界(Grain-boundaries,GBs)中。实验所得到的缺陷参数有利于对UNCD/a-C:H复合材料电学基本特性的理解,并且可用于抑制UNCD基材料的缺陷。

Mahmoud Shaban

J. Semicond. 2021, 42(6): 062802

doi: 10.1088/1674-4926/42/6/062802

5

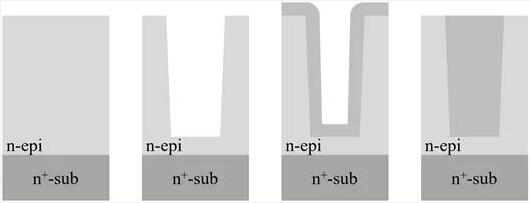

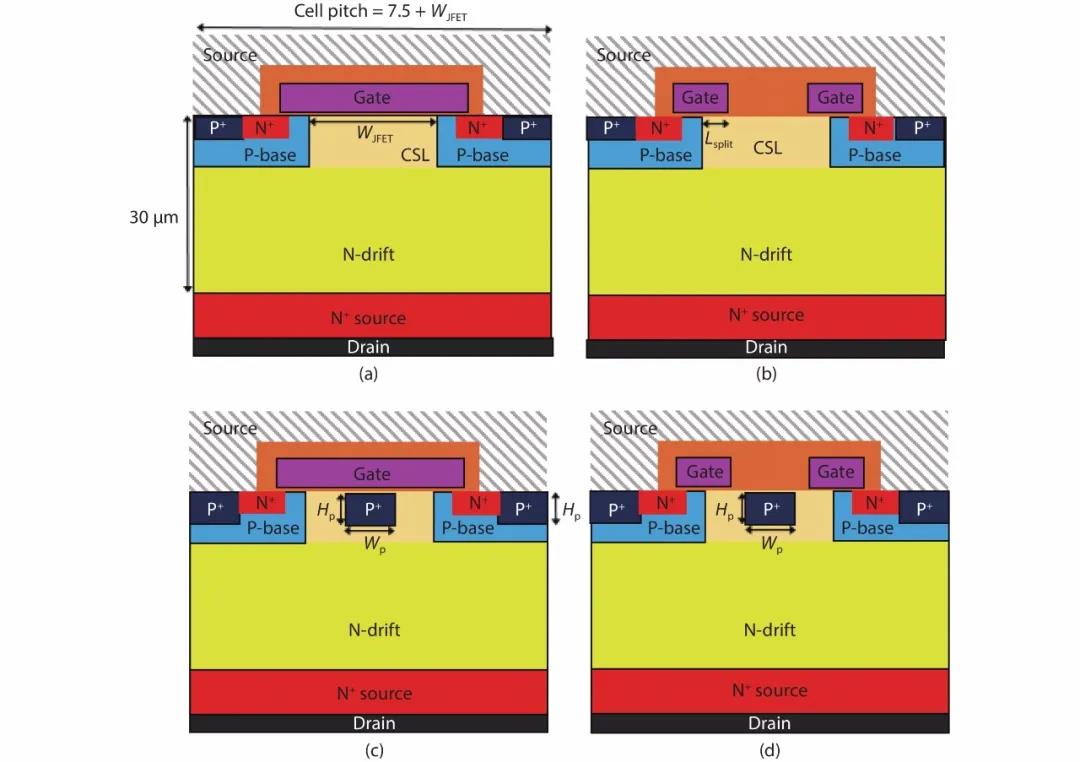

一种通过中心植入区域实现静态与开关性能更好平衡的3.3 KV 4H-SiC 分裂栅极MOSFET

分裂栅极MOSFET(SG-MOSFET)由于可以降低反向跨路电容(CRSS)而被广泛认知。但是由于栅极氧化电场较高,导致SG-MOSFET无法在3.3 kV等级稳定可靠工作。除了静态性能较低,高栅极氧化电场还使得SG-MOSFET存在诸如源漏之间穿通以及漏电极导致的势垒降低(DIBL)等问题。我们提出了一种具有接地中心植入区域(SG-CIMOSFET)的3.3 kV 4H-SiC SG-CIMOSFET,不仅可以解决以上问题,并且可以平衡优化静态性能与开关性能。通过中心植入区的引入,大幅降低了SG-CIMOSFET的导通电阻(RON),且使栅极氧化电场(EOX)最大化。由于部分屏蔽了栅极到漏极之间的电容耦合,接地中心植入区域大幅降低了CRSS以及栅极漏极电荷(QGD)。与平面MOSFET相比,SG-MOSFET、中心植入MOSFET (CIMOSFET)和SG-CIMOSFET分别将RON×QGD提高了83.7%、72.4% 和 44.5%。结果表明该器件不仅具有最小的开关能量损耗,而且具有最快的开关时间。

图1. MOSFET的横断面视图。(a) 平面MOSFET。(b) SG-MOSFET。(c) CIMOSFET。(d) SG-CIMOSFET。

Jongwoon Yoon, Kwangsoo Kim

J. Semicond. 2021, 42(6): 062803

doi: 10.1088/1674-4926/42/6/062803

6

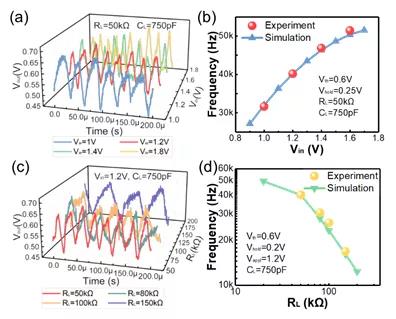

基于高一致性阈值开关器件的高性能神经形态计算振荡神经元

近年来,基于阻变存储器(RRAM)等神经形态器件的类脑计算成为研究热点,有望突破传统计算架构的“冯•诺依曼”瓶颈,而低功耗、高一致性的神经元器件实现高性能类脑计算的关键要素之一。相较于传统CMOS电路构建的“积分-发放”神经元(integrate-and-fire neuron),基于阈值开关器件的振荡神经元以其体积小、电路结构简单等优势引起了人们的广泛关注,而构建振荡神经元的一个关键挑战在于如何减小器件的随机性。

清华大学钱鹤教授、吴华强教授课题组一直致力于新型存储器与类脑计算的研究,该团队在最新出版的《半导体学报》2021年第6期上发表了题为“Oscillation neuron based on low-variability threshold switching device for high-performance neuromorphic computing”的研究论文。该论文报道了一种基于可控Ag纳米点(Ag NDs)结构阈值开关器件的振荡神经元。此振荡神经元在低电压(~1 V)下即可表现出自振荡行为,且振荡频率随外加电压脉冲幅度的增大而增大,随RRAM人工突触的电阻增大而减小,振荡频率的变化规律与模型拟合较好,可准确地反映RRAM阵列突触权重。进一步,团队将该神经元应用于大规模神经网络,结果表明,得益于阈值开关器件的大开关比(>108),此神经元在规模较大的RRAM神经网络(>128×128)中仍可正常工作;此外,阈值开关器件的高一致性改善了振荡神经元输出频率的分布,可将神经网络识别精度的损失抑制在1%以下。本文所研制的基于Ag NDs器件的振荡神经元在未来的神经形态计算应用中显示出巨大的潜力。

Yujia Li, Jianshi Tang, Bin Gao, Xinyi Li, Yue Xi, Wanrong Zhang, He Qian, Huaqiang Wu

J. Semicond. 2021, 42(6): 064101

专题推荐

半导体学报2021年42卷1期——后摩尔:新型存储与神经形态计算的阻变器件专刊

半导体学报2020年41卷11期——模拟和数模混合集成电路专刊

半导体学报2020年41卷9期——能量存储的挑战和可能性专刊

半导体学报2020年41卷8期——单元素二维半导体材料及应用专刊

半导体学报2020年41卷5期——钙钛矿半导体光电材料与器件专刊

半导体学报2020年41卷2期——面向高能效人工智能计算的可重构芯片技术专刊

半导体学报2020年41卷1期——王占国院士从事科研工作60周年专刊

半导体学报2019年40卷12期——深紫外发光材料与器件专题

半导体学报2019年40卷11期——机器人技术和健康监测用柔性可穿戴传感器专刊

半导体学报2019年40卷10期——硅基化合物材料与器件专题

半导体学报2019年40卷8期——磁性半导体的机遇与挑战专刊

半导体学报2019年40卷6期——二维材料物理性质与光电器件专刊

半导体学报2019年40卷1期——超宽禁带半导体氧化镓材料与器件专刊

半导体学报2017年38卷10期——面向可穿戴物联网与物联网系统的器件和电路专题